Кодер позиционного линейного сигнала

Иллюстрации

Показать всеРеферат

Кодер позиционного линейного сигнала относится к технике проводной связи и может использоваться в линейных трактах волокрнно-оптических систем передачи цифровой информации. Цель изобретения - повышение помехоустойчивости и расширение области применения кодера за счет возможности передачи в сигнале дополнительной информации. Кодер содержит регистр сдвига, делитель тактовой частоты, умножитель тактовой частоты, селектор комбинации двоичных сигналов, последовательнопараллельный преобразователь, D- триггер, дешифратор, элементы ИЛИ 10-13, элемент задержки, коммутатор, параллельно-последовательный преобразователь , информационный вход, тактовый вход, управляющий вход кодера . 3 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 М 7/00

APCTBEHHOE ПАТЕНТНОЕ

СТВО СССР

ТЕНТ СССР) ГОС Д

Вед M

СГОС А

1 . с, ."„ .,ю1 М,- .; г ъ.1, 1 У .У

К-А (21) (22) (46) (71) ."Да . (72) (56)

Com (54)

ГО (57) отно жет лок дим вли тем усто нени в сиг онно

1; вр рабо лине соот пре ный вый часто лект посл вател мент

ТОРСКОМУ СВИДЕТЕЛЬСТВУ

778363/24

8.01.90

0.08.93. Бюл. N 32 аучно-производственное объединение ьняя связь" .И,Галчихин и В.В.Дундуков ,Le Hiepand etw, Journal of 0ptical

unications, ч. 6, June, М 2, 1985. вторское свидетельство СССР

03972, кл. Н 04 В 7/00, 1987.

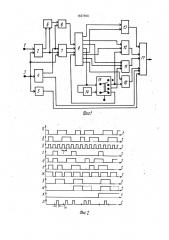

ОДЕР ПОЗИЦИОННОГО ЛИНЕЙНОГНАЛА одер позиционного линейного сигнала ится к технике проводной связи и моспользоваться в линейных трактах вонно-оптических систем передачи зобретение относится,к области провосвязи и предназначено к использованию йн ых трактах волоконно-оптических сисредачи (ВОСП) цифровой информации. ель изобретения — повышение помехочивости и расширение области примекодера за счет возможности передачи але дополнительной информации. ункциональная схема кодера позицио линейного сигнала г;риведена на фиг. менные диаграммы, поясняющие его у, — на фиг, 2; энергетические спектры ных ПНР-и ПЗИ-сигналов, полученных тственно в устройстве-прототипе и в оженном кодере; на фиг. 3. а фиг. 1 обозначены: информационход 1 кодера, регистр сдвига 2, тактоход 3 кодера, делитель 4 тактовой

ы, умножитель 5 тактовой частоты, се6 комбинации двоичных символов, довательно-параллельный преобраэо7, О-триггер 8, дешифратор-9, элеИЛИ 10-13, элемент задержки 14, Ы,, 1837400 А1 цифровой информации. Цель изобретения — повышение помехоустойчивости и расширение области применения кодера за счет возможности передачи в сигнале дополнительной информации.

Кодер содержит регистр сдвига. делитель тактовой частоты, умножитель тактовой частоты, селектор комбинации двоичных сигналов, последовательнопараллельный преобразователь, 0триггер, дешифратор, элементы ИЛИ

10-13, элемент задержки, коммутатор, параллельно-последовательный преобразователь, информационный вход, тактовый вход, управляющий вход кодера. 3 ил., 1 табл.! коммутатор 15, управляющий вход 16 коде- ра, параллельно-последовательный преобразователь 17; на фиг.2-t — текущее время, Т вЂ” тактовый интервал, Тп — позиционный интервал; на фиг.З-S(f) — тактовая частота, .::

; 1

fy — энергетический спектр.

Кодер позиционного линейного сигнала

"работает следующим образом.

Исходный двоичный сигнал с информационного входа 1 (фиг. 1) подается на регистр сдвига 2, в котором сигнал фазируется (фиг. 2,а) и сдвигается (фиг. 2,б) напряжением тактовой частоты (фиг. 2,в), поступающим с тактового входа 3. Напряжение тактовой частоты с входа З,кроме того, подается на входы делителя 4 и умножителя 5 тактовой

„частоты, а также на вход записи последовательно-параллельного преобразователя 7.

Сигналы с входов регйстра сдвига 2 подаются на входы обнаружителя комбинации двоичных символов 6, формирующего йа его выходе импульсы (фиг. 2,г) при появлении в двоичном сигнале двух пробелов

1837400 подряд, а также на вход последовательнопараллельного преобразователя 7, в котором двоичная последовательность (фиг; 2,б) задерживается дважды тактовый интервал (фиг. 2д,е), а затем считывается параллельно с входов преобразователя 7 напряжением полутактовой частоты (фиг. 2,ж), поступающим с выхода делителя 4. Этим же.напряжейием импульсы с выхода обнаружителя 6 записываются в D-триггер 8, образуя на его выходе импульсы длительностью в два тактовых интервала (фиг. 2,з), Двоичные комбинации символов с вы.ходов преобразователя 7 дешифрируются в дешифраторе 9 в зависимости от уровня сиг;, нала на выходе 0-триггера 8 по правилу, приведенному в таблице, Как видно из таблицы, в результате дешифрирования какой-то двоичной комбинации симовлов появляется импульс на 1-4 выходе дешифратора 9 при нулевом состоянии выхода D-триггера 8 или на 5 — 8 выходе дешифратора 9 — при единичном состоянии на выходе D-триггера 8.

Выходы дешифратора 9, за исключением 5-ra выхода, соединяются с входами элементов ИЛИ 10-13, выходы которых подключены к входам соответствующих разрядов параллельно-последовательного и реобразователя 17, Импульсы с 5-го выхода дешифратора 9 (фиг. 2,и), возникающие при считывании. с выходов преобразователя 7 комбинации вида 11 .и при единичном состоянии выхода

D-триггера 8 (фиг, 2,з), подаются непосредственно и через элемент задержки 14 на входы коммутатора 15, управляющий вход которога соединен с управляющим входом

16, На фиг, 1 коммутатор 15 условно обозначен в виде сдвоенного переключателя, имеющего два положения.

В исходном положении коммутатора 15 (например, при отсутствии коммутирующего напряжения на его управляющем входе) незадержанные импульсы с 5-го выхода дешифратора 9 подаются через первую цепь коммутатора на входы элементов ИЛИ 10 и

12, обеспечивающих объединение 5-го выхода дешифратора 9 соответственно с 1-м и

З-м, 7-м выходами дешифратора 9.

При этом задержанные импульсы с выхода элемента задержки 14(показаны пунктиром на фиг. 2,и) через вторую цепь коммутатора 15 подаются на запрещающий вход дешифратора 9, обеспечивая в следующий момент считывания комбинации 00 отсутствие сигнала на

4-м или 8-м выходах дешифратора 9.

Следовательно,. в исходном положении коммутатора 15 появление импульса на 5-м выходе дешифратора 9, т,е. дешифрирова50

Формула изобретения

Кодер позиционного линейного сигнала, содержащий делитель тактовой частоты, вход которого обьединен с входом умнажителя тактовой частоты и является тактовым входом кодера, выход умножителя тактовой частоты соединен с входом считывания паралелльно-последовательного преобразователя, выход которого является выходом кодера. и D-триггер. отличающийся тем, что, с целью повышения помехоустой. ние двоичной комбинации вида 11 и следующей эа ней комбинации 00, обеспечивает на входах параллельно-последовательного преобразователя 17 формирование в парал5 лельном коде кодовых групп вида 0101 и

0000 вместо дешифрированных кодовых групп 0001 и (000.

8 другом положении коммутатора 15 (например, при наличии коммутирующего

10 напряжения на его управляющем входе) незадержанный импульс с 5-ro выхода дешифратора 9 иэ-за размыкания первой цепи коммутатора 15 создает на входах параллельно-последовательного преобразовате15 ля 17 кодовую группу вида ОООО вместо 0001, а задержанный импульс с выхода элемента задержки 14 через вторую цепь коммутатора и элемент ИЛИ 12 в следующий момент считывания и дешифрирования комбинации

20 00 — кодовую rpynr ó вида 1010 вместо 1000.

На уп ра вля ющий вход коммутатора 15 подается дополнительный (служебный) сигнал (фиг. 2,к) с управляющего входа кодера 16.

С помощью импульсов полутактовой частоты (фиг. 2,ж), подаваемых с делителя тактовой частоты 4 на синхронизирующий вход записи параллельно-последовательного преобразователя 17, сигналы (кодовые группы) с выходов элементов ИЛИ 10, 11, 12; 13 записываются в параллельном коде в соот ветствующие разряды преобразователя 17, а затем считываются с выхода преобразователя 17 в последовательном коде (фиг. 2,л) напряжением двойной тактовой частоты, 35 подаваемым с умножителя тактовой частоты

5 на синхронизирующий вход считывания преобразователя 17.

Таким. образом, в предложенном кодере позиционного линейного сигнала осуществ40 ляется преобразование исходного двоичного сигнала в сбалансированный двухуровневый ПЗИ сигнал, при формировании которого с помощью замены кодовых групп и коммутации заменяющих комбинаций создаются защитный интервал и избыточность, позволяющие повысить помехозащищенность ПЗИ сигнала и обеспечить воэможность передачи в нем дополнительной цифровой информации.

1837400 ционными входами дешифратора, выход де- ..лителя тактовой частоты соединен с входом записи параллельно-последовательного преобразователя, с входом считывания по5 сгедовательно-параллельного преобразователя и с синхровходом D-триггера, первый-четвертый выходы дешифратора соединены с первыми входами сооюетственно первого-четвертого элементов ИЛИ, 10 пятый вход дешифратора соединен непосредственно и через элемент задержки соответственно с первым и вторым информационными входами коммутатора, уяравляющий вход которого является

15 управляющим входом кодера, шестойвосьмой выходы дешифратора соединены с вторыми входами соответственно второго-четвертого элементов ИЛ И, первый выход коммутатора соединен с

20 третьйм входом второго элемента ИЛИ, второй выход коммутатора соединен с вторым входом первого и третьим входом третЬего элементов ИЛИ, третий выход коммутатора соединен с запрещающим

25 . входом дешифратора. Уровень сигнала на выходах дешифратора 9

У овень с гнала

Уровень "0" на выходе 0-триггера 8 н выход х преВых. 3 Вых. 4

Вых. 7 Вых.8 о

Вых. 6.

Вых. 5

Вых. 2

ВьФ. 1 разоеля 7

1

0

1

0

1

0

0

0 0

01

10 11

1 чив сти и расширения области применения за чет передачи в сигнале дополнительной ин рмации, в кодер введены регистр сдвига, електор комбинации двоичных символов. де ифратор, последовательно-параллельны преобразователь, коммутатор, элемент зад ржки и элемент ИЛИ, выходы которых сое инены с соответствующими информацион ыми входами параллельно-последовател ного преобразователя, информационный

sxo регистра сдвига является информационны входом кодера, синхрониэирующий вход

per стра сдвига и вход записи последовател но-параллельного преобразователя подкл ены к тактовому входу кодера, первый вы д регистра сдвига соединен с первым входо селектора комбинации двоичных символо, выход которого соединен с ин ормационным входом 0-триггера, второй вы од регистра сдвига соединен с вторым

sxo ом селектора комбинации двоичных си волов и с информационным входом посл овательно-параллельного преобразоват ля, выходы которого и выход 0-триггера сов инены с соответствующими информаУровень "1" на выходе 0-триггера 8

1837400

Ж

У

18374ОО

С9

Фа и

Я1 г

Составитель Н.Бочарова

Техред М.Моргентал Корректор О.Гарелли

Тираж Подписное твенного комитета по изобретениям и открытиям при ГКНТ СССР

113035 Москва Ж-35 Ра шская наб. 4 5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101