Стереодекодер

Иллюстрации

Показать всеРеферат

Использование: в.радиотехнике и телевидении , в качестве стере оде кодера звука в ЧМ радиовещательных и телевизионных приемниках. Сущность изобретения: стереодёкодер содержит суммарно-разностный преобразователь, четырехквадрантный перемножитель , корректирующий фильтр, вход стереодекодера, блок восстановления поднесущей частоты, квадратор, блок фазовой автоподстрой.ки частоты, фазовый детектор , фильтр нижних частот, генератор, первый делитель частоты ма два, коммутатор , выход опорного напряжения поднесущей частоты, блок сравнения фаз, первый электронный ключ, второй электронный ключ, третий делитель частоты на два, второй делитель частоты на два, первый переключатель , третий электронный ключ, второй переключатель, дополнительную частотно-задающую цепь, третий переключатель , вход источника питания, фильтр верхних частот. Стереодекодер обеспечивает прием сигналов радиовещания в системах с полярной модуляцией в системе с пилот-тоном. 1 з.п. ф-лы, 3 ил,

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 04 Н 5/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ . К ПАТЕНТУ с

ы с. с (21) 4911700/09 (22) 04.12.90 (46) 30.08,93. Бюл. ¹ 32 (71) Научно-исследовательский институт

"Дельта" (72) B.В.Милехин и П,П.Полятыкин (73) П,П.Полятыкин (561 Авторское свидетельство СССР

¹1272513, кл, Н 04 Н 5/00, 1981. (54) СТЕРЕОДЕКОДЕР (57) Использование: в радиотехнике и телевидении, в качестве стереодекодера звука в

ЧМ радиовещательных и телевизионных приемниках. Сущность изобретения; стереодекодер содержит суммарно-разностный преобразователь, четырехквадрантный перемножитель, корректирующий фильтр, 1

Ф

Изобретение относится к радиотехнике и телевидению и может быть использовано в качестве стереодекодера звука в ЧМ радиовещательных и телевизионных приемниках.

Цель изобретения — прием сигналов радиовещания с частотной модуляцией в системах с полярной модуляцией с ослаблением и без ослабления.разностного сигнала в области поднесущей частоты и в системе с пилот-тоном, а также повышение устойчивости синхронизации при работе в системах с полярной модуляцией.

Введенные в блок восстановления поднесущей частоты три электронных ключа, первый и второй переключатели, второй и третий делители частоты и дополнительная чвстотозадающая цепь реализуют две схемы восстановления поднесущей частоты на

„„5U„„1838883 АЗ вход стереодекодера, блок восстановления поднесущей частоты, квадратор, блок фазовой автоподстройки частоты, фазовый детектор, фильтр нижних частот, генератор, первый делитель частоты иа два, коммутатор, выход опорного напряжения поднесущей частоты, блок сравнения фаз, первый электронный ключ, второй электронный ключ, третий делитель частоты на два, второй делитель частоты на два, первый переключатель, третий электронный ключ, второй переключатель, дополнительную частотно-задающую цепь, третий переключатель, вход источника питания, фильтр верхних частот. Стереодекодер обеспечивает прием сигналов радиовещания в системах с полярной модуляцией в системе с пилот-тоном. 1 з,п. ф-лы, 3 ил, выходе блока: 31, 25 кГц в системах с полярной модуляцией и 38 кГц в системе с пилоттоном. Переключение частот настройки генератора блока ФАПЧ осуществляется введением дополнительной частотозадающей цепи.

Закорачивание третьим переключателем емкости короектирующего фильтра обеспечивает необходимый баланс амплитуд и фаз суммарного и разностного сигналов на выходах стереодекодера в режимах приема стереосигналов в системе с пилоттоном и в системе с полярной модуляцией, . осуществляемой без ослабления спектра разностного сигнала в области поднесущей частоты.

Таким образом, стереодекодер обеспечивает прием сигналов радиовещания с ча1838883 статной модуляцией в системах с полярной модуляцией с ослаблением и без ослабления разностного сигнала в области поднесущей частоты, а также в системе с пилот-тоном. В стереодекодер в блок восстановления поднесущей частоты введен фильтр верхних частот, причем первый вход блока сравнения фаз соединен с входом квадратора через фильтр верхних частог.

Введение фильтра верхних частот ослабляет мешающий суммарный сигнал на входе квадратора, устраняя тем самым эффект ослабления поднесущей частоты суммарным сигналом, а также el0 ограниччение в квадраторе.

Таким образом фильтр верхних частот обеспечивает повышение утойчивости синхронизации при работе в системах с полярной модуляцией.

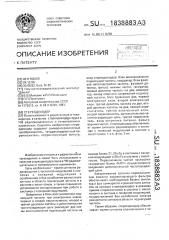

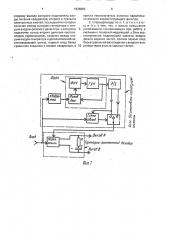

На фиг, 1 приведена структурная схема известного устройства; на фиг, 2 — спектры сигналов в системах стереофонического вещания: а) система с полярной модуляцией (спектр разностного сигнала ослаблен в области поднесущей частоты); б) система с пилот-тоном; в) система с полярной модуляцией без ослабления спектра разностного сигнала в области поднесущей частоты; на фиг, 3— структурная схема стереодекодера.

Стереодекодер содер>кит суммарноразностный преобразователь 1, состоящий из четырехквадраптного перемножителя 2, выходы которого являются выходами стереодекодера, между которыми включен корректирующий фильтр 3. При этом первый вход суммарно-разностного преобразователя является входом стереодекодера 4, который соединен с входом блока восстановления поднесущей частоты 5.

Блок восстановления поднесущей частоты 5 содержит последовательно соединенные квадратор 6 и блок фазовой автоподстройки частоты 7. Блок ФАПЧ 7 состоит из последовательно включенных фазового детектора 8, фильтра нижних частот 9 и генератора 10.

Выход генератора 10, являющийся выходом блока ФЛПЧ 7,через первый делитель частоты на два 11 подключен ко входам коммутатора 12, Выход коммутатора 12 является . выходом блока восстановления поднесущей частоты 13 и подключен ко второму входу суммарно-разностного преобразователя.

Кроме того, блок восстановления поднесущей частоты содержит блок сравнения фаз

14,выход которого подключен к управляющему входу коммутатора, а первый вход является входом блока восстановления поднесущей частоты. Первый электронный ключ 15 включен между первым входом блока сравнения фаз 14 и первым входом фазового детектора 8. Второй электронный ключ

16 включен "между вторым выходом первого делителя частоты 11 и вторым входом блока сравнения фаз 14, к которому подключены последовательно соединенные третий 17 и второй 18 делители частоты. Вход второго делителя частоты 18 соединен со вторым выходом первого делителя частоты 11. Второй вход третьего делителя частоты 17 подключен к первому выходу первого делителя частоты 11. Входы питания третьего 17 и второго 18 делителей частоты и первого

15 электронного ключа 15 подключены к первому выводу первого переключателя 19, ко второму выводу которого подключены входы питания квадратора 6, второго 16 и . третьего 20 электронных ключей. Третий

20 электронный ключ 20 включен между выходом генератора 10 и вторым входом фазового детектора 8, к которому подключен выход второго делителя частоты 18. Второй переключатель 21 включен между вторым вхо25 дом генератора 10 и дополнительной частотозадающей цепью 22. Третий переключатель 23 включен параллельно емкости корректирующего фильтра 3. Первый вход блока сравнения 14 соединен с входом квад30 ратора 6 через фильтр верхних частот 24.

Стереодекодер работает следующим образом. Входной стереосигнал поступает на вход 4 стереодекодера, содержащего суммарно-разностный преобразователь 1, 35 состоящий из четырехквадрантного перемножителя 2, выходы которого являются выходами стереодекодера, между которыми включен корректирующий фильтр 3. Этот фильтр осуществляет коррекцию разност 10 ного (А — В) сигнала при приеме сигналов с полярной модуляцией (фиг. 2,а). При этом на второй вход перемно>кителя. 2 подается с выхода 13 опорное напряжение поднесущей частоты 31, 25 кГц, которое формирует45 ся блоком восстановления поднесущей частоты. В этом режиме все переключатели

19, 21 и 23 находятся во втором положении (II), напряжение питания через переключатель 19 подано на квадратор 6, электронные

50 ключи 16 и 20 замкнуты, делители частоты

17 и 19 выключены, электронный ключ 15 разомкнут, Формирование опорного напряжония 31 25 кГц блоком восстановления .. поднесущей частоты 5 осуществляется сле55 дующим образом, Отфильтрованный фильтром верхних частот 25 сигнал удваивается квадратором

6. Напряжение удвоенной поднесущей частоты 62,5 кГц выделяется блоком ФАПЧ 7.

Затем это напряжение делится по частоте

1838883

45

50 на два первым делителем частоты 11 и через кОммутатор 12 поступает на второй вход ч@тырехвадрантного перемножителя 2 в виде опорного напряжения, когерентного под( несущей частоте 31, 25 кГц. Управление коммутатором 12 обеспечивается при помощи блока сравнения 14 фаз напряжений поднесущей частоты входного стереосигнала (на входе блока 5) и опорного, поступающего через электронный ключ 16 со второго выхода первого делителя частоты 11, При приеме сигналов с полярной модуляцией без ослабления разностного сигнала (А-В) в области поднесущей частоты (фиг, 2„в) переключатель 23 переводится в положение, при котором емкость корректирующего фильтра закорочена, При приеме сигналов с пилот-тоном (фиг. 2,б) все переключатели 19, 21 и 23 переводятся в первое положение (1), напряжение питания через переключатель 19 подано на делители частоты 17 и 18, электронный ключ 15 замкнут, электронные ключи 16 и 20 разомкнуты, квадратор 6 выключен, Входной сигнал с входа стереодекодера 4 через замкнутый электронный ключ 15 поступает на первый вход фазового детектора 8, Петля регулирования блока

ФАПЧ 7, разомкнутая электронным ключом

20, замыкается с выхода генератора 10, через делитель частоты на два 11, делитель

Частоты на два 18 на второй вход фазового детектора 8. При замкнутой таким образом петле регулирования блока ФАПЧ на выход

13 блока восстановления поднесущей частоты 5 через коммутатор 12 поступает опорное когерентное напряжение поднесущей частоты 38 кГц. Синхронизация петли осуществляется на частоте пилот-тона (19 кГц).

Отличие частоты поднесущей в системе с пилот-тоном (38 кГц) от частоты поднесущей с полярной модуляцией (31, 25 кГц) компенСируется подключением дополнительной частотозадающей цепи 22 переключателем

21 к генератору 10. Блок сравнения фаз 14, управляющий коммутатором, сравнивает сигнал пилот-тона, содержащийся в стереосигнале, поступающем с входа сгереодекодера 4, с опорным когерентным сигналом пилот-тона с выхода делителя частоты на два 17. Третий делитель частоты 17 работает в фазосдвигающем на к/2 режиме деления, так что сигнал 19 кГц нз выходе третьего делителя 17 сдвинут на zt /2 относительно сигнала 19 кГц на выходе второго делителя, частоты 18. Для этого третий делитель частоты 17 содержит два входа, второй — счетный, соединен с первым выходом первого

35 делителя 11, а первый-синхронизирующий, соединен с выходом второго делителя 18, Таким образом, стереодекодер обеспечивает прием сигналов радиовещания в системах с полярной модуляцией и в системе с пилот-тоном, Формула изобретения

1. Стереодекодер, содержащий суммарно-разностный преобразователь, состоящий из четырехквадрантного перемножителя, выходы которого являются выходами стереодекодера, между которыми включен корректирующий фильтр, при этом первый вход суммарно-разностного преобразователя, являющийся входом стереодекодера, соединен с входом блока восстановления поднесущей частоты, который содержит последовательно соединенные квадратор и блок фазовой автоподстройки частоты, состоящий из последовательно включенных фазового детектора, фильтра нижних частот и генератора, выход которого, являющийся выходом блока фазовой автоподстройки «астоты, через первый делитель частоты на два подключен к входам коммутатора, выход которого является выходом блока восстановления поднесущей частоты и подключен к второму входу суммарно-разнсстного преобразователя, кроме того, блок восстановления псднесущей частоты содержит блок сравнения фаз, выход которого подключен к управляюьцему е оду коммутатора, а первый вход является входом блока восстановления поднесущей частоты, о т л ич а ю шийся тем, что, с целью приема сигналов радиовещания с частотной модуляцией в системах с полярной модуляцией и с пилот-током, в блок восстановления поднесущей частоты введены три электронных ключа, три переключателя, второй и третий делители частоты и дополнительная частотозадающая цепь, причем первый электронный ключ включен между первым входом блока сравнения фаэ и первым входом фазового детектора, второй электронный ключ включен между вторым выходом первого делителя частоты и вторым входом блока сравнения фаз, к которому подключены последовательно соединенные третий и второй делители частоты, вход последнего из которых соединен с вторым выходом ïåðвого делителя частоты, вход третьего делителя частоты подключен к первому входу первого дели.еля частоты, входы г,итания первого и второго делителей частоты и первого электронного ключа подключены к первому выводу первого переключателя, к

1838883 второму выводу которого подключены входы питания квадратора, второго и третьего электронных. ключей, последний из которых включен между выходом генератора и вторьил входом фазового детектора, к которому подклюЧен выход второго делителя частоты, второй переключатель включен между вторым входом генератора и дополнительной частотозадающей цепью, первый вход блока сравнения соединен с входом квадратора, а третий. переключатель включен параллельно емкости корректирующего фильтра.

2. Стереодекодер по и, 1, о т л и ч а юшийся-тем, что, с целью повышения

5 устойчивости синхронизации при работе в системах с полярной модуляцией, в блок вос. становления поднесущей частоты введен фильтр верхних частот, причем первый вход блока сравнения фаз соединен с входом квад10 ратора через фильтр верхних частот.

1838883

Я+Я

Уд(Л.25п /4) Рр.р. 13К ГО,, ят (Я /Ц ) In (51, Г5 ко) Pö Я

Составитель В. Милехин

Техред М,Моргентал Корректор П. Гереши

Редактор Т, Рожкова

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

Заказ 2929 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ. СССР

113035, Москва, Ж-35, Раушская наб., 4/5