Интегрирующее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства N

Заявлено 02.Х1.1964 (№ 927990/26-24) Кл. 42m, 15 с присоединением заявки №

Комитет по делам изобретений и открытий при Совете Министров

СССР

МПК 601q

УДК 681.142.07(088.8) Приоритет

Опубликовано 1ЗХ111.1966. Бюллетень ¹ 17

Дата опубликования описания 7.Х.1966

Ю. В. Розен, В. И. Мельввков, В. Ф. Марков к И. П. Верб закиев

М,:з П,, ° 1 lr (;е"!-!

Лвторы изобретения

Заявитель

ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО

В известных интегрирующих устройствах в качестве суммирующего элемента используются электромеханические реле с храповыми механизмами, электрические шаговые двигатели и двигатели постоянного и переменного тока.

Для сброса показаний в таких устройствах применяются дополнительные электромеханические устройства, используемые только на время сброса (например, муфты) или специальные генераторы (для ускоренного реверса шаговых двигателей) .

Предлагаемое устройство содержит в качестве суммирующего элемента асинхронный двигатель и отличается от известных тем, что двигатель управляется от двух триггеров.

Благодаря позиционной обратной связи, охватывающей двигатель и один из триггеров, осуществляется импульсный пошаговый режим интегрирования, что позволяет повысить точность интегрирования. Так как выход второго триггера сблокирован со входом первого, то подача сигнала на вход второго триггера реверсирует двигатель и позволяет просто осуществить сброс показаний в режиме непрерывного вращения.

В устройстве применен пересчетный блок, который осуществляет повторные запуски двигателя в режиме непрерывного интегрирования путем опрокидывания второго триггера и разблокирования первого в момент, когда приращение интеграла за время сброса становится равным заранее выбранному значению. Это позволяет устранить ошибку интегрирования, накапливающуюся за время сброса.

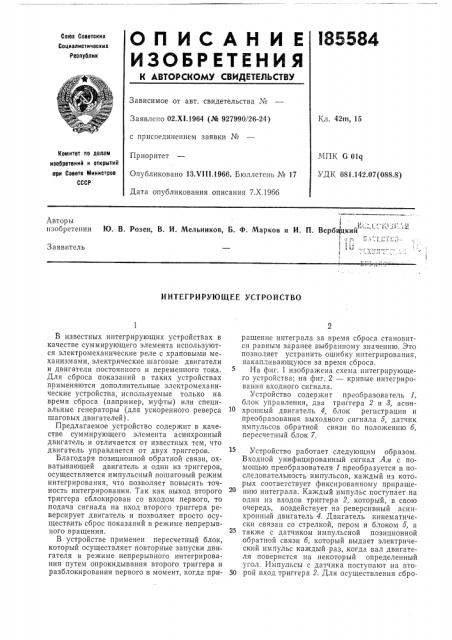

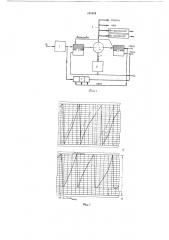

На фнг. 1 изображена схема ннтегрирующего устройства; на фиг. 2 — кривые интегрирования входного сигнала.

Устройство содевжит преобразователь 1, блок управления, два триггера 2 и 8, асинхронный двигатель 4, блок регистрации и преобразования выходного сигнала б, датчик импульсов обратной связи по положению б, пересчетный блок 7.

Устройство работает следующим образом.

Входной унифицированный сигнал Ал с помощью преобразователя 1 преобразуется в последовательность импульсов, каждый из которых соответствует фиксированному приращению интеграла. Каждый импульс поступает на один из входов триггера 2, который, в свою очередь, воздействует на реверсивный асинхронный двигатель 4. Двигатель кинематически связан со стрелкой, пером и блоком б, а также с датчиком импульсной позиционной обратной связи б, который выдает электрический импульс каждый раз, когда вал двигателя повернется на некоторый определенный угол. Импульсы с датчика поступают на вто.

30 рой вход триггера 2. Для осуществления сбро185584

15 го г5

З0

45 са используется второй триггер 8, включающий двигатель на реверс.

Каждый импульс с выхода преобразователя переводит триггер 2 в такое состояние, при котором его выходной триод включает двигатель, Двигатель приводит во вращение и перемещает кинематически связанные с ним устройства до тех пор, пока импульс позиционной обратной связи не вернет триггер 2 в исходное состояние, соответствующее торможению двигателя.

Для осуществления сброса (например, при достижении предельной отметки шкалы) подается команда на триггер 3, который переходит при этом в новое устойчивое состояние, так что его выходной триод включает двигатель.

Двигатель реверсируется и возвращает кинематически связанные с ним устройства в начальное положение, фиксируемое нулевым упором. Одновременно с включением двигателя на реверс триггер 8 блокирует выходной триод триггера 2, запрещая ему воздействовать на двигатель при любом положении этого триггера 2. После реверса двигатель находится на нулевом упоре до тех пор, пока триггер

8 не будет переведен в исходное состояние

«пуск».

В режиме непрерывного интегрирования необходимо учитывать приращения интеграла, накопившегося за время сброса. В устройстве режим непрерывного интегрирования осуществляется путем подачи на вход «пуск» триггера 8 определенного, заранее выоранного, к-ro импульса приращения интеграла, выделяемого пересчетным блоком 7. При этом синхронизация начала пересчета с момента подачи сигнала на сброс осуществляется гашением счетчика по команде «сброс».

Для того чтобы учесть приращение интеграла за время сброса, нулевой упор блока 5 выставляется так, чтобы после окончания сброса стрелка и перо не доходили до нулевой отметки шкалы (диаграммы) на величину, соответствующую к импульсам приращения интеграла, Коэффициент пересчета К выбирается таким образом, чтобы пересчетное устройство не переполнилось за время сброса при максимальном значении параметра Ал „„, на входе.

Метод непрерывного интегрирования, осуществленный в предлагаемом устройстве, иллюстрируется графиками на фиг. 2. На фиг. 2,а показана интегральная кривая при наличии накапливающейся погрешности б за счет потери импульсов приращения интеграла при сбросе. Пунктирная линия соответствует фактическому изменению значения интеграла.

Фиг. 2,б дает представление о записи íà графике предлагаемого прибора, работающего в режиме непрерывного интегрирования, и о выборе величины 1(. Бремя ссбр уу(соответствует максимальному времени сброса, n — число импульсов приращения интеграла на всю шкалу; угол тАм„„,, определяет максимально возможный наклон интегральной кривой.

Предмет изобретения

1. Интегрирующее устройство, содержащее преобразователь входного сигнала в последовательность импульсов, суммирующий асинхронный двигатель, блок управления и блок регистрации и преобразования выходного сигнала, отличающееся тем, что, с целью повышения точности интегрирования и упрощения сброса показаний, блок управления выполнен в виде двух триггеров, на выходы которых подключен двигатель, входы одного из триггеров соединены с преобразователем и датчиком импульсов позиционной обратной связи, а входы второго триггера связаны с элементами сброса и пуска, причем выход этого триггера сблокирован со входом первого.

2. Устройство по п. 1, отличающееся тем, что, с целью устранения ошибки при непрерывном интегрировании, в нем установлен пересчетный блок, связанный с выходом преобразователя и входами второго триггера.