Патент ссср 187399

Иллюстрации

Показать всеРеферат

П И С А Н И Е l87399

Союз Советски»

Сопиалистическик

Республик и за ы итян ия

Зависимое от авт. свидетельства №

Заявлено 09.Х1.1965 (№ 1039709/26-24) с присоединением заявки №

Приоритет

Опубликовано 11.Х.1966. Бюллетень № 20

Дата опубликования описания 26.XI. 1966

}(л, 42m, 14

Комитет по делам изобретений и открытий при Совете Министров

СССР

МПК 6 06f

УДК 681.142.07(088.8) УСИЛИТЕЛЪ СЧИТЫВАНИЯ

Известны усилители считывания на транзисторах со стробированием для запоминающих устройств.

Предложенный усилитель отличается от известных тем, что он содержит два запоминающих биакса с обмотками записи, считывания и выходными обмотками, при этом выходная обмотка каждого биакса подключена к базам первого и второго транзисторов, а эмиттер первого транзистора соединен с коллектором второго транзистора, что повышает надежность усилителя.

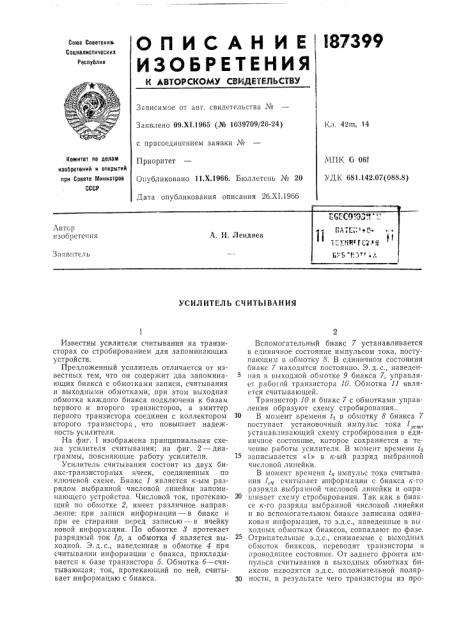

На фиг. 1 изображена принципиальная схема усилителя считывания; на фиг. 2 — диаграммы, поясняющие работу усилителя.

Усилитель считывания состоит из двух биакс-транзисторных ячеек, соединенных по ключевой схеме. Биакс 1 является к-ым разрядом выбранной числовой линейки запоминающего устройства. Числовой ток, протекающий по обмотке 2, имеет различное направление: при записи информации — в биакс и гри ее стирании перед записью — в ячейку новой информации. I Iо обмотке 3 протекает разрядный ток 1р, а обмотка 4 является выходной. Э.д. с., наведенная в обмотке 4 при считывании информации с биакса, прикладывается к базе транзистора 5. Обмотка б — считывающая; ток, протекающий по ней, считывает информацию с биакса.

Вспомогательный биакс 7 устанавливается в единичное состояние импульсом тока, посту пающим в обмотку 8. В единичном состоянии биакс 7 находится постоянно. Э.д.с., наведенная в выходной обмотке 9 биакса 7, управляеl работой транзистора 10. Обмотка 11 является считывающей.

Транзистор 10 и биакс 7 с обмотками управления образуют схему стробирования..

В момент времени t> в обмотку 8 биакса 7 поступает установочный импульс тока 1 „, устанавливающий схему стробирования в единичное состояние, которое сохраняется в течение работы усилителя. В момент времени 4 записывается < 1» в к-ый разряд выбранной числовой линейки.

В момент времени t> импульс тока считывания I, считывает информации с биакса и-ro разряда выбранной числовой линейки и опрашивает схему стробирования. Так как в биаксе к-ro разряда выбранной числовой линейки и во вспомогательном биаксе записана одинаковая информация, то э.д.с., наведенные в вы. ходных обмотках биаксов, совпадают по фазе.

Отрицательные э.д.с., снимаемые с выходных обмоток биаксов, переводят транзисторы в проводящее состояние. От заднего фронта импульса считывания в выходных обмотках биаксов наводятся э.д.с. положительной поляр30 ности, в результате чего транзисторы из прог г-Ю

tie 7

3 4 5 "б.

1 о

1cv г 9

Фиг. Z

Фг 2. /

Составитель Б. Тимохин

Редактор П. Вербова Техред А. А. Камышникова Корректоры: Е. Ф. Полионова и О. Б. Тюрина

Заказ 3441711 Тираж 1075 Формат бум, 60X90 /ä Объем 0,16 изд, л. Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совеге Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 ьодящего состояния переходят в режим отсечки. B момент времени 1 в обмотку 2 биакса 1 поступает числовой ток l, отрицательной полярности, который стирает информации — устанавливает бпакс 1 в нулевое состояние. В момент времени t,- в обмотку 2 поступает числовой ток амплитудой + - /в1, а в обмотку

8 — разрядный ток амплитудой — i/,1,„. Ре. зультирующий ток (+ г/в 1,„,) не изменяет нулевого "îñòîÿíèÿ биакса к-го разряда выбранной числовой линейки. В момент времени 1, в обмотки б и 11 биаксов 1 и 7 поступает импульс тока считывания 1„,. Так как в обоих биаксах записана различная информация, то э. д. с., наведенные при считывании в выходных обмотках 4 и 9, имеют различную полярность. От переднего фронта импульса считывания в выходной обмотке

4 наводятся э. д. с. положительной полярности, а в выходной обмотке 9 биакса 7 — отрицательной полярности. От заднего фронта импульса считьвЛннн-.полярность и э. д. с., наведенные и выходных, обмотках биаксов, будут иметь противоположный знак. г1т действия этих э.д. с. усилитель счизывания не срабатывает, что будет соотьетствовать считыванию

«0» с к-го разряда.

Таким образом, усилитель считывания надежно работает при считывании «1» с к-го разряда выбранной числовой линейки.

При считывании «0» и при действии помех в моменты записи и стирания информации усилитель считывания надежно закрыт.

Предмет изобретения

Усилитель считывания на транзисторах со стробированием для запоминающих устройств, oòëè÷ïющийся тем, что, с целью повышения надежности работы запоминающего устройства, он содержит два запоминающих биакса с обмотками записи, считывания и выходными обмотками, при этом выходная обмотка каждого биакса подключена к базам первого и второго транзисторов, а эмиттер первого транзистора соединен " коллектором второго тран--истора.