Патент ссср 195202

Иллюстрации

Показать всеРеферат

Союз Соеетскиз

Социалистические

Республик

Зависимое от авт. свидетельства №

Заявлено 08,71.1966 (№ 1082060 26-24) с присоединением заявки №

Приоритет

Кл. 42m, 14

МПК Ст 061

Комитет по делам изобретений и открытий при Сосете соинистрое

СССР

УДК 681.142:53.087.92 (088.8) Опубликовано 12.И,1967. Бюллетень М 9

Дата опубликования описания 19.Л.1967

Лвтор изобретения

b. Л, Ермилов

Институт электромеханики

Заявитель

ЦИФРОВОЙ ЭКВИДИСТАКТНЫЙ ПРЕОБРАЗОВАТЕЛЬ

Известны цифровые эквидистантные преобразователи для систем программного управления станками, выполненные на элементах и узлах цифровых дифференциальных анализаторов.

Предложенный преобразователь отличается от известных тем, что входы и выходы сдвигающих регистров соединены через разделительные схемы со входами реверсивных счетчиков, подключенных к преобразователям кода в число импульсов, выходы которых соединены со входами схемы возведения в квадрат приращений двух координат и извлечения квадратного корня из суммы этих квадратов и со входами схемы умножения приращений координат на радиус эквидистанты, причем выход схемы извлечения квадратного корня соединены со входами делителей двух схем деления, входы делимых которых подключены к выходам схем умножения на радиус эквидистанты, а выходы совместно с выходами средних ячеек сдвигающих регистров соединены с выходными зажимами устройства.

Это позволяет расширить класс преобразуемых кривых без перестройки структуры устройства.

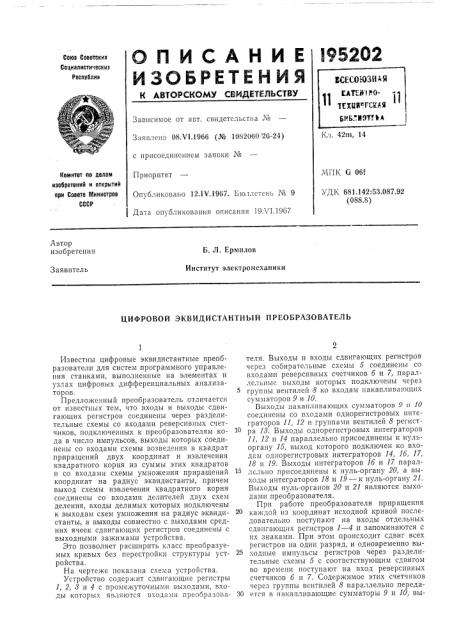

На чертеже показана схема устройства.

Устройство содержит сдвпгающие регистры

1, 2, 8 и 4 с промежуточными выходами, входы которых являются входами преобразователя. Выходы и входы сдвигающнх регистров через собирательные схемы 5 соединены со входами реверсивных счетчиков 6 и 7, параллельные выходы которых подключены через группы вентилей 8 ко входам накапливающих сумматоров 9 и 10.

Выходы накапливающих сумматоров 9 и 10 соединены со входами однорегистровых интеграторов 11, 12 и группами вентилей 8 регистра 18. Выходы однорегистровых интеграторов

11, 12 и 14 параллельно присоединены к нульоргану 15, выход которого подключен ко входам однорегистровых интеграторов 14, 16, 17, 18 и 19. Выходы интеграторов 16 и 17 napaëлельно присоединены к нуль-органу 20, а выходы интеграторов 18 и 19 — к нуль-органу 21.

Выходы нуль-органов 20 и 21 являются выходами преобразователя.

Прн работе преобразователя приращения каждой из координат исходной кривой последовательно поступают на входы отдельных сдвнгающпх регистров 1 — 4 и запоминаются с их знаками, При этом происходит сдвиг всех регистров на один разряд, и одновременно выходные импульсы регистров через разделительные схемы 5 с соответствующим сдвигом во времени поступают на вход реверсивных счетчиков 6» 7. Содержимое этих счетчиков через группы вентилей 8 параллельно переда3гт ется в ттакапливающие сумматоры 9 и 10, вы195202

Предмет изобретения. 7 Jj

I —:З е

Ф"! 38 т

Составитель А. А. Маслов

Редактор Л. А. Утехина Текред A. А. Камьгкгникова Корректоры: О. 6, Тюригга и М. П. Ромашова

Заказ !739 10 Тираж 535 Подписное

ЦНИИПИ Комитета по делам ггзобретений н о-крытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Тгп1отрафия, пр. Сапунова, 2 ходные импульсы которых представляют .собой усредненные величины входных приращений. Эти величины возводятся в,квадрат при помощи однопегистровых интетраторов ll и 12 и суммируются в накопителе 15, который совместно с интегратором 14 образует схему извлечения квадратного корня из полученной суммы.

Выходные импульсы накопителя 15, представляющие приращения квадратного корня, поступают на две схемы деления в качестве приращений величины делителя. Приращения делителя для этих схем образуются умножением усредненных величин входных приращений на величину радиуса эквидистанты, которая вводится в регистр 13. Умножение производится регистром И и двумя группами вентилей 8, управляемых этим регистром.

Одна из схем деления образована однорегистровыми интеграторами 1б и 17, а также накапливающим сумматором 20, выполняющим фукцию нуль-органа, Аналогичная схема деления образована интеграторами 18 и 19 и нуль-органом 21.

Выходные импульсы нуль-органов 20 и 21, представляющие результаты вычисления схем деления, поступают на выход преобразователя и совместно с исходными приращениями ЛХ„ и ЛУ„образуют приращения координат эквпдистанты ЛХ и ЛУ.

Цифровой эквидистантный преобразователь для систем программного управления станка5 ми, содержащий сдвигающие регистры, реверсивные счетчики с параллельными выходами, преобразователи кода в число импульсов, схему возведения приращений двух координат в квадрат и извлечения квадратного корня пз

10 суммы этих квадратов, схему умножения приращений координат на радиус эквидистанты и две схемы деления, отличающийся тем, что, с целью расширения класса преобразуемых кривых без перестройки структуры устройства, 15 входы и выходы сдвигающих регистров соединены через разделительные схемы со входами реверсивцых счетчиков, подключенных к преобразователям кода в число импульсов, выходы которых соединены со входами схемы

20 возведения в квадрат приращений двух координат и извлечения квадратного корня из суммы этих квадратов и со входами схемы умножения приращений координат на радиус эквидистанты, причем выход схемы извлечения

25 квадратного корня соединен со входами делителей двух схем деления, входы делимых которых подключены к выходам схем умножения на радиус эквидистантны, а выходы совместно с выходами средних ячеек сдвигающих

30 регистров соединены с выходными зажимами устройства.