Патент ссср 195214

Иллюстрации

Показать всеРеферат

Союз Соеетскик

Социалистическими

Республик

Зависимое от авт. свидетельства №

Заявлено 18.1Ъ .1066 (Гча 1071094/26-24) Кл. 42m, 14

21а<, 37/58 с и тисосдинениeм за, âêè №

МПК 6 063

Н 03k

УДК 681.142.07(088.8) Приоритет

Опубликова;о 12,1V.1967, Б|оллстспь М 9

Дага опуб. пко-ÿ;ÿêæ. описания 20.ч 1.1967

Комитет по делам изобретений и открытий ори Совете Мииистроз

СССР

Авторы изобретен:m

O. А. Никольский и Л. Г. Титоь

Союзный научна-исследовательский институт приборостроения

Заявитель

11ОЫ1ЕДОВАТЕЛЬ11ОЕ ЗАЛОМИНАЮШЕЕ УСТРОЙСТВО

Известны последовательные запоминающие устройства на линиях задержки, содержащие параметроны в тракте хранения.

Предложенное устройство отличается тем, что в нем выход линии задержки подключен через ключи-преобразователи ко входам схемы фазирования, каждый выход которой соединен соответственно с каждым единичным входом триггера; единичные выходы каждого триггера подсоединены соответственно ко входам схемы фазирования; а один из выходов схемы фазирования подключен через схему храпения «о входу линии задержки.

Это увеличивает надежность согласования линии задержки с параметронами в широком диапазоне температур.

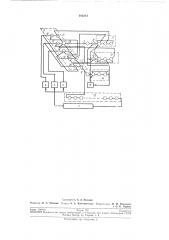

На чертеже дана схема запоминающего устройства.

Выход линии задержки 1 через ключи-преобразователи 2, 8, 4 соединен со схемой фазировапия 5, имеющей три выхода б, 7, 8, два из которых б и 7 через параметронные ключи 9 и 10 соединены соответственно со входами триггеров 11 и 12, а третий выход 8 соединен со входом первого из параметропов тракта хранения 18 и установочным входом триггера 14 рабочей части цикла, который в свою очередь соединен со счетчико и 15 тактов, выход которого подключен к сбросовым входам триггеров 11, 12 и 14.

Схема фазировки состоит из десяти параметронов, пять из которых 1б, 17, 18, 19, 20, являются входными параметронными ключами и соединены с выходами ключей-преобразователей 2, 8, 4, а пять других соединены последовательно между собой, причем каждый из этих пяти параметронов одновременно соединен с соответствующим входным параметронпым ключом. Кроме того, входы первых трех входных параметронных ключей 1б, 17, 18 соединены с выходами последних трех входных параметронных ключей 18, 19, 20 соответственно.

Выходы триггеров 11 и 12 соединены соотт5 ветственно со входами параметронов 21, 19 и

22, 20.

Устройство работает следующим образом, В начале информации записывается стартовый импульс. Стартовый импульс, вышедший

20 из линии задержки, появляется на выходе одного из ключей-преобразователей 2, 8, 4 (или в крайнем случае двух при скважности радиоимпульсов накачки, равной 0,5) и поступает на схему б фазирования. При этом он прохо25 дит через те параметронные ключи 1б, 17, 18, 19, 20, которые связаны с данным ключомпреобразователем. Пройдя схему фазировкп, стартовый импульс появляется на выходе б, либо на выходе 7, либо ни на одном из них и

3Q сооч.нетственно переводит в ocTQHHIIp «1»

4 триггер 11, лиоо трипер 12, либо нп -от, пп другой. Но прп этом стартовый импульс всегда появляется на выходе 8 и переводит в состояние «1» триггер И, задающий рабочую часть цикла.

Триггеры li и 12 на данный цикл выбирают безопасньш канал из трех входных пар".метронных ключей, через которые должна пройти информацпя.

Прп этом возможны трп слу (ая:

1. Если триггер 11 находитс» В ссстсяпи .

«Î», триггер 12 — в состоянии «О», то откр:.: ты параметронныс ключи 17, 8, 19 (приорптетный ключ 18).

2. Если риггер 11 находится в состоянии

«1», Tp Hp(ep 12 — В сосТО» 1(и и «О», тс откр ь!ты параметронные ключи 16, 17, 18 (приоритетный ключ 17).

3. Если триггер 11 находится в состоянии

«О», триггср 12 — в состоя::ши «1», то сткрыгы i(apai(v(pol,ныр !(;,,(0 (1! 1а (9 20 (и и Вч тсгпый „(люч 19).

Рассмотрим эти случаи.

1. Если стартовый импульс появляется на ьыходе ключа-преобразователя 4, то при этом

Он поступ3ет на В..сд п3paìeTpÎПГ(ОГО кл(счa

18. TBK I(BK OCTB;(bl(b!e ВходнЫС парамстронные ключи закрыты (<0», !, то благодаря инверсной связп между ((Bpa»CTpoi;aзш 20 и 18, последш(й открыт для прохождения стартовоГО ИЪ(П>J(bca. СТарТОВЫП H(1(п>ЛЬС чСрез СОО! .. рательную схему проходит на Выход 8 и через параметроны тракта храпения 18 в линшо задержки, переьодя при этом триггер 14 з состояние «1». Но триггеры 11 и 2 остаются в состоянии «О» и блокируют параметро iilыс ключи 20 и 21. Открыты для прохождения информации ключи 17, 18 19. Если за этот цикл изменяется время задержки,aHIIr(II задержки и импульсы начинают появляться ila Dblxo;Iax ключей-преобразователей 2 плп 8, то это пе вызывает сбоев в работе, т. к. в этом случае информация идет через параметроны 19 и.;и

17 соответственно и далее через собирательную схему на выход схемы фазировкп. Не вызывает сбоев и появление импульсов на вь.ходе двух ключей-преобразователей (только подтверждение сигнала).

2. Если стартовый импульс появляется на выходе ключа-преобразователя 8, то прн этом он поступает на входы параметропных ключей

17 и 20. Но ключ 20 закрыт (триггер 12 состоянии «0»). Ключ 17 открыт олагодаря Инверсной связи с закрытого кл(оча 19. Поэтому

cTapToBbIH HMII) Ibc проходит

1. и 20, зато открыты ключи 16, 17, 18 и 21

40 .".5

65! б.(-. ->да - <с -:О>:и(:(- «1» "p ll! CI>3 1) . Приоритетным;!Вляется ключ 17, НО I(ocT> пление информации на ключи 16 и 18 также нс Вызыьаст сбоев, поскольку все они объединены собирательной схемой. Лналогично не нарушает нормальной работы и появление импульсов па Выходах двух ключеп-преобразователей.

;>. Если cTapTOBb(II им(!ульс появляется и(! выходе кгнсча-преобразователя 2, то при этом o! I поступ ст на входы параметронных ключей 16 H 19. Оба ключа открыты; ключ 16 благодаря инверсной связи с закрытого клю la i8, ключ 19 благодаря инверсной связи с (рнГГсра i 1, пахсдящеГОся В состоянии «О:>.

Ста .говый;-(а!пульс проходит через ключи 16 и 19, но в первом случае его дальнейшее прохожде(ше блокпрозано закрытым ключом 21, а I;0 втором слу -:ае он появляется на выходе схемы (! азирсвки и через пар аметронпый

10 ilepe(I0 HT TpHITep 12 v, состояние

«1».

При этом про 0>êäåíèe информации разрешается только через ключи 18, 19, 20. Через ключи 16, 17 информация может пройти, но ее дальнейшее прохождение будет блокироваi;o закрытыми параметро Пыми кл(очами 21 и

22,первый благодаря состоянию «О» тригг,.— ра 11, Второй благодаря состоянию «1» тр (ггера 12). Приоритетным в данном случае является ключ 19, однако появление импульсов на Входах ключей 18 и 20 также не вызывает нарушений В xpal .ÿùåéñÿ информации.

Б случае пояВлсп(!.! i!»(пульсов I(3 В(>(ход(1х двух ключей-преобразователей сбой может возникнуть лишь в том случае, когда рабочими являются крайние пз входных параметрсн(Ib(x ключей (16 и 18, 17 и 19, 18 и 20) выбранного канала. iToub(искл(счить сбой, Один из этих ключей блокируется другим, Между стартовым импульсом и последующей ннформацисй должен быть интервал минимум в два такта, необходимый для перестроики триперов 11 и 12. После того как триггер И переходит в состояние «1», он блокирует параметронпые ключи 9 и 10.

Таким образом, вся последующая информацпя не ьызывает персстройки триггеров 11 и

12. После прохождения через схему фазиров;H I(oc IegiIeII uH! bi HПф0рм3ции, TpH((epb(11, 12 и 14 сбрасываются В состояние «О» импульсом персполненпя счетчика 15 тактов (емкость егo равна числу хранимых двоичных единиц) и 0,i начинает пересчитывать ГаКТОВЫЕ (:<и!У !ЬСЫ С МОМЕНТ3 ПОЯВЛЕНИЯ СТ3Ртового импульса iia выходе 8.

Б следующий цикл стартовый импульс снова появляется (га выходе линии задержки, проходит схему фазировкп и производит перестройку триггеров 11 и 12.

Так как перестройка этих триггеров происходит в ка>к,-„ый цикл, а изменение времени задер>кки линни задержки, за цикл намного меньше периода тактовых импульсов, то прак195214 тически Обеспечивается надежная работа предлагаемого запоминающего устройства в широком интсрвале температур.

При этом, конечно, длительность паузы („> с.Ы/ C, гд к — температурный коэффициент расширения линии;

1. — длина;

Л1 С вЂ” заданный интервал температур.

Предлагаемое запоминающее устройство реализовано на магниевой линии задержки и емкостных параметронах.

В качестве ключа-преобразователя использован полупроводниковый диод, включенныи в цепь связи мсжду двумя параметронами, один из которых является эталонным. НОрмально этот диод заперт и отпирается лишь импульсом с выхода линии задержки. Если амплитуды импульса с ВыхОдя линии задержки не хватает для отпирания диода (как в дан юм случае), импульс предварительно усил гв а ется.

На вход линии задержки поступает радиоимпульс (сложенный с эталонным) непосредственно с параметрона.

Запоминающее устройство может быть выполнено на любой линии задержки, а также на магнитном барабане и любых трехтактных мажоритарных элементах (параметронах, парах Гото на туннельных диодах н т. д.).

Предлагаемое запоминающее устройство на

5 линии задержки может быть применено в качестве оператпзного запоминающего устройства в параметронных вычислительных маши. пах.

10 Предмет изобретения

Последовательное запоминающее устройство, содержащее линию задержки, ключипреобразователи, схему фазирования, тригге15 ры и схему хранения, отличающееся тем, что, с целью увеличения надежности согласованияя линии задер>кки с параметронами в широком диапазоне температур, в нем выход линии задержки подключен через ключи-преоб20 разователи ко входам схемы фазирования, каждый выход которой соединен соответственно с каждым единичным входом триггера; единичные выходы каждого триггера подсоединены соответственно ко входам схемы фа25 зирования; а один из выходов схемы фазирования подключен через схему хранения ко входу линии задержки.

Составитель A. А. Плащин

Редактор Л. А. Утехина Тсхред А. А. Камышникова Корректоры: М. П. Рогиагиова и О. Ь. Тюрина

Заказ 1740i10 Тирани <35 Подписное

ЦНИИПИ Комитета по делам изоорстешш и открытий прп Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Тппографил, пр. Сапунова, 2