Устройство обнаружения ошибок при дискретной

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ l96087

ИЗОБРЕТЕ Н ИЯ

Своз Ссветскик

Социалистических

Республик фф ip

Зависимое от авт. свидетельства No

1 ...,1т,1Рт, i ! ! ,х111К Н 04/

1К 621.394.181.1 (088.8) Заявлено 08.Х11.1965 (№ 1041540/26-9) с присоединением заявки М

Приоритет

Опубликовано 16Х.1967. Б1оллетепь .xË 11

Дата опубликсвания описания ЗОЛ 1.1967

Комитет ло делам изобретений и открытий ори Совете Министров

СССР

Автор изобретения

Е. В. Митряев

Заявитель

Ленинградская военная инженернаь Краснознаменная академия им. А. Ф. Можайского

УСТРОЙСТВО ОБНАРУЖЕНИЯ ОШИБОК ПРИ ДИСКРЕТНОЙ

ПЕРЕДАЧЕ СИГНАЛОВ В АНАЛОГОВОЙ СИСТЕМЕ

С АВТОМАТИЧЕСКИМ ЗАПРОСОМ ОШИБОК

Известные устройства обнаружения ошибок при дискретной передаче сигналов в аналоговой системе с автоматическим запросом ошибок имеют ряд недостатков: сложные передающие устройства; ограниченная возможность применения в аналоговых системах без дискретизации, поскольку снижается точность и помехоустойчивость передачи.

Предлагаемое устройство позволяет уменьшить вероятность переспроса правильно принятых сигналов.

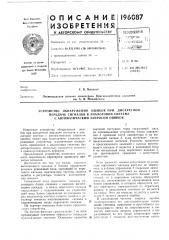

Достигается это тем, что между выходом вычитающего каскада и блоком управления включен решающий блок, состоящий из порогового каскада, анализатора частоты запроса ошибок и регулятора точности восстановления сигнала.

Сигнальный вход порогового каскада решающего блока соединен с выходом вычитающего каскада,: а выход порогового каскада

napaëëåëüHo с подключением на управляющий вход блока управления подсоединен через анализатор частоты запроса ошибок и регулятор точности восстановления сигнала к управляющему входу порогового каскада.

На чертеже показана блок-схема предлагамого устройства.

На выходе фильтра предсказания 1 по всем предыдущим значениям образуется очередное предсказанное значение. Очередное принятое значение поступает через сигнальный вход на запоминающее устройство блока управления 2 приемной части аппаратуры и на вычитающий каскад 8, куда поступает также предсказанное значение, Разность принятого и предсказанного значений с выхода вычитающего каскады 3 подается в решающий блок

4 на сигнальный вход порогового каскада 5, где производится сравнение с допустимой разностью.

Если разность меньше допустимой, то на выходе порогового каскада импульс не образуется, и в блоке управления 2 очередное заполненное значение поступает на выход в качестзе истинного. Если разность больше допус"òèìoé, то в пороговом каскаде образуется импульс, поступающий на управляющий вход блока управления, в котором образуется спгна,! переспроса, передаваемый по обратному каналу, и заполненное значение не выдается ны выход. Зтот же импульс подается в анали=а;op 6 частоты запроса ошибок.

В анализаторе частоты запроса ошибок ! êîHñòðóêTèâío это последовательное соединение счетчика импульсов и простейшего интегрирующего звена из сопротивления и емкости) импульсы запроса усредняются и образующееся на его в оде напряжение через

30 регулятор 7 точности восстановления сигна196087

Составитель В. Максимов

Техред Т. П. Курилко

Корректоры: В. В. Крылова и Л. В, Наделяева

Редактор Н. Корченко

Заказ 1925g9 Тираж 535 Подписное

Ц11ИИПИ Комитета по делам изобретений и огкрытнй при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 ла изменяет уровень срабатывания порогового каскада 5.

11ачальная установка 8 регулятора точности производится вручную по заданной средней частоте запроса ошибок или, что эквивалентно, по заданной средней точности восстановления,передаваемого сигнал а.

Предмет изобретения

1, Устройство обнаружения ошибок при дискретной передаче сигналов в аналоговой системе с автоматическим запросом ошибок, содержащее фильтр предсказания и вычитающий каскад, отличающееся тем, что, с целью уменьшения вероятности переспроса правпльно принятых сигналов, между выходом вычитающего каскада и блоком управления включен решающий блок, состоящий из порогового каскада, анализатора частоты запроса ошибок и регулятора точности восстановления сигнала.

2. Устройство по п. 1, отличающееся тем, что сигнальный вход порогового каскада решающего блока соединен с выходом вычитающего каскада, а выход порогового каскада параллельно с подключением на управляющий вход блока управления подсоединен через анализатор частоты запроса ошибок и регулятор точности восстановления сигнала к

15 управляющему входу порогового каскада.