Двухтактный разветвляющий элемент

Иллюстрации

Показать всеРеферат

Со!аз Соаатскик уаупуулиу Я Яo @ PQ$ЯЦЯЯ

l97292 т1з

71! ЗависIIAIoc от авт. свидетельства

Зат1влс11о 30.17.1966 (¹ 1074073!26-24) >410 I E-, $

Кл, 421п, 14

21а1, 36/18 с присоединением заявки №

Приоритет

МПК Су 061

Н 031<

УДЕ 681.142.07(088.8) Комитет па делам изобретений и открытий ари Совете Министров

СССР

Опубликовано 31.V.1967. Бюллетень № 12

Дата опубликования описания 21Л П.1967

Авторы изобретения

K). t-". Александров и М. A. Аидреещев

З" я итс,!ü

ДВУХТАКТНЫЙ РАЗВЕТВЛЯЮШИЙ ЭЛЕМЕНТ

Известны двухтактные разгетвляющие элементы, содержащие двухтактную ячейку памяти и буферную ячейку памяти.

Предложенныи элемент содержит дополнительный транзистор, эмнттер которого подкл10 Iен к эа1иттер 1у двухтактпо1! ячейки памяти, а база через резистор соединена с коллектором и подключена ко входу буферной ячейки.

Благодаря этому повышаются быстродействие и устойчивость работы при изменении питающих напряжений, а также появляется возможнос1ь твердосхемного исполнения элемента.

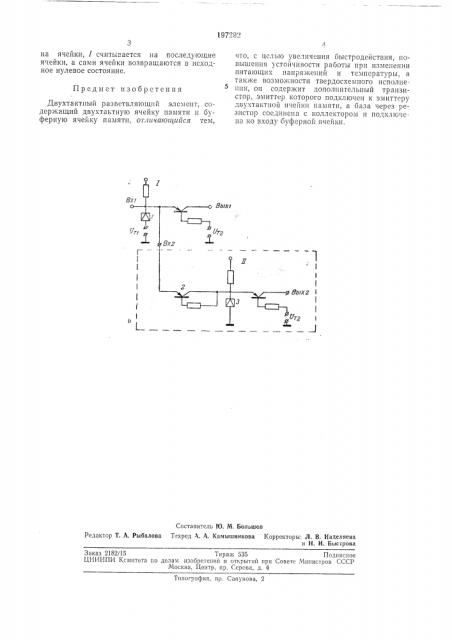

На чертеже приведена принципиальная схема разветвля1ощего элемента.

Разветвление информации происходит следующим образом, Единичное значение двоичной информации представляется низковольтным состоянием туннельного диода 1, пулевое значение — высоковольтным состоянием.

Пусть исходное состояние ячсш;н 1 и П соответствует «О». В этом случае эмиттер разветвляющего транзистора 2 находится под отрицатсльньум потепциалоы, задаваемым туннельным диодо 1. База разветвляющсго транзистора находится под потепцпало;i, задаваемым туннельным диодо;i 8 буферной ячейки П. Потенциалы эмиттера п базы разветвляющего транзистора близки по величине, ток через разветвля1ощий транзистор не протекает.

Запись «1» в ячейку памяти 1 происходит во время действия тактового напряжения Г,>.

При этом напряжение íà T) ííåëbiioì диоде 1 сначала падает. Поскольку туннельный диод

3 буферной ячейки П подключен к общей шине, то в течение периода времени первого такта происходит подзапирание разветвляющего транзистора. Это значит, что входной ток весь идет на запись «1» в ячейке I, В результате этого область устойчивой работы этой ячейки не сужается от подключения к ней буферной ячейки. Далее под действием входного сигнала и тактового напряжеш1я происходит переключение ячейки 1 в единичное состояние, после чего напряжение на туннельном диоде этой ячейки, изменяясь по закону изменения тактового напряжения, увеличивается до нуля. Одновременно происходит открыва11ие развствляющего транзистора

2, под действием тока в коллекторной цепи этого транзнс 1ора происходит перекл1оченпс ту1ьнельного диода 8 ячейки П в единичное состояние. Диод 8 псрсключается с задержкой после переключения туннельного диода 1 ячci êè 1. Оое ячейки 1 и П будут сохранять сдш:пчное состояние до момента действия тактового напряжения U,-. Этим тактовым

30 напряжением, одновременно воздействующим

1 ц у< ао

Предмет изобретения

Составитель Ю. М. Большов

Редактор Т. А. Рыбалова Техред А. Л. Камышиикова Корректоры: Л. В. Наделяева и H. И. Быстрова

Заказ 2182)15 Тираж 535 Подппс1ое

ЦНИИПИ Ксгиптета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 на ячейки, 1 считывается на последующие ячейки, а сами ячейки возвращаются в исходное нулевое состояние.

Двухтактный разветвляющн элемент, содержащий двухтактную ячейку памяти н буферную ячейку памяти, отл11чаюций ся тем, и iTo, с целью увеличения быстродействия, Iloвыщения устойчивости работы при изменении питающих напряжений и температуры, а также возможности твердосхемного исполне. ння, он содержит дополнителы1ый транзистор, эмиттер которого подключен к эмиттсру двухтактной ячейки памяти, а база через резистор соединена с коллектором и подкл1оче на ко входу буферной ячейки.!

l

Я яг 1

I ! тд