Компаратор

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано при построении аналоговых и аналого-цифровых схем на МДП-транзистсрах Целью данного изобретения является расширение функциональных возможностей устройства за счет обеспечения двухстороннего гистерезиса Для этого в компараторе, состоящем из последовательно соединенного дйфференциальнбго каскада , усилителя 10 с общим истоком, инвертора 11 и общей схемы управляющего напряжения 1, в зависимости от логического состояния выхода компаратора и выхода второго инвертора 14 включается один из ключей: первый 4 или второй 13 и в результате ответвляется ток, определяемый током генератора тока 2 и отношением размеров либо транзисторов входного и первого выходного, либо входного и второго выходного 12 в токовом отражателе 3, с ояного из двух выходов дифференциального каскада, вызывая эквивалентное напряжение смещения относительно опорного напряжения В результате в устройстве реализуется передаточная характеристика с двухсторонним гистерезисом относительно опорного напряжения. 2 ил

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ПАТЕНТУ

Комитет Рессийскей Федерации по иатентам и теварным знакам (21) 4927487/21 (22) 15.0491 (46) 15.10.93 Бюл йа 37-38 (71) Научно кследовательский институт измерительной техники (72) Богатырев EH. Поварницына З.М; Ивасенко

lOA; Егоров KB. (73) Нау вю-исследовательский институт измерительной техники (54) КОМПАРАТОР (57) Изобретение относится к импульсной технике и может быть иаюльзовано при построении аналоговых и аналого-цифровых схем на МДП-транзисторах Целью данного изобретеев является рaсaирение функциональных возможностей устройства за счет обеспечения двухстороннего гистерезиса

Для этого в компараторе, состоящем ю последоrsI3Ш (щ2Щ5!П СЗ (Я) 3 вательно соединенного дифференциального каскада, усилителя 10 с общим истоком, инвертора 11 и общей схемы управляющего напряжения 1, в зависимости от логического состояния выхода компаратора и выхода второго инвертора 14 включается один иэ ключей: первый 4 ипи второй 13 и в результате ответвляется ток, определяемый током генератора тока 2 и отношением размеров либо транзисторов входного и первого выходного, либо входного и второго выходного 12 в токовом отражателе 3, с одного из двух выходов дифференциального каскада, вызывая эквивалентное напряжение смещения относительно опорного напряжения

В результате в устройстве реализуется передаточная характеристика с двухсторонним гистерезисом относительно опорного напряжения. 2 ия

2001510

Изобретение относится к импульсной технике и может быть использовано при построении аналоговых и аналого-цифровых схем на МДП-транзисторах.

Известно. что для отделения информационного сигнала от напряжения шумов и помех меньшей амплитуды вводя гистереэис. с помощью положительной обратной связи, когда внешний резистор подключается с выхода на неинвертирующий вход. Однако при этом напряжение гистерезиса недостаточно для ряда областей применения, необходимы резисторы больших номиналов для устранения омической связи между входом и выходом, что затруднительно для реализации в интегральных схемах на небольшой площади и из-эа зависимости напряжения гистерезиса от технологических уходов, Наиболее близким по технической сущности к заявляемому является компаратор напряжения, содержащий источник управляющего напряжения. элемент смещения. состоящий иэ генератора тока. отражателя тока и ключа, а также последовательно сое- 25 диненные дифференциальный каскад, усилитель с общим источником и первый инвертор, а дифференциальный каскад выполнен на первом и втором транзисторах р типа, затвор первого из которых является соответственно неинвертирующим, а затвор второго — инвертирующим входами компаратора, истоки первого и второго транзисторов объединены и подключены к выходу генератора тока дифференциально- З5 го каскада на третьем транзисторе р типа, затвор которого соединен с входом источника управляющего напряжения, а нагрузкой дифференциального каскада являются нагрузочные транзисторы и типа, затворы ко- 40 торых объединены и подключены к стоку первого транзистора и к первому выходу отражателя тока элемента смещения, выполненного на транзисторах п типа, а вход отражателя тока соединен с выходом гене- 45 ратора тока элемента смещения на транзисторе р типа, затвор которого подключен к входу источника управляющего напряжения, а исток первого выходного транзистора отражателя тока элемента смещения под- 50 ключен к стоку транзистора и типа первого ключа, исток и подложка которого подключены к общей шине, а затвор к выходу первого инвертора и соответственно к выходу компаратора, шину источника напряжения.

В этом компараторе функция преобразования аналоговых сигналов следующая:

Gr-=1, при Од >Ов

01= О, при Оь < Ов - Ог

Q = Q -1, при Ов < и < <Ов+ Ог, где 0 — напряжение гистереэиса:

Q — выходной сигнал (текущее значение);

0 1 — выходной сигнал (предыдущее значение):

Од — входной сигнал на неинвертирующем входе компаратора:

08 — входной сигнал на инвертирующем входе компаратора.

Графическая иллюстрация алгоритма преобразования аналоговых сигналов в цифровые показана на фиг,2а. Таким образом, в схеме прототипа реализован односторонний гистерезис, при котором точность сравнения при переключении иэ противоположных уровней разная. Эта схема применима для узкого круга задач, с помощью схемы прототипа невозможно отделить информационный сигнал от напряжения шумов и помех меньшей амплитуды, симметричных относительно опорного сигнала.

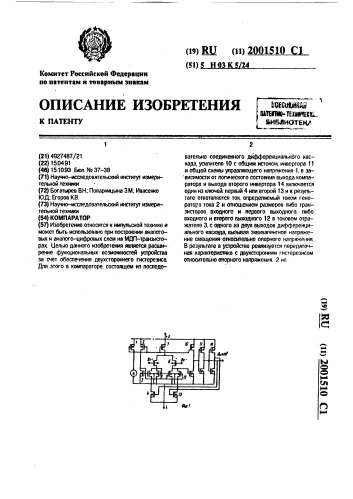

Цель изобретения — расширение функциональных возможностей эа счет обеспечения двухстороннего гистерезиса, Поставленная цель достигается тем, что в известный компаратор напряжения, содержащий источник управляющего напряжения. элемент смещения, состоящий из генератора тока и ключа, а также последовательно соединенные дифференциальный каскад, усилитель с общим истоком и первый инвертор, а дифференциальный каскад выполнен на первом и втором транзисторах р типа, затвор первого иэ которых является соответственно неинвертирующим, а затвор второго — инвертирующим входами компаратора, истоки первого и второго транзисторов объединены и подключены к выходу генератора тока дифференциального каскада на третьем транзисторе р типа, затвор которого соединен с входом источника управляющего напряжения, а нагрузкой дифференциального каскада являются нагрузочные транзисторы и типа, затворы которых объединены и подключены к стоку первого транзистора и к первому выходу отражателя тока элемента смещения, выполненного на транзисторах и типа, а вход отражателя тока соединен с выходом и генератора тока элемента смещения на транзисторе р типа. затвор которого подключен к входу источника управляющего напряжения, а исток первого выходного транзистора отражателя тока элемента смещения подключен к стоку транзистора и типа первого ключа. исток и подложка которого подключены к общей шине. а затвор к выходу пер2001510 6 вого инвертора и соответственно к выходу компаратора, шину источника напряжения, дополнительно введены второй выходной транзистор отражателя тока, второй ключ на транзисторах и типа, второй инвертор, причем сток второго выходного транзистора является вторым выходом отражателя тока и соединен со стоком второго транзистора р типа дифференциального каскада, затвор с входом отражателя тока, в исток со стоком транзистора второго ключа, исток и подложка которого соединены с общей шиной, а затвор — с выходом второго инвертора. вход которого соединен с выходом первого инвертора и соответственно с выходом компэратора. (известные технические решения КМДП компараторов с подобным двухсторонним гистерезисом авторами не обнаружены, На фиг. 1 изображена электрическая принципиальная схема КМДП компаратора; на фиг. 2а,б — передаточные характеристики соответственно прототипа и заявляемого решения.

КМДП компаратор содержит источник 1 управляющего напряжения, элемент смещения, состоящий из генератора тока 2 на транзисторе р типа, токового отражателя 3 на транзисторах и типа, ключа 4 на транзисторе и типа, дифференциальный каскад, состоящий из дифференциальной пары на первом, втором транзисторах р типа 5, 6, генератора тока 7 на третьем транзисторе р типа. токового отражателя, выполненного на нагрузочных транзисторах 8, 9 и типа, усилитель 10 с общим истоком, первый инвертор 11, второй выходной транзистор t2 отражателя тока 3, второй ключ 13 на транзисторах и типа, второй инвертор 14, при этом дифференциальный каскад, усилитель

10 с общим источником, первый инвертор

11 последовательно соединены, затвор первого 5 транзистора дифференциального каскада является соответственно неинвертирующим, а затвор второго транзистора 6 инвертирующим входами компаратора, а истоки первого 5 и второго

6 транзисторов объединены и подключены к выходу генератора тока 7 на третьем транзисторе р типа, затвор которого соединен с источником 1 управляющего напряжения, сток первого 5 транзистора соединен с входом отражателя тока, выполненного на нагрузочных транзисторах 8, 9. сток первого транзистора 5 соединен также с первым выходом отражателя тока 3 элемента смещения, а вход отражателя -:ока 3 соединен с выходом генератора тока 2 элемента смещения на транзисторе р типа, затвор которого подключен к источнику 1 уп5

50

45 равляющего напряжения, исток nepsoro выходного транзистора отражателя тока 3 подключен к стоку. транзистора и типа nepeoro ключа 4, исток и подложка которого подключены к общей шине, а затвор к выходу первого 11 мнвертора и соответственно к выходу компаратора. сток второго 12 выходного транзистора является вторым выходом отражателя тока и соединен со стоком второго транзистора р типа 6 дифференциального каскада, затвор с входом отражателя тока 3, в сток со стоком транзистора 13 второго ключа, исток и подложка которого соединены с общей шиной, в затвор с выходом второго инвертора 14, вход которого соединен с выходом первого инвертора 11 и соответственно с выходом компаратора.

КМПД компвратор работает следующим образом.

Предположим, что напряжение на инвертирующем входе компаратора "-" монотонно возрастает от очень малого или нулевого значения, а на неинвертирующий вход "+" подается опорное напряжение, задающее порог компаратора (см.фиг,2б). При этом сигналом высокого уровня с выхода компаратора открыт первый ключ 4, через который иэ инверсного выхода дифференциального каскада компаратора вытекает ток, определяемый током генератора тока 2 и соотношением размеров входного транзистора и первого выходного транзистора отражателя тока 3, что эквивалентно увеличению опорного напряжения на неинвертирующем входе компаратора Од на величину напряжения Ur 1!/gm, где 11— вытекающий ток с инверсного выхода дифференциального каскада через первый выходной транзистор токового отражателя 3, g — крутизна характеристик входных транзисторов 5. 6 дифференциального каскада.

При этом второй 13 ключ сигналом низкого уровня с.выхода второго инвертора 14 закрыт. Когда напряжение иа инверсном (см.фиг,2б) входе компарвторв превысит значение ОА+ Ur, тогда нв выходе компаратора появляется сигнал низкого уровня, закрывающий первый ключ 4 и через второй

14 инвертор открывающий второй ключ t3. через которыЯ иэ прямого выхода дифференциального каскадв компараторв вытекает ток, onðåäåëÿåìûÈ током генератора тока

2 и соотношением размеров входного транзистора и второго выходного транзистора отражателя тока 3, что эквивалентно уменьшению опорного напряжения на неинвертирующем входе компаратора Од на величину

Ог - 1г/gm, где !g вытекающий ток с прямого выхода дифференциального каскада че2001510 рез второй выходной транзистор токового отражаетля 3, gm — крутизна характеристик входных транзисторов 5, 6 дифференциального каскада. Далее когда при монотонном уменьшении сигнала нв инверсном входе компаратора "-" произойдет до значения Од — Ur тогда на выходе компаратора появляется сигнал высокого уровня, открывающий первый ключ 4 и через второй 14 инвертор закрывающий второй ключ 13 и компаратор попадает в исходный участок передаточной характеристики (см.фиг.2б), Для симметричного гистереэиса

О - Ur

Формула изобретения

KoMflAPAT0p, выполненный на полевых транзисторах, содержащий источник управляющего напряжения, элемент смещения, состоящий из генератора тока, отражателя тока и ключа, а также последовательноо соединенные дифференциальный каскад, усилитель с общим истоком и первый инвертор, при этом дифференциальный каскад выполнен нв первом и втором транзисторах р-типа, затвор первого из которых является соОтветственно неинвертирующим, а затвор второго инвертирующими входами компаратора, истоки первого и второго транзисторов объединены и подключены к выходу генератора тока дифференциального каскада на третьем транзисторе р-типа, затвор которого соединен с входом йсточника управляющего напряжения, а нагрузкой дифференциального каскада являются нагруэочные транзисторы п-типа, затворы которых объединены и подключены к стоку первого транзистора и к первому выходу отражателя тока элемента смещения, выполненного на транзисторах h-типа, а вход отражателя тока соединен с выходом генеТаким образом, в заявленном устройстве реализован двухсторонний гистерезис со следующей функцией преобразования:

0; - 1, при UA > Ue+ Ог:

5 Qi-О, при Од < Ов — Ог;

Gt 0!-1 при Ов — Ог UA < Us+ Ог.

Технический эффект от использования предлагаемого КМДП компаратора заключается в расширении функциональ10 ных воэможностей эа счет обеспечения двухстороннего гистерезиса. (56} Патент США М 4394587, кл. Н 03 К 5/24, 1983, ратора тока элемента смещения на тп.. чзисторе р-типа, затвор которого подключен к входу источника управляющего напряжения. а исток первого выходного транзистора отражателя тока элемента смещения подключен к стоку транзистора и-типа первого ключа, исток и подложка KQTopolQ подключены к общей шине, а затвор к выZ5 ходу первого инвертора и соответственно к выходу компаратора. шину источника напряжения, отличающийся тем, что, с целью расширения функциональных возможностей эа счет обеспечения двустороннего

3р гистереэиса, в него введены второй выходной транзистор отражателя токе, второй ключ на транзисторах п-типа, второй инвертор, причем сток второго выходного транзистора является вторым выходом от35 ражателя тока и соединен со стоком второго транзистора р-типа дифференциального каскада, затвор - с входом отражателя тока. а исток - со стоком транзистора втЬрого ключа, исток и подложка которого соеди4О нены с общей шиной, а затвор - с выходом второго инвертора, вход которого соединен с выходом первого инвертора и соответственно с выходом компаратора, 2001510

d8 г2

Составитель В.Богатырев

Редактор Т.Никольская Техред М,Моргентал - Корректор А.Обручар

Тираж Подписмое

НПО "Поиск Роспатента

113035, Москва, Ж-35, Раушская наб., 4/5

Заказ 3132

Производственно-издательский комбинат "Патент". г. Умгород, ул.Гагарина. 101