Делитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

2022I6

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 22.X.1966 (№ 1108812/26-9) с присоединением заявки №

Кл. 21ат, 36/02

МПК H 03k

УДК 621.374.4(088.8) Приоритет

Опубликовано 14 1Х.1967. Бюллетень . 4 19

Дата опубликования описания 27.Х1.1967

Комитет по делам изобретений и открытий при Совете Министров

СССР

Авторы изобретения

Л. А, Дубицкий и E. M. Шеремет

Львовское конструкторское бюро

Заявитель

ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЧ И1ЧПУЛЬСОВ

Известные делители частоты следовашгя импульсов содержат ждущий мультивибратор с коллекторно-базовыми связями и эмпттерпым повторителем в цепи заряда времязадающего конденсатора.

Недостатком этих устройств является пониженная максимальная частота входных импульсов и малые пределы изменения длительности и сква>кности выходных импульсов.

Предлагаемое устройство отличается от известных тем, что последовательно с разрядным сопротивлением времязадающего конде: >сатора включен стабилитрон. Катод его подключен между базой нормально открытого транзистора и обкладкой конденсатора, а»сжду анодом стабилитрона и базой нормально закрытого транзистора включен делитель нап р яжепи я.

Делитель выполнен HB x cOIIpOTHBëåíèëх, к общей точке которых подключен катод диода. Анод его соединен с коллектором нормально закрытого транзистора.

Это позволяет повысить максимальную частоту входных импучьсов и расширить пределы изменения длительности и скважности выходных импульсов.

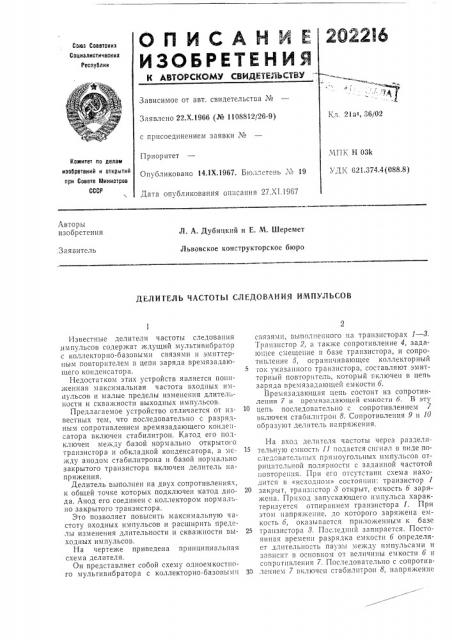

На чертеже приведена принципиальная схема делителя.

Он представляет собой схему одноемкостного мульгивибратора с коллекторно-базовымп связями, выполненного на транзисторах 1 — 8.

Транзистор 2, а также сопротивление 4, задаюгцее смещение в базе транзистора, и сопротивление 5, ограничивающее коллекторный ток указанного транзистора, составляют эмиттерный повторитель, который t:.êëî÷åí в цепь заряда времязадающей емкости 6.

Бремязадающая цепь состоит из сопротивлепия 7 и времязадающей емкости 6. В эту

10 цепь последовательно с сопротивлением 7 включен стабплптрон 8. Сопротивления 9 и 10 образуют делитель напряжения.

На вход делителя частоты через разделительную емкость 11 подается сигнал в виде последовательных прямоугольных импульсов отрицательной полярности с заданной частотой повторения. При его отсутствии схема находится в «исходном» состоянии: транзистор 1

20 закрыт, транзистор 8 открыт, емкость 6 заряжена. Приход запускающего импульса характеризуется отпиранием транзистора 1. При этом напряжение, до которого заряжена емкость 6, оказывается приложенным к базе

25 транзистора 8. Последний запирается. Постоянная времени разрядка емкости 6 определяет длительность паузы между импульсами и зависит в основном от величины емкости 6 и сопротивления 7. Последовательно с сопротив30 пением 7 включен стаби Ièòðон 8, напряженпе

202216 стабилизации которого подбирается близким к напряжению коллекторного.питания.

IpII отсутств11И Зс1Г1ускаlощих и. !пульсов !!11 пряжение на стабилитроне убывает до тех пор, пока не приблизится к напряжению коллекторпого питания. Сопротивление стабил;1трона при этом резко возрастает и дальнеиший разряд емкости б осуществляется с боль. щей постоянной времени, в результате чего пауза»lежду имп i ьсами ЗначиTcл1>110 возраLтает.

При наличии запускающих импульсов указанное состоя!!не отсутствует, поскольку опрокидывание схемы происходит при напряжении на стабилитроне, превращающем напряжение стабилизации. Разрядный ток емкости

6, а, следовательно, и коллекторный ток транзистора 1, при этом достаточно ьелик. Следует отметить, что в описываемом устройстве величина разрядного сопротивления 7 выбрана меньше, чем в и3IIecTII! Ix устройствах, вследствие чего емкость б разряжается большим разрядным токо.i. Зто, а также вышеотмеченное обстоятельство, свидетельствуют о малой стегени насыщения транзистора 1, что ускоряет опрокидывание схемы и повышает максимальную частоту деления. Опрокидывание схемы осуществляется запускающими импульсами, поступающими на базу транзистора 8 двум» различными путями. зо

Первый путь представляет собой цепь, состоящую из емкости 11, сопротивления 10 и стабилитрона 8. При напряжении на е IKocòè б, превышающем амплитуду импульсов, прошедших на катод стабилитрона 8, транзистор З5

8 надежно закрыт, и емкость 6 разряжается.

Разряд продолжается до момента, при котором осуществляется равенство указанных напряжений, и схема опрокидывается. На коллекторе транзистора Тб формируется перед- 4О ний фронт импульса. Следует отметить, что )3 данном случае переднему фронту импульса, как правило, предшествуют характерные всплески, причиной которых является кратковременное отпирание транзистора Тб запуска- 45 ющими импульсами. По окончании действия запускающего импульса напряжение, запасенное на емкости С4, запирает транзистор Тб, схема возвращается в прежнее состояние, н емкость С4 продолжает разряжаться до при- 50 хода следующего запускающего импульса.

Второй путь представляет собой цепь, состоящую из емкости 11, диода 12, сопротивления 4 и емкости б. Запускающие импульсы, поступающие на вход настоящей схемы, диф- 55 ференцируются, причем постоянная времени дифференцирующей цепи имеет разные величины при формировании отрицательной и положительной полуволн. Формирование отр ii гсльной полуIIoëilû осуществляется цепью, посто;1ИII, 1» В!земpIIII l

Положительная полуволна передается па базу транзистора 8 через стабилитрон 8, но на работу схемы существенного влияния ие оказывает. Опрокидывание схемы осуществляется совместным дейстьием двух импульсов: импульса запуска, переданного це пьнз элементов 11, 10, 8 на базу транзистора 8, и отрицательной полуволны продифференцировапного импульса запуска. Совместное действие указанных импульсов, а также регулировка их амплитуд посредством изменения сопротивления 10 позволяет полностью уничтозкить всплески, предшествующие переднему фронту выходного им!пульса.

В результате использования указанных импульсов для опрокидывания схемы уменьшается время опрокидывания и повышается максимальная частота деления.

Предмет изобретения

Делитель частоты следования импульсов, содержащий ждущий мульп;вибратор с коллскторно-базовыми связями ri эмиттерным повторителем в цепи заряда времязадающего конденсатора, отлича1ощийся тем, что, с целью повышения максимальной частоты входных импульсов и расширения пределов изменения длительности и скважности выходных импульсов, последовательно с разрядным сопротивлением времязадающего конденсатора включен стабилитрон, катод которого соединен с обкладкой упомянутого конденсатора и базой нормально открытого транзистора, а мезкду анодом стабилитрона и базой нормально закрытого транзистора включен делитель напрязкения на двух сопротивлениях, к общей точке которых подключен катод диода, анод которого соединен с коллектором нормально закрытого транзистора.

Составитель 3. Гилииская

I едактор Н. Джарагетти Текред Л. Я, Бриккер

Корректоры: Л. В. Каделяева и Н, И. Быстрова

Заказ 3622!9 Тиранс 535 Подписное

ЦНИИПИ Когяптета по дслаги изобретений и открытий прп Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2