Устройство для определения наибольшей разности

Иллюстрации

Показать всеРеферат

20402!

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 16.VIII.1965 (№ 1023028/26-24) с присоединением заявки №

Приоритет

Опубликовано 09.Х.1967. Бюллетень № 21

Дата опубликования описания 3.1.1968

Кл. 42m, 14

МПК G 06f

УДК 681.325.66:511.123 (088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Авторы изобретения В. Е. Злобинский, Ю. Л. Урин, В. Х. Цингауз и Ю. Д. Полисский

Заявитель

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАИБОЛЬШЕЙ РАЗНОСТИ

НЕСКОЛЬКИХ ЧИСЕЛ

Известны устройства для определения наибольшей разности нескольких (k) двоичных и-разрядных чисел, содержащие реверсивные счетчики-регистры для хранения сравниваемых чисел, логические схемы управления, генератор импульсов и счетчик наибольшей разности.

Предложенное устройство отличается от известных тем, что оно содержит и+1+2 логические схемы «ИЛИ», 1+1 логическую схему «И», по k логических элементов

«ЗАПРЕТ», дифференцирующих цепочек, инверторов и элемент задержки; причем ко входам каждой из и схем «ИЛИ» первой группы подсоединены инверсные выходы одноименных разрядов всех kрегистров чисел,,ко входам каждой из k схем «ИЛИ» второй группы подключены прямые выходы всех разрядов одноименных регистров чисел, выходы каждой схемы «ИЛИ» первой группы соединены с запрещающим входом одноименного элемента «ЗАПРЕТ»: к возбуждающим входам всех элементов «ЗАПРЕТ» и входу элемента задержки подключен источник сигнала упраьления; выходы элементов «ЗАГ1РЕТ» через дифференцирующие цепочки соединены с нулевыми входами одноименных разрядов регистров всех чисел; выход элемента задержки подключен ко всем k схемам «И», соединенным с вычитающими входами всех регистров чисел, к которым подсоединены также выход генератора импульсов и выходы одноименных схем «ИЛИ» второй группы; выходы этих схем подключены ко

5 входам (тт+1с+1)-й схемы «ИЛИ» и через инверторы ко входам (а+ k+2) -й схемы

«ИЛИ», выходы которых соединены со входами ф+1)-й схемы «И», куда подсоединен также и выход генератора импульсов, а выход

10 (/А+1) -й схемы «И» подключен к регистру наибольшей разности.

Это упрощает схему устройства и повышает его быстродействие.

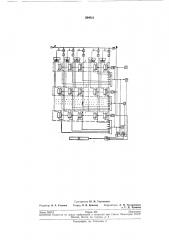

Блок-схема устройства приведена на чер15 т еже.

Устройство содержит регистры 1 сравниваемых чисел с вычитающими счетными входами, логические схемы «ИЛИ» 2 первой группы, логические схемы «ИЛИ» 8 второй

20 группы, элементы «ЗАПРЕТ» 4, дифференцирующие цепочки 5, нулевые входы б разрядов регистров, элемент 7 задержки, логические схемы «И» 8, а+1+1 и а+1+2 соответственно логические схемы «ИЛИ» 9 и 10, генератор

25 11 импульсов, клемму 12 подключения источника управляющего сигнала, инверторы 13, (1+1) схему 14 «И», счетчик 15 наибольшей разности.

Устройство работает следующим образом.

3О Сигнал разрешения сравнения поступает на

204021 клемму 12. На запрещающие входы элементов

«ЗАПРЕТ» 4 приходит сигнал со схем «ИЛИ»

2, объединяющих инверсные выходы триггеров одноименных разрядов всех чисел.

При наличии нуля хотя бы в одном из этих триггеров появляется сигнал на выходе соответствующей схемы 2, и через одноименную схему 4 сигнал не проходит, B этом случае, когда во всех триггерах данного разряда записаны единицы, отсутствуют сигналы на входах соответствующей схемы 2 «ИЛИ» и сигнал на тормозящем входе схемы 4. На выходе схемы 4 появляется сигнал, который через дифференцирующую цепочку 5 сбрасывает в нулевое состояние все триггеры данного разряда. Управляющий сигнал со схемы 5 через линию задержки 7 подается также на схемы совпадения 8, разрешающие прохождение вычитающих импульсов от генератора 11 в регистры 1. В тот момент, когда наименьшее из чисел обратится в нуль, прекращается подача вычитающих импульсов в регистр этого числа и исчезает сигнал с выхода одноименной схемы <ИЛИ» 8. На выходе инвертора 18 этого числа появляется сигнал. Через схему «ИЛИ»

10 он проходит на схему «И» 14 и разрешает прохождение импульсов от генератора импульсов 11 в счетчик 15 наибольшей разности. На третий вход схемы «И» 14 поступает в это время сигнал со схемы «ИЛИ» 9. Этот сигнал исчезает при обращении в нуль содержимого всех регистров сравниваемых чисел.

Тогда исчезает сигнал с одного из входов схемы 14 и запрещается прохождение импульсов в счетчик наибольшей разности. Так как сигналом начала подсчета импульсов в счетчике

15 служит момент обращения в нуль наименьшего числа, а концом сравнения является обращение в нуль всех регистров, то по окончании сравнения в счетчике 15 будет записана наибольшая разность сравниваемых чисел..

Устройство может быть применено в специализированных системах автоматики для определения максимального разброса какихлибо параметров, для сравнения чисел, записанных в двоичном коде.

Предмет изобретения

Устройство для определения наибольшей разности нескольких чисел, содержащее реверсивные счетчики-регистры для хранения сравниваемых чисел, логические схемы управления, 10 генератор импульсов и счетчик наибольшей разности, отличающееся тем, что, с целью упрощения схемы и повышения быстродействия, оно содержит n+k+2 логические схемы

«ИЛИ», 1+1 логическую схему «И», по и лот5 гических элементов «ЗАПРЕТ», дифференцирующих цепочек, инверторов и элемент задержки, причем ко входам каждой из п схем

«ИЛИ» первой группы подсоединены инверсные выходы одноименных разрядов всех Й

20 регистров чисел, ко входам каждой из Й схем «ИЛИ» второй группы подключены прямые выходы всех разрядов одноименных регистров чисел, выходы каждой схемы «ИЛИ» первой группы соединены с запрещающим

25 входом одноименного элемента «ЗАПРЕТ», к возбуждающим входам всех элементов «3АПРЕТ» и входу элемента задержки подключен источник сигнала управления, выходы эле ментов «ЗАПРЕТ» через дифференцирующие

30 цепочки соединены с нулевыми входами одноименных разрядов регистров всех чисел, выход элемента задержки подключен ко всем k схемам «И», соединенным с вычитающими входами всех регистров чисел, к которым подЗ5 соединены также выход генератора импульсов и выходы одноименных схем «ИЛИ» второй группы, выходы этих схем подключены ко входам (u+k+1)-й схемы «ИЛИ» и через инзерторы ко входам (n+k+2)-й схемы «ИЛ11», 40 выходы которых соединены со входами (k+1)-й схемы «И», куда подсоединен также н выход генератора импульсов, а выход (k+1)-й схемы «И» подключен к регистру наибсльшей разности, 204021

Составитель Ю. М. Торгоненко

Редактор Л. А. Утехина Техред Л. Я. Бриккер Корректоры: А. П. Татаринцева и T. Д. Чунаева

Заказ 3883!7 Тираж 535 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Советс Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2