Многокаскадный делитель частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ГА

I,ë. 21е, 36/10

Заявлено 16Х.1966 (№ !076345/26-10) с присоединением заявки ¹

Приоритет

Опубликовано 08.Х11.1967. Бюллетень М 1

МПК 6 Olr

: ДК 621.374.4(088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Дата опубликования описания 12.11.19á8

Авторы изобре-.ения

Л. С. Ситников, Д. Л. Утяков и С. E. 1оковенко

Заявитель

Завод «Точэлектроприоор»

МНОГОКАСКАДНЬ1й ДЕЛИТЕЛЬ ЧАСТОТЫ

Известные многокаскадные делители частоты выполнены в виде последовательно соединенных емкостных накопительных счетчиков.

Однако при уменьшении частоты следования входных импульсов стабильность работы этих счетчиков уменьшается. Путем увеличения емкостей накопителя удается обеспечить частоту следования выходных импульсов до 50 гт1.

При этом все каскады многоразрядного делителя различаются параметрами деталей накопителя, т. е. теряется унификация каскадов.

Однако при отказе от унификации в описанных делителях невозможно обеспечить сколь угодно низкие частоты следования выходных и мпул ьс о в.

Предлагаемый многокаскадный делитель частоты для устранения этих недостатков имеет делитель, снабженный логическими схемами обеспечения фазоимпульсного режима работы накопителей («ИЛИ», «И»), а также схемой выработки сдвинутых последовательностей импульсов, один из выходов которой подсоединен ко входу первого каскада делителя, а другой выход — к одному из входов всех схем

«ИЛИ». При этом вторые входы схем «ИЛИ» соединены с выходами накопительных счетчиков предыдущих каскадов через схемы «И» или непосредственно, а вторые входы схем

«И» — к выходу первого каскада делителя либо к выходу схемы «И» предыдущего каскада.

Кроме того, делитель снабжен двухтактным генератором импульсов, синхронизатором, схемой задержки источником импульсов опорной последовательности и схемами разновременного совпадения, причем первый выход двухтактного генератора подсоединен к одному из входов всех схем «ИЛИ», а второй через источ10 ник импульсов опорной последовательности— к одному из входов синхронизатора. Второй вход последнего через схему задержки соединен с зажимом входных импульсов. Первые входы схем разновременного совпадения под15 ключепы к зажиму либо к выходу аналогичной схемы предыдущего каскада, а вторые входы через схемы «И» соответствующих каскадов — с выходом синхронизатора, при этом его выход подключен ко входу схемы «ИЛИ»

20 первого каскада.

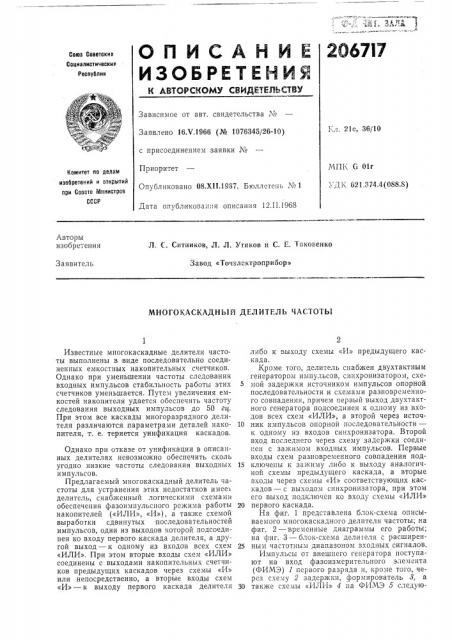

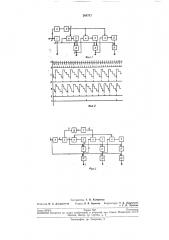

На фиг. 1 представлена блок-схема описываемого многокаскадного делителя частоты; на фиг. 2 — временные диаграммы его работы; на фиг. 3 — блок-схема делителя с расширен25 ным частотным диапазоном входных сигналов.

Импульсы от внешнего генератора поступают на вход фазоизмерительного элемента (ФИМЭ) 1 первого разряда и, кроме того, через схему 2 задержки, формирователь 3, а

30 также схемы «ИЛИ» 4 на ФИМЭ 5 следую206717

10 щих разрядов. Выходные импульсы ФИМЭ 1 поступают на первый выход делителя и все схемы б совпадения, выход любой из которых также является одним из выходов делителя.

Благодаря наличию схемы 2 задержки импульсы, поступающие на входы первой схемы

«ИЛИ» 4 с выходов формирователя 8 и ячейки 1, не совпадают по времени. Поэтому поступление каждого импульса с выхода ячейки

1 вызывает сдвиг фазы выходных импульсов

ФИМЭ 5 следующего разряда на один период следования входных импульсов. Приход десятого импульса с выхода ячейки 1 вызовет срабатывание ФИМЭ 5 следующего разряда, синфазное со срабатыванием ячейки 1. В результате на выходе первой схемы б совпадения импульсы следуют с частотои —, где

Увх частота следования входных импульсов.

Аналогичным образом функционируют следующие разряды, причем каждый разряд работает на достаточно высокой частоте (на частоте входных импульсов), а делит только импульсы, поступающие с выхода предыдущего разряда.

Поскольку разрядность делителя не имеет принципиальных ограничений, можно получить выходные импульсы со сколь угодно низкой частотой следования. Времснные диаграммы напряжений (см. фиг. 2) иллюстрируют работу делителя. Здесь а — входные импульсы; b— импульсы на выходе формирователя 3; с — напряжение на накопительном конденсаторе импульсы ячейки 1; а — выходные импульсы ячейки 1; — е напряжение на накопительном конденсаторе ячейки 5 следующего разряда;

f — импульсы на выходе ячейки 5; g — импульсы на выходе первой схемы б совпадения.

С целью упрощения временные диаграммы построены для случая, когда коэффициент деления каждого разряда принят равным четырем. Делители могут применяться в тех случаях, когда на вход поступает фиксированная или же меняющаяся в сравнительно небольших пределах (не более чем в 5 — 10 раз) частота, например, в генераторах меток времени, вторичных эталонах частоты и т. д.

В тех случаях, когда требуется делить частоту следования входных импульсов, меняющуюся в широком диапазоне частот, начиная с нуля (такая задача возникает, например, в

15 го г5

Зо

50 цифровых частотомерах), целесообразно использовать модифицированную блок-схему, представленную на фиг. 3.

Входные импульсы поступают на схему 8 задержки, а также на схемы 10 разновременного совпадения. Импульсы с одного из выходов двухтактного генератора 7 подаются на схемы 4 сборки всех разрядов устройства, а на опорный элемент 50 поступают импульсы со второго выхода генератора. Выходные импульсы ячейки 5 подаются на синхронизатор

9 в качестве синхронизирующих.

П р ед м е т изобретения

1. Многокаскадный делитель частоты, содержащий накопительные счетчики, отличающийся тем, что, с целью обеспечения унификации каскадов делителя и возможности получения сколь угодно низких частот следования выходных импульсов, а также расширения частотного диапазона входных импульсов, делитель снабжен логическими схемами обеспечения фазоимпульсного режима работы накопителей («ИЛИ», «И»), двухтактным генератором импульсов, синхронизатором, схемой задержки, источником импульсов опорной последовательности, схемами разновременного совпадения и схемой выработки сдвинутых последовательностей импульсов, один из выходов которой подсоединен ко входу первого каскада делителя, а другой выход — к одному из входов всех схем «ИЛИ», при этом вторые входы схем

«ИЛИ» соединены с выходами накопительных счетчиков предыдущих каскадов через схемы

«И», одни входы которых подсоединены к выходу первого каскада делителя, а вторые входы — к выходам накопительных счетчиков.

2. Делитель частоты по п, 1, отличающийся тем, что первый выход двухтактного генератора подсоединен к одному из входов всех схем «ИЛИ», а второй — через источник импульсов опорной последовательности с одним из входов синхронизатора, второй вход последнего через схему задержки соединен с зажимом входных импульсов; первые входы схем одновременного совпадения подключены к упомянутому зажиму, а их вторые входы через схемы «И» соответствующих каскадов соединены с выходом синхронизатора, при этом его выход подключен ко входу схемы «ИЛИ» первого каскада.

206717

Фиг.1

Составитель Г. Н. Кучеренко

Редактор Н. A. Джарагетти Техред Л. Я. Бриккер Корректоры: T. Б. Лаврухина и Т Д Чунаева

Заказ 4670/3 Тираж 530 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий прп Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2