Многоканальный цифровой коррелятор

Иллюстрации

Показать всеРеферат

206908

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сова Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 22.Xl 1.1966 (№ 1120661/26-24) Кл. 42m, 14 с присоединением заявки №

МПК 4 061 хтДК 681.325.36(088.8) Приоритет

Опубликовано 08.Xll.1967. Бюллетень № 1

Дата опубликования описания 25,I.1968

Номитет по делам иаобретеиий и открытий ри Совете Министров

СССР

Автор изобретения в. и. ю

Заяьитель

Институт автоматики и электрометрии Сибирского отделения

АН СССР

МНОГОКАНАЛЪНЫЙ ЦИФРОВОЙ КОРРЕЛЯТОР

Предмет изобретения

В известных многоканальных цифровых корреляторах, содержащих аналого-цифровые преобразователи, устройство умножения, группу коммутируемых накопительных элементов и устройство синхронизации, требуются более длинные реализации случайного процесса, чем это принципиально необходимо.

Для повышения быстродействия в предлагаемом корреляторс использован комбинированный способ задержки: путем запоминания дискреты сигнала и ее переме ценил в сдвиговом регистре. При этом сдвиговый регистр имеег число каскадов больше одного, но меньше числа накопительных элементов.

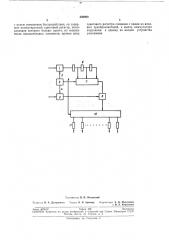

На чертеже показана блок-схема описываемого коррелятора.

Он содержит два входных аналого-цифровых преобразователя 1 и 2, к которым подключены выходы 8 и 4 синхронизатора 5. Выход преобразователя связан с первым каскадом сдвигового регистра б, BbIxoäû всех каскадов которого переключаются коммутатором

7. Его управляющий вход соединен с выходом 8 синхронизатора 5, а выход подключен и устройству 9 перемно;кения, связанному вторым входом с аналого-цифровым преобразователем 2. Устройство перемножения через дополнительный комму-,атор 1D связано с нак0IIHTP. IHiIH 11, UHC. O KGTOpbIX pBBkIO вычисляемых точек корреляционной функции.

Последняя вычисляется в течение определенного числа циклов работы. В начале каждого цикла происходит измерение входного сигнала преобразователем 1, измерение второго сигнала преобразователем 2 и сдвиг в регистре б, причем в первый каскад регистра записывается измеренное значение сигнала.

Одновременно открываются первые каналы коммутаторов 7 и 10, Вследствие этого на

10 умножитель поступают измеренные значения сигналов с одинаковыми аргументами, а их произведения накапливаются в первом накопителе.

В последующих циклах работа протекает

1 аналогично, но второй сигнал подается на умножитель с фиксированным аргументом, а первый благодаря срабатыванию регистра каждый цикл передается задержанным на время, пропорциональное количеству циклов. 0

Многоканальный цифровой коррелятор с не25 посредственным вводом данных для стациопарных на интервале наблюдения процессов, содержащий аналого-цифровые преобразователи, устройство умножения, группу коммутируемых накопительных элементов и устрой30 с1во синхронизации, отличающийся тем, что, 206908

Составитель В, H. Жовинский

Редактор Н. А. Джарагетти Текред Л. Я. Бриккер Корректоры: Е. Ф. Полионова и И. Л. Кириллова

Заказ 4678/12 Тираж 535 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типографии, пр. Сапунова, 2 с целью повышения быстродействия, он содержит коммутируемый сдвиговый регистр, число каскадов которого больше одного, но меньше числа накопительных элементов, причем вход сдвигового регистра соединен с одним из входных преобразователей, а выход коммутатора подключен к одному из входов устройства умножения.