Десятичный счетчик

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Со сз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Кл. 42m, 14

21а>, 36/22

Заявлено 10.1.1967 (№ 1125376/26-24) с присоединением заявки №

Приоритет

Опубликовано 22.XII.1967. Бюллетень № 2

Дата опубликования описания 29.1I.1968

МПК G 061

Н 03k

УД К 621.374.32.055 (088.8) Котситет по делвте изобретений и открытий при Совете Министров

CCCP

Авторы изобретения

А. С. Очков, В. А. Яиочкин и Б. С. Мошкаров

Заявитель

ДЕСЯТИЧНЫЙ СЧЕТЧИК

В вычислительной технике для выполнения вычитания двух групп импульсов обычно применяются двоично-десятичные счетчики на триггерах, схемах совпадения в дешифраторе.

В зависимости от направления счета используются те или иные цепи, что снижает быстродействие таких счетчиков.

Цель изобретения — построение такой схемы счетчика, которая обеспечивала бы вычитание двух групп импульсов без удлинения пути прохождения импульсов в счетчике.

В предлагаемом счетчике и-ный выход дешифратора соединен со входом схемы совпадения, выход которой подключен к 9-п-ому выходу дешифратора, вторые входы схем совпадения объединены и связаны с управляющей шиной.

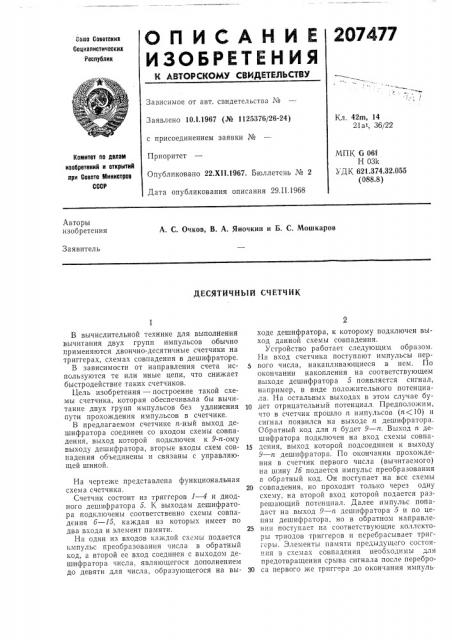

На чертеже представлена функциональная схема счетчика.

Счетчик состоит из триггеров 1 — 4 и диодного дешифратора 5. К выходам дешифратор а подключены соответственно схемы совпадения б — 15, каждая из которых имеет по два входа и элемент памяти.

На один из входов каждой схемы подается импульс преобразования числа в обратный код, а второй ее вход соединен с выходом дешифратора числа, являющегося дополнением до девяти для числа, образующегося на выходе дешифратора, к которому подключен выход данной схемы совпадения.

Устройство работает следующим образом, На вход счетчика поступают импульсы первого числа, накапливающиеся в нем. По окончании накопления на соответствующем выходе дешифратора 5 появляется сигнал, например, в виде полон ительного потенциала. На остальных выхсдах в этом случае бу10 дет отрицательный потенциал. Предположим, что в счетчик прошло >г импульсов (n(10) и сигнал появился на выходе и дешифратора.

Обратный код для и будет 9 — гг. Выход и дешифратора подключен на вход схемы совпа15 дения, выход которой подсоединен к выходу

i — и дешифратора. По окончании прохождения в счетчик первого числа (вычитаемого) на шину 1б подается импульс преобразования в обратный код. Он поступает на все схемы

20 совпадения, но проходит только через одну схему, на второй вход которой подается разрешающий потенциал. Далее импульс попадаст на выход 9 — n дешифратора 5 и по цепям дешифратора, но в обратном направле25 нии поступает на соответствующие коллекторы триодов триггеров и перебрасывает триггc .pbl. Элементы памяти предыдущего сОстОЛния в схемах совпадения необходимы для предотвращения срыва сигнала после перебро30 са первого же триггера до окончания импуль

207477

1б

Составитель Л. В. Скобелева

Редактор П. А. Вербова Техред Т. П. Курилко Корректоры: T. П, Лаврухина и В. В. Крылова

Заказ 34/15 Тираж 530 Подписное

ЦНИИПИ Комитста по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2

3 са преобразования в обратный код. После переброса триггеров сигнал дешифратора появляется на выходе 9 — а. На счетчике устанавливается обратный код числа. Затем на вход счетчика подаются импульсы второго числа (уменьшаемого). Если это число больше первого, то счетчик переполняется, сбрасывается на О (с выдачей сигнала переноса в следующий разряд) и заполняется вновь на величину разности этих двух чисел без единицы. Устройство для добавления единицы при операциях в обратном коде во многих случаях, например в измерительных приборах, необязательно, так как эта ошибка систематическая и может учитываться другими способами.

Если второе число меньше первого, разность получается в обратном коде и при необходимости ее можно преобразовать в прямой код.

Таким образом, предлагаемый счетчик обеспечивает вычитание двух чисел и сохраняет быстродействие обычного нереверсивного счетчика благодаря тому, что добавочные коммутирующие элементы (схемы совпадения), обеспечивающие преобразование числа

s p обратный код, и, следовательно, вычитание, подключены к выходам дешифратора, а соединение счетных триггеров сохраняется таким же, как у обычного нереверсивного счетчика.

Схема совпадения может быть собрана без

10 применения транзисторов, например на конденсаторе, сопротивлении и диоде.

Предмет изобретения

Десятичный счетчик, содержащий триггеры, 15 схемы совпадения и дешифратор, отличающийся тем, что, с целью расширения функциональных возможностей, и-ный выход дешифратора соединен со входом схемы совпадения, выход которой подключен к 9 — и-ному

20 выходу дешифратора, вторые входы схем совпадения объединены и связаны с управляющей шиной.