Накапливающий сумматор с фиксацией ошибкипереноса

Иллюстрации

Показать всеРеферат

208338

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистическик

Респуйлин

Зависимое от авт. свидетельства №

Заявлено 22.XI.1966 (№ 1115658/26-24) с присоединением заявки №

Кл. 42m, 14

МПК G 061

УДК 681.325.55:

:681.335.4 (088.8) Приоритет

Комитет по делам изобретений и открытий при Совете Мииистрсв

СССР

Опубликовано 29.XII.1967. Бюллетень № 3

Дата опубликования описания 19.III.1968

Авторы изобретения

М. В. Чхеидзе и Г. Г. Ладария

Заявитель Тбилисский филиал Всесоюзного научно-исследовательского института метрологии им. Д. И. Менделеева

НА КАП Л И BAIOI È Й СУММАТОР С Ф И КСАЦИ ЕЙ ОШ И Б KH

ПЕРЕНОСА

Известны накапливающие сумматоры с фиксацией ошибки переноса, содержащие триггерный регистр с линиями задержки, дифференцирующими цепочками и логическими элементами.

Предложенный сумматор отличается от известных тем, что в нем единичные выходы триггеров всех разрядов сумматора, кроме старшего и младшего, и нулевые выходы триггеров всех разрядов, кроме младшего, через дифференцирующие цепочки, схемы совпадений и собирательные схемы подключены ко входам схем неравнозначности, вторые входы каждой из которых через линии задержки присоединены к выходам собирательных схем в цепь сквозного переноса, принадлежащих соседнему младшему разряду сумматора, а выходы через собирательную схему:подключены к выходу схемы фиксации ошибки переноса.

Это позволило повысить достоверность выполнения операций суммирования за счет контроля процесса распространения переноса.

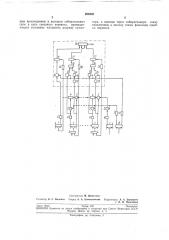

На чертеже приведена схема устройства.

Сумматор содержит триггеры 1, схемы совпадения 2 и 8, собирательные схемы 4 и 5 и дифференцирующие цепочки б. Схемы совпадения управляются сигналом, который образуется на выходе элемента (линии) задержки 7, подключенного к нулевому выходу триггера 8, Одновременно с засылкой в сумматор слагаемого, которое должно сложиться с его содержимым, на счетный вход триггера 8 должен подаваться импульс, переводящий его из нулевого положения в единичное. В результате на нулевом выходе триггера 8 происходит смена высокого уровня низким, однако линия задержки, которая рассчитана на время срабатывания элементов 2 и б, обеспечивает наличие высокого уровня на соответствующих входах элементов 2 до тех пор, пока первичные переносы не пройдут в цепь сквозного переноса. После этого высокий уровень с группы элементов 2 снимается, и схема сквозного распространения переносов блокируется от вторичных переносов.

Схема фиксации переноса обведена на чертеже пунктирной линией.

Сигнал переноса, который поступает в данный разряд сумматора, должен переключить триггер 1, соответствующий этому же разряду. Схема фиксации ошибки переноса

25 определяет тот случай, когда сигнал переноса, поступивший в данный разряд сумматора, не влечет за собой переключения триггера 1 соответствующего разряда сумматора, т. е. возникает ошибка в результате суммирова30 ния.

208338

Младший разряд сумматора не содержит элементов, входящих в схему фиксации ошибки переноса, поскольку в него не поступает сигнал переноса. К старшему разряду сумматора подключены дифференцирующая цепочка б, схема совпадения 9, управляемая от линии задержки 10, схема неравнозначности 11 и линия задержки 12, рассчитанная на сумму времен срабатывания триггера 1 и элемента б. 10

К остальным разрядам суммирующей схемы подключены иденгичные комбинационные схемы, которые в совокупности и создаюг собственно схему фиксации ошибки переноса совместно со схемой старшего разряда сумматора.

Схема фиксации ошибки переноса содержит на каждый разряд сумматора, кром» первого и последнего, один дифференцирующий элемент 18, схемы совпадения 14 и 15, собирательные схемы 16, схему неравнозначности 17 и линии задержки 18. Задержка каждой линии 18 рассчитана на сумму времен срабатывания элемента 5, триггера 1, элемента б или 18, схемы совпадения 14 или 15 и собирательной схемы 16, т, е. линия задержки 18 обеспечивает подачу сигнала на вход соответствующего ему элемента неравнозначности 17 одновременно с ожидаемым поступлением сигнала с выхода соответству- 50 ющей собирательной схемы 16.

Выходы всех элементов неравнозначности

17 подключены ко входу 19 сборки.

Перед началом работы в сумматоре может содержаться результат предыдущей опера- 35 ции, а триггер 8 находится всегда в нулевом положении. В результате высокий уровень с выхода линии задержки 7 поддерживается на соответствующих входах группы схем совпадения 2. 40

Поступление на сумматор числа, которое должно сложиться с его содержимым, сопровождается засылкой импульса на счетный вход триггера 8. Поскольку слагаемые поступают в триггерный регистр через счетные 45 входы триггеров, то вначале происходит поразрядное сложение по модулю 2 в каждом триггере 1. В случае, если какой-либо триг.гер 1 при этом переходит из единичного положения в нулевое, это фиксирует соответ- 50 ствующий дифференцир ующий элемент б, в результате чего в цепь сквозного переноса через соответствующую схему совпадения 2 поступает сигнал первичного переноса. Б этот момент триггер 8 уже опрокинут, однако 55 благодаря наличию линии задержки 7, подключенной к его нулевому выходу, высокий уровень поддерживается на соответствующих входах схем совпадения 2 до момента прохождения первичных переносов в цепь скво:- 60 ного переноса. После этого высокий уровеч, с группы вентилей схем совпадения 2 снимается, чем достигается блокировка цепи сквозного переноса от возможного проникновения в нее вторичных переносов, которые 65 могут возникнуть B результате реализации процесса распространения переносов.

Одновременно с этим высокий уровень, образовавшийся на единичном выходе триггера 8 и задержанный линией задержки 10 на время, необходимое для засылки первичных переносов в цепь сквозного переноса, передается на соответствующие входы схем совпадения 14 и 15 и снимает блокировку со схемы фиксации ошибки переноса.

Каждый сигнал переноса, поступающий в данный разряд сумматора через соответствующую собирательную схему 5, одновременно поступает через соответствующую линию задержки 18 в схему фиксации ошибки переноса. Сигнал переноса поступает на счетный вход соответствующего триггера 1 сумматора, триггер опрокидывается и переходит из нулевого положения в единичное или наоборот. Любой из этих случаев фиксируется дифференцирующими элементами б и 18, подключенными к выходам триггеров 1 сумматора.

Таким образом, в случае, если перенос, поступивший в данный разряд сумматора, опрокинул триггер 1, то этот факт зафиксирует один из двух дифференцирующих элементоз

6 или 18, подключенных к выходам данного триггера 1. Образовавшийся на выходе дифференцирующего элемента б или 18 сигнал через схему совпадения 14 или 15 и собирательную схему 16 поступает на один из выходов соответствующего элемента неравнозначности 17. Одновременно на второй вход того же элемента неравнозначности поступает сигнал с выхода линии задержки 18, в результате чего на его выходе сигнала не образуется. Если соответствующий триггер 1 сумматора не сработает, это будет зафиксировано соответствующим элементом неравнозначности 17, а сигнал, появившийся на выходе собирательной схемы 19, будет являться признаком того, что в сумматоре произошла ошибка в результате неполностью реализованного процесса распространения переноса.

Предмет изобретения

Накапливающий сумматор с фиксацией ошибки переноса, содержащий триггерный регистр с линиями задержки, дифференцирующими цепочками и логическими элементами, отличающийся тем, что, с целью повышения достоверности выполнения операций суммирования за счет контроля процесса распространения,переноса, в нем единичные выходы триггеров всех разрядов сумматора, кроме старшего и младшего, и нулевые выходы триггеров всех разрядов, кроме младшего, через дифференцирующие цепочки, схемы совпадений и собирательные схемы подключены ко входам схем неравнозначности, вторые входы каждой из которых через линии задер208338

Составитель М. Штильман

Редактор Б. С. Нанкина Техред А. А. Камышникова Корректоры: А. А. Березуева и Л. В. Наделяева

Заказ 190)2 Тираж 530 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 жки присоединены к выходам собирательных схем в цепь сквозного переноса, принадлежащих соседнему младшему разряду сумматора, а выходы через собирательную схему подключены к выходу схемы фиксации ошибки переноса.