Цифровое вычислительное устройство для решения рекуррентных уравнений

Иллюстрации

Показать всеРеферат

ОП И САНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

2О9030

4=jII чит. ЗАЛА

6оюа Советских

Социалиотичеоких

Реопублин

Зависимое от авт. свидетельства №вЂ”

Заявлено 14.11.1966 (№ 1056713/26-24) с присоединением заявки №вЂ”

Приоритет—

Опубликовано 17.1.1968. Бюллетень № 4

Дата опубликования описания 19.III.1968

Кл. 42m, 14

МПК G 061

УДК 681.14-523.8(ф88.8) Комитет па делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

Г. Ф. Луговой

Заявитель

Военно-воздушная инженерная ордена Ленина Краснознаменная академия им. проф. Н. Е. Жуковского

ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ

РЕКУРРЕНТНЫХ УРАВНЕНИЙ

Известны цифровые устройства для решения рекуррентных уравнений, содержащие запоминающее устройство, арифметическое устройство, устройство управления и устройство ввода-вывода.

Предлагаемое устройство отличается тем, что запоминающее устройство выполнено на сдвигающих регистрах, в разрядах которых хранится значение рекуррентно вычисляемых величин, выходы разрядов величин вплоть до и — 1 через вентили, связанные с устройством управления, соединены со входами множительного устройства выход множительного устройства соединен со входом накопительного сумматора, выход которого через вентиль, соединенный с устройством управления, связан со входом записи n-ro значения величины в запоминающее устройство.

Это позволяет увеличить быстродействие устройства.

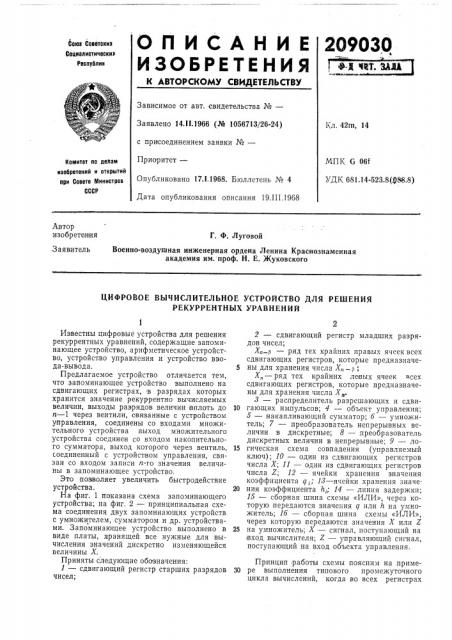

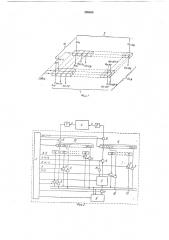

На фиг. 1 показана схема запоминающего устройства; на фиг. 2 — принципиальная схема соединения двух запоминающих устройств с умножителем, сумматором и др. устройствами. Запоминающее устройство выполнено в виде платы, хранящей все нужные для вычисления значений дискретно изменяющейся величины Х.

Приняты следующие обозначения:

1 — сдвигающий регистр старших разрядов чисел;

2 — сдвигающий регистр младших разрядов чисел;

Х, p — ряд тех крайних правых ячеек всех сдвигающих регистров, которые предназначе5 ны для хранения числа Х„

Մ— ряд тех крайних левых ячеек всех сдвигающих регистров, которые предназначены для хранения числа Х„.

3 — распределитель разрешающих и сдви10 гающих импульсов; 4 — объект управления;

5 — накапливающий сумматор; б — умножитель; 7 — преобразователь непрерывных величин в дискретные; 8 — преобразователь дискретных величин в непрерывные; 9 — ло15 гическая схема совпадения (управляемый ключ); 10 — один из сдвигающих регистров числа Х; 11 — один из сдвигающих регистров числа 2; 12 — ячейки хранения значения коэффициента q,-; 18 — ячейки хранения значе20 ния коэффициента h;; 14 — линия задержки;

15 — сборная шина схемы «ИЛИ», через которую передаются значения q или h на умножитель; 1б — сборная шина схемы «ИЛИ», через которую передаются значения Х или Z

25 на умножитель; Х вЂ” сигнал, поступающий на вход вычислителя; Z — управляющий сигнал, поступающий на вход объекта управления.

Принцип работы схемы поясним на .приме30 ре выполнения типового промежуточного цикла вычислений, когда во всех регистрах

3 уже содержатся соответствующие числа. За начало процесса примем такт передачи числа Х„ (численного значения сигнала) из .преобразователя 8 в крайние левые ячейки сдвигающих регистров. Для осуществления этой операции из распределителя 8 разрешающих и сдвигающих импульсов поступает на соответствующую схему «И» первый разрешающий импульс, Но так как в схеме предусматривается параллельная передача значений всех разрядов числа, то этот же,первый импульс поступает на входы схем «И» 9 других, не показанных на фиг. 2, разрядов числа Х„. Итак, во всех левых ячейках сдвигающих регистров будет записано число Х„. Заметим, что значение числа Х„:предыдущего цикла, обозначаемое в текущем цикле через Х„г до начала рассматриваемого .процесса уже сдвинуто в соседние ячейки. Следующим разрешающим импульсом через схему «ИЛИ», условно показанную на схеме шиной 15, передается на умножитель значение коэффициента qp, а через шину 1о передается на умножитель значение числа Х„. Третий импульс запускает умножитель, в котором производится операция умножения qp на Х„. Четвертым импульсом разрешается передача результата умножения из умножителя в накапливающий сумматор 5. Пятым импульсом запускается сумматор. В сумматоре, который выполнен накапливающим, значение qp+ суммируется с содержанием сумматора (в данном случае с нулем), результат накопления остается в сумматоре. На этом заканчивается первый этап рассматриваемого цикла вычислений.

Следующий этап начинается передачей значений q> и Х i на вход умножителя действием шестого импульса. Дальше процесс протекает аналогично предыдущему, т. е. в результате действия третьего, четвертого и пятого импульсов в сумматоре оказывается сумма, равная доЛ, +а1 Х„ i Потом в сумматоре оказывается сумма чоХл + qltn — 1+ ч»Хп — 2

1 и т. д. до получения суммы,, q,.A „г. Слеt=0 дующим действует импульс р+6, разрешающий передачу hi u Z i на вход умножителя.

С этого момента начинаются операции по вычислению всех членов, содержащих значения сигнала Z, и одновременно производится сдвиг на одну ячейку вправо всего массива чисел в левой плате. Заметим, что аналогичный сдвиг массива чисел в правой плате производится во время реализации этапов получения суммы

1, q;A „< . Последней вычислительной onei- =o

209030 рацией рассматриваемого цикла операция умножения h, на Z„„„B

3 теле и накопление суммы gqi XÄ i+

i=Î в сумматоре. является умножиа

g nfZ, 1

1=1

Итак, в результате выполнения всех указанных выше этапов вычислений в сумматоре формируется значение сигнала Z„. Импульсом (+a+6 это значение сигнала Z передается из сумматора в крайние левые ячейки платы. Кроме того, через некоторое время, обусловленное наличием в цепи линии задержки, этим же импульсом +и+6 содержимое накапливающего сумматора 5 сбрасывается на нуль. Заключительным импульсом в рассматриваемом цикле является импульс (+a+7.

20 Этот импульс разрешает передачу с сохранением в ячейках запоминающей платы значения сигнала Л„к преобразователю 8, который предназначен для преобразования сигнала Z„èç дискретной формы в непрерывную. После преобразования сигнал поступает на вход управляемого объекта 4, Из анализа работы схемы следует, что вычислитель допускает в течение достаточно больших интервалов времени перемещение массивов чисел в запоминающих платах одновременно с выполнением вычислительных операций. Это обстоятельство повышает общее бьгстр одей ств и е в ы числ ителя.

Предмет изобретения

Цифровое вычислительное устройство для решения рекуррентных уравнений, содержащее запоминающее устройство, арифметическое устройство, устройство управления и

4> устройство ввода-вывода, отличающееся тем, что, с целью увеличения его быстродействия, в нем запоминающее устройство выполнено на сдвигающих регистрах, в разрядах которых хранится значение рекуррентно вычис50 ляемых величин, выходы разрядов величин вплоть до и — 1 через вентили, связанные с устройством управления, соединены со входами множительного устройства, выход множительного устройства соединен со входом на55 копительного сумматора, выход которого через вентиль, соединенный с устройством управления, связан со входом записи и-ro значения величины в запоминающее устройство.