Многоканальный блок приоритета

Иллюстрации

Показать всеРеферат

209049

Союз Советских

Социалистических

Реслуйлик

Бсесоюа юя

Кл. 42m, 14

Комитет оо делам иаооретеиий и открытий

0рН Сосете Мииистрое

СССР

МПК G 061

УДК 681.326.3(088.8) Автор изобретения

О. И. Семенков

Институт технической кибернетики АН Белорусской ССР

Заявитель

МНОГОКАНАЛЪНЫЙ БЛОК ПРИОРИТЕТА

Известны многоканальные блоки приоритета, содержащие триггеры, логические схемы

«И», «ИЛИ» и «НЕ».

Предложенный блок отличается от известных тем, что в нем выходы управления устройств, связанных с общим запоминающим устройством, соединены с первыми входами схем первых «И» и с единичными входами триггеров, вторые входы схем «И» подсоединены- -к выходам первых схем «НЕ», входы которых через схему «ИЛИ» связаны с выходами триггеров всех каналов, кроме данного, выходы первых схем «И» через схему «ИЛИ» подсоединены к местному устройству управления запоминающим устройством, выходы триггеров данного канала подсоединены к первым входам вторых схем «И» и через схемы «ИЛИ» ко входам вторых схем «НЕ» каналов, номер которых превышает данный, выходы вторых схем «НЕ» подключены к первому входу третьих схем «И», вторые входы которых связаны через схему «ИЛИ» с выходами местного устройства управления запоминающим устройством, выходы третьих схем «И» подключены ко вторым входам вторых схем «И», а их выходы через схемы

«ИЛИ» — ко входам местного устройства управления запоминающим устройством.

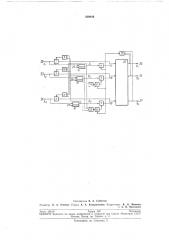

На чертеже дана блок-схема блока приоритета.

Она содержит схемы «И» 1 — 8, схемы «НЕ»

9 — 18, триггеры 14 — 16, диодные сборки 17—

19, местное устройство 20 управления и схему «ИЛИ» 21.

5 Заявки вычислительных устройств на обращение к памяти поступают на входы 22 — 24 блока хь х2,...,х„, Рассмотрим работу блока на примере канала 28 (хД.

10 Возможны два режима работы этого канала, определяющиеся тем, свободна или заня. та оперативная память обслуживанием других заявок в момент поступления заявки по данному каналу. Сигнал заявки поступает на

15 вход схемы «И» 2 и установочный единичный вход триггера 15. Если к этому моменту ни один из каналов блока не занят (триггеры

14 — 16 находятся в состоянии «О»), то на выходе схемы «И» 2 появляется сигнал заявки, 20 который через диодную сборку 18 проходит в местное устройство управления оперативной памяти для обслуживания.

Если поступившая заявка застает оперативную память занятой выполнением другой за25 явки (один или несколько триггеров находятся в состоянии «1») сигнал на выходе схемы «НЕ» 10 отсутствует, и поступившая заявка запоминается триггером 15, становясь таким образом в очередь на обращение к памя30 ти. Если вместе с заявкой второго канала в

209049

3 очереди стоят заявки каналов с более высокими номерами (х, х,„,х„), то после кончания обслуживания (появление одного из сигналов у1, у2,...,у, на шинах 25 — 27) эти заявки поступают в местное устройство 20 управления в порядке возрастания номеров каналов. Это обеспечивается схемами «НЕ» 12 — 18 и схемами «И» 4 — 8. После того, как окончено обслуживание заявки второго канала, местное устройство 20 управления вырабатывает сигнал g>, который устанавливает в «0» триггер 15 и с выхода схемы «ИЛИ» 21 поступает на вторые входы схем «И» 4, б и 8, производя тем самым очередной опрос каналов.

Логику работы многоканального блока приоритета можно описать следующими логическими условиями: канал х,: га,=х, $2,+г, у, канал х,: 222=2, f 2,.+-га г, у,.;

j= I j=1 канал ха (аа — хз Q 2! к гз (21 + 22) Q M

j=1 j 1 уа и — 1 и и — 1 канал х„: га„= х„. Y 2, -(- г„ г, Q у,, к=1 где х1, х ... х„ — сигналы заявок по соответствующим каналам;

z1, z» ... z„— сигналы на входе триггеров

14 — 1б;

g1, у» ... g„— сигналы на выходе местного устройства 20 управления.

Анализ вычислительной системы с блоком приоритета показывает, что среднее время ожидания в очереди для i-ro устройства определяется следующим выражением: и к 1 где и — число вычислительных устройств в системе (т. е. число каналов блока приоритета), 10 т — время обслуживания одной заявки, p,, — средняя частота следования заявок к-ro устройства.

Предмет изобретения

15 Многоканальный блок приоритета, содержащий триггеры, логические схемы «И», «ИЛИ» и «НЕ» отличающийся тем, что, с целью его упрощения, выходы управления устройств, связанных с общим запоминающим

20 устройством, соединены с первыми входами схем первых «И» и с единичными входами триггеров, вторые входы схем «И» подсоединены к выходам первых схем «НЕ», входы которых через схему «ИЛИ» связаны с выхода25 ми триггеров всех каналов, кроме данного, выходы первь1х схем «И» через схему «ИЛИ» подсоединены к местному устройству управления запоминающим устройством, выходы триггеров данного канала подсоединены к первым

30 входам вторых схем «И» и через схемы

«ИЛИ» к входам вторых схем «НЕ» каналов, номер которых превышает данный, выходы вторых схем «НЕ» подключены к первому входу третьих схем «И», вторые входы кото35 рых связаны через схему «ИЛИ» с выходами местного устройства управления запоминающим устройством, выходы третьих схем «И» подключены ко вторым входам вторых схем

«И», а их выходы через схемы «ИЛИ» — ко

40 входам местного устройства управления запоминающим устройством.

209049

72

24

27

Составитель В. А. Субботин

Редактор Л. А. Утехина Техред А. А. Камышникова Корректоры: В. П. Минеева и А. П. Васильева

Заказ 336/16 Тираж 530 Подписное

ЦНИИГ!И Комитета по делам изобретений и открытий при Совеге Мшшстров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2