Двоичное арифметическое устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВМДЕТЕЛЬСТВУ

2IO49I

Союз Ссаатских

Социалистических

Ресоуйлин

Зависимое от авт. свидетельства №

Кл. 42m, 14

Заявлено 18.Ш,1965 (№ 947514/26-24) с присоединением заявки №

Приоритет

Опубликовано 6.111968. Бюллетень ¹ 6

Дата опубликования описания 27.V.1968

МПК G 061

УДК 681.325.5 (088.8) Комитет со делам иаобретений и открытий ари Сосете Министров

СССР

Автор изобретения

T. В. Долидзе

Заявитель

ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

Известны двоичные арифметические устройства, содержащие параллельный накопительный сумматор, регистр множимого — делителя и регистр множителя — частного, а также вентили.

Предлагаемое устройство отличается от известных тем, что выходы триггеров регистра множимого — делителя связаны с первыми входами вентилей, вторые входы которых объединены и подсоединены к выходам схем сборки, входы которых подключены к шинам сигнала переноса предыдущего разряда и инверсии переноса с предыдущего разряда, Единичный выход регистра множимого — делителя связан через первый вентиль с нулевым входом триггера предыдущего разряда, нулевой выход через второй с единичным входом.

Это позволяет упростить устройство.

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 — детальная блок-схема устройства умножения.

В состав арифметического устройства входят двоичный накопительный сумматор 1, регистр 2 множимого (делителя, второго слагаемого), регистр 8 частного (множителя), схема 4 управления операциями сложения (вычитания) при делении и преобразованием кода делителя, триггер б запоминания кода делителя, элемент задержки б, схема 7 управления занесением и сдвигом разрядов частного и сложением (вычитанием), схемы 9 и 10 «ИЛИ» к устройство местного управления 8.

При выполнении операций сложения сигнал в младший разряд сумматора приходит из устройства управления 8. Этот сигнал по цепи переноса и его инверсии, переписывая разряд за разрядом содержимое регистра 2 в сумматор 1 с одновременным преобразованием содержимого сумматора 1 в окончательный результат.

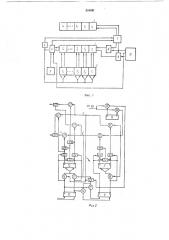

Специфика предлагаемого арифметического устройства иллюстрируется детальной блоксхемой и описанием работы этой схемы для случая умножения.

15 На схеме (фиг. 2) показаны два последних разряда множимого и регистра суммы и один старший разряд (управляющий) регистра множителя. Схема состоит из регистра множимого на триггерах 9 и 10, регистра суммы на

20 триггерах 11 и 12, триггера 18 старшего разряда множителя, вентилей 14 и 15 сдвига множимого вправо, вентилей 1б — 18 промежуточного суммирования, вентилей 19 и 20 управления умножением, вентилей 21 в цепи обра25 зования переносов и его инверсий. Устройство содержит также диодные логические схемы 22

«И» и схемы 28 «ИЛИ». Из устройства управления поступают последовательности импульсов, число которых зависит от числа разрядов со30 множителей, Если триггер 13 старшего разря3 да множителя находится в состоянии «1», управляющий импульс проходит через вентиль 20 и подается на вентили переноса. Перенос формируется согласно следующей формуле:

Е = (А Л ВЛе) V (АЛВЛ е) V / (А Л В Л е) \/ (А Л В Л е), где: А и  — одноименные разряды слагаемых; е — перенос из предыдущего разряда.

Цепи переноса состоят из логических быстродействующих элементов 21, от которых зависит скорость распространения переносов, и сравнительно медленно действующих диодных логических элементов 22 и 28, от которых не зависит скорость распространения переноса и которые подготавливают цепи для быстрого распространения двоичных переносов.

Вентили 1б и 17 на выходе регистра множимого 2, получающие сигналы,Е и Е, дают результаты однотактного суммирования (промежуточное суммирование).

Промежуточная сумма определяется следующим выражением:

Ь,„=(Е; ДВ,) /(Е-,ЛВ).

Полученная таким образом промежуточная сумма заменяет находящееся в сумматоре 1 предыдущее частичное произведение последующим частичным произведением.

Каждый разряд текущей суммы определяется следующей формулой:

S — (S „A ) / (Sñ „A )

В отличие от существующих устройств умножения в предлагаемом устройстве с целью совмещения операций сложения и сдвига на выходе триггеров регистра множимого 2 подключены вентили 14 и 15 сдвига вправо, управляемые импульсами переноса Е или его инверсией Е в каждом разряде. Применение управляемых вентилей сдвига позволяет одновременно разряд за разрядом образовывать сумму частичных произведений в сумматоре и сдвигать вправо на один разряд множимое.

Это совмещение операций сложения и сдвига позволяет переходить к следующему циклу образования частичных произведений непосредственно после формирования суммы в младшем разряде независимо от старших разрядов, благодаоя чему существенно ускоряется распространение переносов при умножении.

Сдвиг единицы i-го разряда регистра множимого определяется по следующей формуле:

С = (В; Л E -I) Ч (B,. Л Е -1) Ч (В; Л К), где:  — i-ый разряд регистра множимого; г

Et s u Er i — перенос и его инверсии из сосед210491 него младшего разряда сумматора; К вЂ” разрешение сдвига при нулевом состоянии триггера старшего разряда регистра множителя Т„.

Сигнал сдвига единицы С является сигналом установки в единичное положение триггера (i — 1) -ro разряда множимого.

Сдвиг нуля i-го разряда регистра множимого определяется по следующей формуле:

С = (В(Л Ei i) V (В,/\ Er i) V (В,. /\ К).

Если триггер старшего разряда регистра множителя Т„стоит в нулевом положении, управляющий импульс проходит через вентиль

В6 и подается на схему сдвига множимого;

15 происходит сдвиг множимого на один разряд вправо. Временная задержка между управляющими импульсами, которые приходят из устройства управления, определяется временем срабатывания триггера сумматора. Сдвиг

20 и сложение, из которых состоит процесс умножения, происходят одновременно. Их продолжительность определяется в основном временем срабатывания триггера младшего разряда.

25 Время умножения двух т-разрядных двоичных чисел для настоящего устройства равно:

З0 гДе: f„= t,ð+ " Р- вРемЯ оДноРазРЯДного

m сложения;

t,ð — время переброса триггера;

Т„,р=mt„,ð — максимальное время переноса;

" р = t,ð — время переноса на один разряд. пе т

Указанные цепи переноса могут использоваться также для организации сдвига при делении.

Предмет изобретения

Двоичное арифметическое устройство, содержащее параллельный накопительный сумма45 тор, регистр множимого — делителя и регистр множителя — частного, вентили, отличающееся тем, что, с целью его упрощения, выходы триггеров регистра множимого — делителя связаны с первыми входами вентилей, вторые входы

50 которых объединены и подсоединены к выходам схем сборки, входы которых подключены к шинам сигнала переноса предыдущего разряда и инверсии переноса с предыдущего разряда, единичный выход регистра множимого—

55 делителя связан через первый вентиль с нулевым входом триггера предыдущего разряда, нулевой выход через второй — с единичным входом.