Многоканальный счетчик импульсов

Иллюстрации

Показать всеРеферат

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

2lll56

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 11.III.1966 (№ 1060968j26-24) с присоединением заявки №

Приоритет

Опубликовано 08.I I.1968. Бюллетень № 7

Дата опубликования описания 24.IV.1968

Кл. 42гп, 14

МПК G 06f

УДК 621.374.32(088.8) Комитет по делам изобретеиий и открытий при Совете Министров

СССР

Авторы изобретения

И. А. Злобин, Е. Е. Шапаренко и Л. П. Клюкин

Заявитель

МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ

Многоканальные счетчики импульсов используются в качестве регистратора .в аппаратуре, предназначенной для измерения плотности потока ионизирующих излучений счетHbIM методом. Такие измерения часто провоДятся в ядерной физике и lIIpH решении технических задач, связанных с использованием радиоактивных изотопов и ядерных излучений, особенно при гамма-дефектоскопии различных изделий методом, просвечивания с непрерывным сканированием.

Известен многоканальный, счетчик импульсов, содержащий предварительные пересчетные устройства с триггерами переполнения, блок памяти на ферритовых сердечниках с приводом, коммутатор, регистр памяти, программный блок, блок .вывода накопленной информации, логические схемы и таймерное устройство, включающее генератор иипульсов, делитель частоты и узел «пуск — стоп» с временным селектором.

Цикл работы этого счетчика состоит из одновременного накопления информации по всем каналам и поочередного вывода информации, накопленной в каналах, причем во время вывода информация не накапливается и часть ее теряется. В результате такой счетчик не может быть использован при контроле процессов, где требуется непрерывное накопление информации с одновременным ее выводом.

Предложенный многоканальный счетчик отличается от известного тем, что он содержит в таймерном устройстве схему «НŠ— И» и статический триггер, причем схема «HE — И» соединена по входу с временным селектором, а по выходу — с делителем частоты, управляющие входы статического триггера соединены с выходом делителя, выходом временного селектора и узлом «пуск — стоп», à выход— с управляющим входом, схемы «HE — И»,привода блока памяти и через линию задержки с управляющим .входом схемы «НŠ— И» таймерного устройства и входом блока выхода информации. Кроме того, счетчик содержит узел блокировки команд, состоящий из счетчика импульсов, статического триггера блокировки и двух схем «НŠ— И» блокировки команд «стирание информации» и «вывод информации», причем счетчик импульсов соединен по входу,со схемой «НŠ— И» таймерного устройства, по выходу со входом статического триггера блокировки, второй вход которого связан с управляющим входом статического триггера таймерного устройства, а выходы подключены к схемам «НŠ— И» блокировки команд, входы которых соединены со входом счетчика импульсов и с блоком вывода информации.

Устройство обеспечивает непрерывное накопление информации с одновременным ее выводом, а также предотвращает вывод ин3 формации в промежуток времени с момента пуска до момента достижения выбранного времени набора.

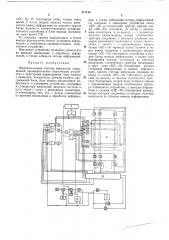

На чертеже дана блок-схема многоканального счетчика.

Он содержит предварительные пересчетные устройства 1, триггеры 2 переполнения, регистр 8 адреса коммутатора, дешифратор 4 коммутатора, формирователи 5 тока считывания, формирователи 6 тока записи, схему

«ИЛИ» 7, программный блок 8, временной селектор 9, генератор 10 импульсов, схему

«HE — И» 11 таймерного устройства, делитель частоты 12, статический триггер 18, узел

«пуск — стоп» 14, схему «НŠ— И» 15, блок памяти 16, линию задержки 17, схемы

«НŠ— И» 18 и 19, счетчик 20 импульсов, статический триггер 21, усилители 22 чтения, генераторы 28 токов запрета, триггеры 24 регистра памяти, блок 25 вывода.

Схема работает следующим образом.

При подаче сигнала «пуск» с узла «пуск —стоп» 14 происходит разблокировка входа предварительных пересчегных усгройств и начинается набор информации в каналы счегчика. Одновременно сигнал «иуск» устанавливает тр ггеры 18 и 21 в состояние, поддерживающее схемы «НŠ— И» 11, 15 и 18 закрь:тыми, а схему «НŠ— И» 19 открытой, и открывает временной селектор 9, через который импульсы ча"тотой f с генератора импульсов 10 попадают на вход схемы «НŠ— И» ll, на вход регистра адреса 8 коммугагора, в программный блок 8 и на вход установки «О» триггера 18.

Коммутатор 8, 4 с приходом сигнала частотой f начинает поочередный опрос У триггеров 2 переполнения, одновременно выбирая соответствующий формирователь 5 тока считывания и формирователь б тока записи. Частота генератора импульсов рассчитывается, исходя из требования, чтобы время переклю1 чения коммутатора S= — было больше или

Л равно времени обращения к блоку 16 памяти.

За каждый промежуток времени S программный блок 8 выдает серию управляющих импульсов, следующих в определенной последовательности: импульс считывания, на который формирователь 5 тока считывания вырабатывает импульс тока считывания, достаточный для перемагничивания соответствующей строки ферритовой матрицы в нулевое состояние; импульс разблокировки усилителей 22 чтения; импульс добавления «Ь> з регистр памяти 24, возникающий при поступлении на .вход программного блока 8 импульса с соответствующего триггера переполнения через схему «ИЛИ» 7, импульс запрета, поступающий через схему «HE — И» 15 н запускающий q генераторов 28 тока запрета, сигнал блокировки на каждый из которых подается с соответствующего триггера 24 регистра памяти, импульс записи на формирователь тока записи, вырабатывающий импульс тока за$11156

4 писи в выбранную строку матрицы, и импульс установки «О» в регистре памяти.

Под действием импульсов считывания и разблокировки происходит считывание инфор5 мации, накопленной в опрашиваемом канале матрицы, в регистр памяти, Если триггер переполнения опрашиваемого канала счетчика зафиксировал состояние переполнения предварительного пересчетного устройства, то под действием импульса добавления «1» к информации, выведенной в регистр памяти, добавляется единица. Под действием импульсов запрета и записи осуществляется регенерация числа .в опрашиваемый канал матрицы, после чего импульсом установки «0» регистр памяти очищается.

С приходом очередного сигнала с генератора,программа повторяется, но уже для следующего канала.

20 1

По истечении времени T/N, равного KN —, 1 где К вЂ” целое число, сигнал с выхода делителя частоты 12 переводит триггер И в состояние, запрещающее схеме «НŠ— И» 15 про2> пускать сигналы, служащие для регенерации числа в выбранном (первом) канале блока памяти. При этом происходит сброс информации, накопленной в опрашиваемом канале матрицы.

Длительность сигнала с выхода триггера И равна S, поскольку триггер 18 устанавли вается в состояние «О» каждым .в;.одным импульсом с генератора 10. Сигнал, формируемый триггером 18, задержанный на время линией задержки 17 и поданный на входы схем

«НŠ— И» 18, 19, 11 и счетчика 20 используется в качестве команды вывода информации из,канала счетчика, команды установки в состояние «0» предварительных пересчетных

40 устройств, а также для управления схемой

«НŠ— И» 11. Импульсы с генератора 10, переводящие триггер 18 в состояние «О» из состояния «1», на вход делителя частоты 12 не поступают, поскольку в момент их прохожде4 ния на управляющем входе схемы «НŠ— И»

11 присутствует запрещающий сигнал, подаваемый через линию задержки 17 с выхода триггера 18. Благодаря этому формирование триггером 18 перечисленных выше команд для соседних каналов осуществляется с интервалом T/Ì, а для любого отдельного канала— с интервалом Т.

Открытая схема «НŠ— И» 19 пропускает команду установки «О» предварительного пересчетного устройства в блок вывода, где этот сигнал формируется и подается в опрашиваемое .предварительное пересчетное устройство.

Схема «НŠ— И» 18, служащая для пропускания команды «вывод информации», остается о0 закрытой до тех пор, пока на счетчик 20 с коэффициентом .пересчста Л, управляющий триггером 21, не поступит N импульсов с выхода линии задержки 17. При этом триггер 21 изменяет состояние на противоположное, от65 крывая схему «НŠ— И» 18 и закрывая схему

2!1156

«НŠ— И» 19, Благодаря этому только через время T после подачи сигнала «пуск» начинается вывод информации из каждого канала блока памяти и соответствующего предварительного устройства в блок:вывода поочередно через время TIN.

Из команды «вывод информации» в блоке вывода формируется сигнал «стирания информации» в выбранном предварительном пересчетном устройстве.

Описанное устройство позволяет совместить во времени накопление и обработку информации, а также избежать .потерь информации.

Предмет изобретения

rÈíîãîêàHàëüíûé счетчик имаульсов, содержащий предварительные пересчетные устройства с триггерами переполнения, блок памяти с приводом, коммутатор, регистр памяти, программный блок, блок вывода накопленной информацпи и таймерное устройство, состоящее из генератора импульсов, делителя частоты и узла «пуск — стоп» с временным селектором, отличающийся тем, что, с целью совмещения во времени накопления и обработки информации, а также избежания потерь информации, он содержит в таймерном устройстве схему

«НŠ— И» и статический триггер, причем схема «НŠ— И» соединена по входу с времен,ным селектором, а по выходу — с делителем частоты, управляющие входы статического триггера соединены с выходом делителя, выходом временного селектора и узлом «пуск—

CT0II», а ВЫХОД вЂ” с уlIp3B lSIIOlliÈМ входОл1 схемы «1-1Š— И» при вода блока памяти и через линию задержки с управляющим входом схемы «НŠ— И» таймерного устройства и входом блока вывода информации, а также узел блокировки команд, состоящий из счетчика импульсов, статического триггера блокировки и двух схем «НŠ— И» блокировки команд

«стирание информации» и «вывод информации», причем счетчик импульсов соединен по входу со схемой «НŠ— И» таймерного устройспва,:по выходу со входом статического триггера блокировки, второй вход которого связан с управляющим входом статического триггера таймерного устройства, а выходы подключены к схемам «НŠ— И» блокировки команд, 25 входы которых соединены со входом счетчика импульсов и с блоком вывода информации.