Усилитель тока

Иллюстрации

Показать всеРеферат

2II589

О11ИСАН И Е

ИЗОБРЕТЕНИЯ, Союз Сааетских

Социалистических

Реслт4лик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства ¹

Заявлено 11.1.1967 (Эй ?125019/26-9) с присоединением заявки №

Приоритет

Опубликовано 19.П.1968. Бюллетень № 8

Дата опубликования описания 7Х.1968

Кл. 21а2, 18/08

МПК H 03f

УДК 621.374.4:621.397 (088.8) 11омитет по делам иаа4ретаиий и открытий лри Сааета Мииистрае

СССР

Авторы изобретения

Х. Н. Седиков и В. В. Доброхотов

Заявитель

УСИЛИТЕЛЬ ТОКА

Предложенный усилитель тока относится к импульсной технике. В известных выходных усилительных каскадах 1на транзисторах, работающих на индуктивную нагрузку (например, на отклоняющую систему электроннолучевой трубки с магнитным отклонением), требуется обеспечить линейность выходной характеристики, температурную и временную стабильность.

В известных усилителях относительно велико время нарастания и спадания тока, что затягивает момент его установления в индуктивности, и следовательно ограничивает быстродействие.

В предложенном устройстве эмиттер входного и коллектор составного транзисторов через два резистора, один из которых переменный, подключены к эмиттеру транзистора выходного каскада, база которого соединена с землей,. а к коллектору подключена нагрузка, при этом участок база — эмиттер входного транзистора зашунтирован,диодом, а эмиттер .первого триода составного транзистора подсоединен одновременно к базе второго триода и через резистор к источнику питания.

Такое исполнение улучшает температурную б еменные характеристики

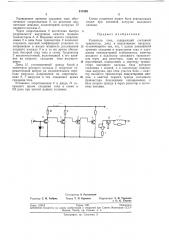

Принципиальная схема предложенного усилителя изображена на чертеже.

Усилитель состоит из трех каскадов.

Ток в отклоняющей катушке 1 индуктив5 ности создается коллекторным током транзисторов 2, 3, 4, составляющих второй каскад, собранный по схеме составного транзистора с общим эмиттером. Напряжение на базу транзистора 2 поступает с коллекторной на10 грузки транзистора входного каскада 5.

Эмиттер входного каскада подключен к сопротивлениям б и 7, по которым протекает выходной ток отклонения. Так как выходной ток в 500 †10 раз больше входного, каскад

I5 5 работает в режиме, близком к режиму эмиттерного повторителя: на сопротивлениях

6, 7 нагрузки повторяется входное напряжение, которое и определяет величину выходного тока, протекающего через катушку индук20 тивности. Таким образом осуществляется отрицательная обратная связь, определяющая стабильность и линейность усилителя.

Для сокращения длительности нарастания

25 тока в цепь катушки 1 индуктивности включен каскад с общей базой 8 (третий каскад усилителя). За счет введения каскада с высоким выходным сопротивлением время нарастания тока в катушке удается сократить "

ЗО 3 раза при прочих равных условиях.

211589

Предмет изобретения

Составитель А. Рассмотров

Техред Т. П. Курилко Корректоры: 3. И. Тарасова и О. li. Тюрина

Редактор С. И. Хейфиц

Заказ 1024)2 Тираж 530 Подписное

ЦНИИПИ Комитета rio делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2

Уменьшение времени спадания тока обеспечивает сопротивление 9, по величине значительно меньшее коллекторной нагрузки 10 входного каскада 5.

Через сопротивление 9 достаточно быстро разряжаются внутренние емкости мощных транзисторов 8, 4. Введение малого сопротивления 9 в цепь базы транзистора 8 позволяет сохранить высокий коэффициент усиления по напряжению и малую мощность рассеивания входного каскада 5 и в то же время обеспечить быстрый спад тока в схеме. Транзистор

2 высокочастотный, маломощный и его влияние на скорость спадания тока несущественно.

Диод 11, установленный между базой и эмиттером входного каскада 5, подрезает отрицательный выброс на положительном перепаде импульса напряжения на сопротивлениях б, 7 нагрузки и тем сокращает время спадания тока.

Установка сопротивления б и диода 11 сокращает время спадания тока в схеме в

2,5 раза при прочих равных условиях.

Схема усилителя может быть использована также при активной нагрузке выходного каскада, Усилитель тока, содержащий составной транзистор, диод и индуктивную нагрузку, 10 отличающийся тем, что, с целью уменьшения времени спадания и нарастания тока и улучшения температурной стабильности, эмиттер входного и коллектор составного транзисторов через два резистора, один из которых

15 переменный, подключены к эмиттеру транзистора выходного каскада, база которого соединена с землей, а к коллектору подключена нагрузка, при этом участок база — эмиттер входного транзистора зашунтирован дио20 дом, а эмиттер первого триода составного транзистора подсоединен одновременно и базе второго триода и через резистор к источнику питания.