Комбинационный преобразователь двоичного кода в двоично- десятичный

Иллюстрации

Показать всеРеферат

2I7708

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСИОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №вЂ”

Заявлено 17.1V.1967 (№ 1150830/26-24) Кл. 42mз, 5/00 с присоединением заявки №

МПК G 06f

УД К 681.325.53(088.8) 11риоритет

Опубликовано 07.V.1968, Бюллетень № 16

Комитет по делам изоеретеиий и открытий при Совете Министров

СССР

Дата опубликования описания 22.VIII.1968

Авторы изобретения

Ю. Р. Миронович и Б. Г. Ушерович

Центральное проектно-конструкторское бюро механизации и автоматизации

Заявитель

КОМБИНАЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО

КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ

Преобразователи параллельного двоичного кода в двоично-десятичный известны.

Предложенный комбинационный преобразователь двоичного кода в двоично-десятичный код содержит потенциальные логические преобразователи двоичного кода в двоично-десятичный код и двоично-десятичные сумматоры и отличается от известных тем, что в нем выходы первого пятиразрядного каскада логического преобразователя соединены со входами второго и третьего разрядов двоично-десятичного сумматора, а выходы второго пятиразрядного логического преобразователя соединены со входами первого, второго и третьего разрядов двоична-десятичного сумматора, выходы которого соответствуют преобразованному двоично-десятичному коду.

Использование потенциальных логических схем позволяет повысить быстродействие и устойчивость работы преобразователя.

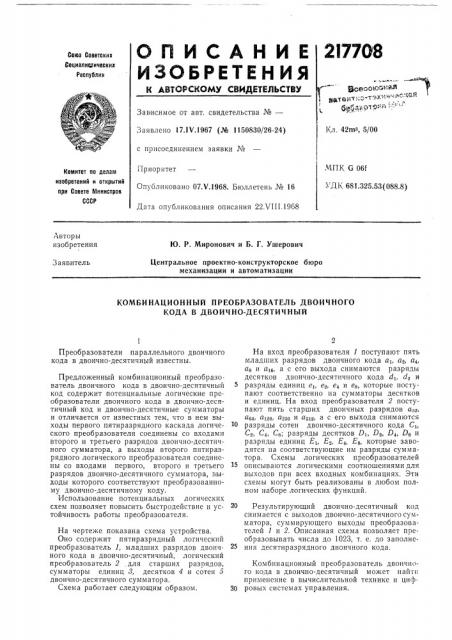

На чертеже показана схема устройства.

Оно содержит пятиразрядный логический преобразователь 1, младших разрядов двоичного кода в двоично-десятичный, логический преобразователь 2 для старших разрядов, сумматоры единиц 8, десятков 4 и сотен 5 двоично-десятичного сумматора.

Схема работает следующим образом.

На вход преобразователя 1 поступают пять младших разрядов двоичного кода аь ав, а4, а8 и а«, а с его выхода снимаются разряды десятков двоично-десятичного кода d>, ds u

5 разряды единиц е,, ев, е4 и еа, которые поступают соответственно на сумматоры десятков и единиц. На вход преобразователя 2 поступают пять старших двоичных разрядов азз, <о4, п«з, az;s и а5«, а с его выхода снимаются

10 разряды сотен двоично-десятичного кода С>

С», С, Cs.,разряды десятков О,, D, В„Ds и разряды единиц Е,, Е,, Ех, Е, которые заводятся на соответствующие им разряды сумматора. Схемы логических преобразователей описываются логическими соотношениями для выходов при всех входных комбинациях. Эти схемы могут быть реализованы в любом полном наборе логических функций.

20 Результирующий двоично-десятичный код снимается с выходов двоично-десятичного сумматора, суммирующего выходы преобразователей 1 и 2. Описанная схема позволяет преобразовывать числа до 1023, т. е. до заполнения десятиразрядного двоичного кода.

Комбинационный преобразователь двоичного кода в двоично-десятичный может найти применение в вычислительной технике и циф30 ровых системах управления.

217708

Предмет изобретения а,а,а а,а, ам 2 %в Ь Ъ

Бв Ф 2 Ег

4 Ф 2 1

Т1 L8 С/ С2 L „

Составитель Б. С. шкрабов

Редактор Л. А. Утехина Техрсд T. П. Курилко Корректоры: Т. Д. Чунаева и А. П. Васильева

Заказ 2037/!3 Тираж 530 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совсте Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, и р. Сапунова, 2

Комбинационный преобразователь двоичного кода в двоично-десятичный код, содержащий потенциальные логические преобразователи двоичного кода в двоично-десятичный код и двоична-десятичные сумматоры, ог.еи. чающийся тем, что, с целью повышения быстродействия, выходы первого пятиразрядного каскада логического преобразователя соединены со входами второго и третьего разрядов двоично-десятичного сумматора, а выходы второго пятиразрядного логического преобразователя соединены со входами первого, второго и третьего разрядов двоично-десятичного сумматора, выходы которого соответствуют преобразованному двоично-десятичному коду.