Устройство для преобразования двоично- десятичного кода

Иллюстрации

Показать всеРеферат

2I852 2

ОПИСАНИ Е

ИЗОБРЕТЕНИЯ

Союз Советокиз

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 06.IX.1966 (№ 1100671/26-24) с присоединением заявки №

Приоритет

Опубликовано 17Х,1968. Бюллетень № 17

Дата опубликования описания 8Х!!!.1968

Кл, 42m, 14

МПК С 06f

УДК 681.325.63(088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Авторы изобретения

В. A. Левицкий и А. П. Охинченко

Заявитель

УСТРОЙСТВО ДЛЯ HPЕОБРАЗОВАНИЯ ДВОИЧНОДЕСЯТИЧНОГО КОДА

Известно устройство для преобразования двоично-десятичного кода целых чисел в двоичный код, содержащее сдвиговой регистр кода преобразуемого числа, шифратор, двоичный параллельный сумматор и узел управления.

Предлагаемое устройство отличается от известных тем, что выходы младшего (старшего) разряда каждой тетрады сдвигового регистра подключены через шифратор ко вхо ам соответствующих разрядов сумматора, а гыходы узла управления — к цепям управления сдвигами кодов регистра и сумматора. Это позволяет повысить скорость преобразования.

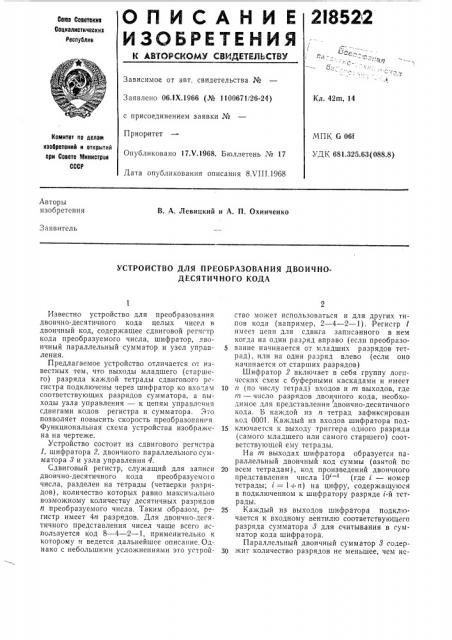

Функциональная схема устройства изображена на чертеже.

Устройство состоит из сдвигового регистра

1, шифратора 2, двоичного параллельного сумматора 8 и узла управления 4.

Сдвиговый регистр, служащий для записи двоично-десятичного кода преобразуемо о числа, разделен на тетрады (четверки разрядов), количество которых равно максимально возможному количеству десятичных разрядов н преобразуемого числа. Таким образом, регистр имеет 4п разрядов. Для двоично-десятичного представления чисел чаще всего используется код 8 — 4 — 2 — 1, применительно к которому и ведется дальнейшее описание. Однако с небольшими усложнениями это устройство может использоваться и для других типов кода (например, 2 4 2 — !). Регистр 1 имеет цепи для сдвига записанного в нем когда на один разряд вправо (если преобразо5 вание начинается от младших разрядов тетрад), или на один разряд влево (если оно начинается от старших разрядов)

Шифратор 2 включает в себя группу логических схем с буферными каскадами и имеет

10 и (по числу течрад) входов и m выходов, где и — число разрядов двоичного кода, необхо) димое для представления двоично-десятичного кода. Б каждой из и тетрад зафиксирован код 0001. Каждый из входов шифратора под15 ключается к выходу триггера одного разряда (самого младшего или самого старшего) соответствующей ему тетрады.

На m выходах шифратора образуется параллельный двоичный код суммы (взятой по

20 всем тетрадам), код произведений двоичного представления числа 10 (где i — номер тетрады; i = 1 —: n) на цифру, содержащуюся в подключенном к шифратору разряде i-й тетрады.

25 Каждый из выходов шифратора подкл очается к входному вентилю соответствующего разряда сумматора 3 для считывания в сумматор кода шифратора.

Параллельный двоичный сумматор 3 содер30 жит количество разрядов не меньшее, чем не218522

Составитель В. В. Максимов

Редактор Е. В. Семанова Техред Т. П. Курилко Корректоры: А. П. Васильева и Н. И. Быстрова

Заказ 2105/20 Тираж 530 Подписное

Ill-1ИИПИ Комитета по делам. изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 обходимо для двоичного представления максимальногоо преобразуемого числа. Сумма t ор имеет регистр суммы для запоминания результата и цепи сдвига результата на один разряд вправо (влево), если входы шифратора подключены к самым младшим (самым старшим) разрядам тетрад регистра 1.

В тех случаях, когда устройство применяется для ускорения ввода информации в

ЦВМ или спецвычислитель, имеющие, по крайней мере, один собственный сумматор, последний используется и в данном устройстве в качестве сумматора 8.

Узел управления 4 представляет собой группу типовых импульсных схем и обеспечивает командные сигналы для приема извне в регистр 1 кода преобразуемого числа, пеоедачи этого кода с выходов шифратора в сумматор, сдвига на один разряд кодов в регистре 1 и сумматоре 8.

Устройство работает следующим образом.

После ввода преобразуемого числа в регистр 1 с выходов шифратора 2 в сумматор 3 считывается двоичный код числа, соотве гствующего и-разрядному десятичному числу, содержащему в каждом из разрядов либо «0», либо «1» — в зависимости от положения -.риггеров регистра.

Далее трижды повторяется цикл, состоящий из сдвига на один разряд кодов, которые ранятся в регистре и сумматоре, и последующего добавления в сумматор нового кода с выходов шифратора. После этого в сумматоре оказывается двоичный код преобразованного числа, поскольку туда были введены с необходимыми «весами» коды, соответствующие четырем разрядам всех тетрад регистра 1.

10 Таким образом, независимо от количества разрядов преобразуемого числа, процесс преобразования занимает три такта суммирования, три такта сдвига и один начальный такт ввода кода из шифратора в сумматор.

Предмет изобретения

Устройство для преобразования двоично-десятичного кода целых чисел в двоичный код, содержащее сдвиговый регистр кода преобра20 зуемого числа, шифратор, двоичный napaл, лельный сумматор, узел управления, отличаюи(ееся тем, что, с целью повышения скорости преобразования, выходы младшего (старшего) разряда каждой тетрады сдвиго25 вого регистра подключены через шифратор ко входам соответствующих разрядов сумматора, а выходы узла управления — к цепям управления сдвигами кодов регистра и сумматора.