Схема сравнения

Иллюстрации

Показать всеРеферат

ОПИСАНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 29.Х11.1966 (Ле 1125633/26-24) — У с присоединением заявки №

Комитет по делим изобретеиий и открытий при Совете Министров

СССР

Приоритет

8) Опубликовано 17.V.1968. Б1ог!летев ¹ 17

Дата опубликования описания 6Л"П1.1968

Авторы изобретения

В. М. Долкарт, M. М. Каневский, Г. Х. Новик и В .Н. Степанов

Всесоюзный научно-исследовательский институт электромеханики

Заявитель

СХЕМА СРАВНЕНИЯ

Известны схемы сравнения двоичных чисел, содержащие диодные схемы совпадения, инвертирующие и выходные транзисторы.

Предложенная схема отличается тем, что коллектор инвертирующего p — и — р-транзистора каждого разряда соединен со входами диодных схем совпадения и с базой дополнительного n — p — -n-транзистора, коллектор которого подключен к эмиттеру дополнительного и — р — и транзистора следующего разряда, а эмиттер дополнительного транзистора старшего разряда по соединен к источнику питания.

Это позволяет уменьшить количество Неооходимого оборудования.

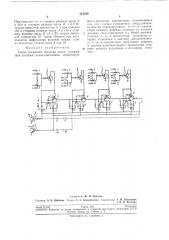

Схема, сравнения четырех разрядов двоичных чисел приведена па чертеже.

Сравниваемые числа А и В размещаются в двух регистрах сд,поднымп схемами совпадеHHя 1 и 2 IB Irаждох! разряде, п) lirllo ICHHь1)iil к нулевым и единичным выходам А,, В,. и

Аг, В,. тРиггеРов Региствов соотвстстве!ьно, 11 с р — -гг — р-инвертирующими транзпсторамп 8 на выходе, коллекторы которых соединены со входами других диодных схем совпадения 4, 5 и с базами дополнительных и — р — n-транзисторов 6, коллектор каждого из которых подключен к эмиттеру дополнительного и — р — итранзистора следующего разряда, а эмиттер дополнительного транзистора старшего разряда соединен с источником питания, Вторые входы диодных схем совпадечия 4 и 5 подключены к единичным,выходам триггеров А:, Вг, а выходы схем совпадения через диоды и 8 — к базам выход транзисторов 9 il

5 10.

В исходном состоянии транзисторы 8 и о

occcх разрядов заперты. При совпадении информации в ста )Illllx разрядах регистров транзисторы 8» 6 открыты. выходные тран1р зисторы 9 и 10 заперты. а потенциал питания (30в) через цепочку последовательно соединенных дополнительных транзисторов 6 подается на дподные схемы совпадения следуюlFIÄIx разрядов.

15 Прп соападен1ш информации l30 всех разрядах транзисто1)ы 8 и 6 ВОРх разрядов oTKpbI ты, и потенцпа7 ООв появится FIH коллекторе послc31сго м TH,Tøcãо разряда. Прп этом выходные транзисторы 9:l 10 заперты или ог20 крыты; ec:!It Опп подсоединены и 1 Оллсктору транзистора 6 последнего разряда через резцсторы 11, 12 и диоды г8, 14. Одновременное

ВК1IoitCHÍOC ПЛП ВЬIК;ПОЧЕПНОЕ СоетоЯНИЕ ВЫходнь!х транзисторов 9 и 10 свидетельствует о

25 равенстве сравнивал bix чисел А=-В.

При несовпадении старших разрядов сравнпвасмых чисел, транзисторы 8 и 6 заперты, и потенциал питания 30в на дподные схемы совпадения следующих разрядов не подается, 30 и тем самым блокируется связь следующ! х разрядов с выходными транзисторами 9 и 10, 218530

Составитель Ю. Н. Колотов

1 едактор Э. Н, Шибаева Техрсд A. Л, Камышиикова Корректоры: Г. И. Плешакова и В. В. Крылова

Заказ 2112/5 Гираж 530 Подписное

ЦНИИГ1И Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типографии, пр. Сапунова, 2

При наличии «1»,в старшем разряде числа А и «0» в старшем разряде числа В (А)В) открыт выходной транзистор 9, а при наличии

«0» в старшем разряде числа А и «1» в старшем разряде числа В (А (В) открыт выходной транзистор 10. Таким образом при несовпадении информации включен только одич пз выходных транзисторов 9 или 10.

Предмет изобретения

Схема сравнения двоичных чисел, содержащая диодные схемы совпадения, инвертирующие и выходные транзисторы, отлича ошаяся тем, что, с целью уменьшения оборудования, коллектор инвертирующего р — и.— р — транзистора каждого разряда соединен со входами

5 диодных схем совпадения и с базой дополнительного л — р — и-транзистора, коллектор которого подключен к эмиттеру дополнительного и — р — и-транзистора следующего разряда, а эмиттер дополнительного транзистора стар10 шего разряда подключен к источнику питания.