Двоичный дешифратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Кл, 42)пз, 7/24

42m:, 5/02

Заявлено 21.Х11.1965 (И 1044423/26-24) с присоединением заявки ¹

Приоритет

Опубликовано 14.V1.1968. Бюллетень № 19

Дата опубликования описания 6.1Х.1968

МПК G 06I

G 061

УДIy 681.325.53 (088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

А. А. Бирштейн

Заявитель

ДВОИЧНЫЙ ДЕШИФРАТОР

Известны двоичные дешифраторы, содержащие регистры и дешифрирующие матрицы.

Предложенный дешифратор на и разрядов, содержащий базовую часть, выполненную в виде дешифратора на и — р разрядов любого известного типа, и дополнительную часть на р разрядов в виде регистра на триггерах, отличается от известных тем, что выходы триггеров подсоединены к схемам «И», к каждой из которых также подсоединена одна из 2Р групп выводов нагрузок базового дешифратора, подключенных к его выходам. Такое выполнение дешифратора позволяет упростить устройство и повысить надежность его работы.

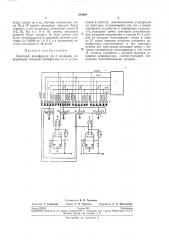

Предложенный двоичный дешифратор изображен на чертеже. Он содержит базовый дешифратор 1 с группой выходных каналов, триггерные ячейки 2 дополнительных разрядов, логические схемы И 8, повторные группы выходных каналов 4, нагрузку 5.

Дешифратор выполнен на шесть разрядов, в качестве основного, базового, принят дешифратор на четыре разряда, а число дополнительных разрядов, следовательно, равно р=2.

Аноды ат, аз, aт и а4 триггерных ячеек дополнительных пятого и шестого разрядов подключены к логическим схемам Ит, Ие, И,, и Ич так, чтобы с учетом записываемых в этих разрядах нуля или единицы и в соответствии с этим распределением потенциалов на анодах а, ... а соответственно всегда была бы открыта лишь одна логическая схема И, а следовательно, и одна группа выходных каналов, а все остальные логические схемы И и им соответствующие группы выходных каналов были бы заперты. Прп изменении двоичного числа на выходе дешифратора в пределах первых четырех разрядов, т. е. от 000000 до 001111, открытой будет лишь логическая схема 11т и

i группа выходных каналов, соответствующая десятичным числам от 0 до 15. При записи единицы в дополнительном пятом разряде (n — р+1=4-l1 = 5) открывается логическая схе»a Ие и соответственно !! группа выходных каналов, а все остальные логические схемы И и группы выходных каналов запираются. В этом случае счет будет в двоичной системе счисления от 010000 до 011111 или в десятичной системе от 16 до 31.

При записи единицы в дополнительном шестом разряде (н — p+2=4+ 2=6) и при нулсвом состоянии пятого разряда открытой будет логическая схема I I>. а следовательно, и !!! группа выходных каналов, а остальные логические схемы И и группы выходных каналов будут заперты. В этом случае двоичный счет будет изменяться от 100000 до 101111 или в десятичной системе счисления от 32 до 47.

При записи единицы в дополнительных пятом

30 и шестом разрядах под высоким потенциалом

219891

Предмет изобретения

Составитель И. Н. Горелова

Техред Т. П. Курилко Корректор С. А. Башлыкова

Редактор T. Горшкова

Заказ 2379/б Тираж 530 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров CCCl

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 будут аноды аа и а4, поэтому логическая схема И4 и IV группа выходных каналов будут открыты, а все остальные логические схемы И (И, И,, Из) и 1, П и П1 группы выходных .каналов будут заперты. В этом случае счет будет производиться в двоичной системе счисления от 110000 до 111111, а в десятичной системе счисления от 48 до 63.

Двоичный дешифратор на и разрядов, содержащий основной дешифратор на n — р разрядов и регистр дополнительных р разрядов на триггерах, отличающийся тем, что, с целью упрощения устройства и повышения надежности, выходные шины триггеров дополнительных .разрядов подключены к схемам И, к каждой из которых подсоединена также и одна из 2р групп выводов нагрузок основного дешифратора, подключенных к его выходам, причем все триггерные выходные шины с высоким потенциалом подсоединены к той схеме

И, которая соединена с группой выходов основного дешифратора, соответствующей очередному дополнительному разряду.