Цифровой интегратор

Иллюстрации

Показать всеРеферат

219911

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик, . ьЩ 1

Зависимое от авт. свидетельства М

Заявлено 09.XI.1965 (№ 1036788/26-24) с присоединением заявки М

Приоритет

Опубликовано 14.Ъ 1.1968. Бюллетень Мо 19

Дата опубликования описания 2.IX.1968

Кл 42m4, 7/18

42d, 10

МПК G 06@

G 01с1

УДК 681.335.7(088.8) Номитет по делам изобретений и открытий при Совете Министров

СССР

Авторы изобретения

Л. А. Русинов и А. Л. Гуревич

Заявитель

ЦИФРОВОЙ ИНТЕГРАТОР

Известны цифровые интеграторы, содержа1цие регистры подынтегральной функции, преобразователи кода функции и число-импульсный накопительный счетчик.

Предлагаемое устройство отличается от известных тем, что оно содержит триггер, счетный вход которого подключен к выходу разрядов счетчика преобразователя кода подынтегральной функции в число-импульсный код, единичный выход триггера подсоединен ко входу вентиля переноса, выход которого соединен со входом число-импульсного накопительного счетчика, а также к шине переноса дополнительного кода из регистра подынтегральной функции в преобразователь, нулевой выход триггера соединен с шиной переноса прямого кода из регистра в преобразователь.

Это позволяет упростить интегратор при кодировании подынтегральной функции m-ричными невзвешенными кодами.

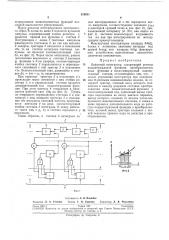

На фиг. 1 показана блок-схема двух соседних разрядов интегратора для интегрирования функций, представленных в т-ричной системе счисления, каждый разряд которых кодирован двоичными кодами (в том числе и невзвешенными, например двоично-десятичными циклическими); на фиг. 2 — график тактов.

Интегратор состоит из регистра 1 подынтегральной функции, преобразователя кода подынтегральной функции в число-импульсный на управляемом счетчике 2 со вспомогательным триггером 8, вентилем 4 и накопительного счетчика 5 интеграла со схемами задержки б, предназначенными для устранения временного наложения импульсов. Каждая разрядная ячейка регистра 1 связана с соответствующей ячейкой счетчика 2. Последний устанавливается в положение, соответствующее прямому или дополнительному коду

10 подынтегральной функции при импульсе опроса регистра 1, поступающем с триггера 3. Выход счетчика 2 соединен со счетным входом триггера 8, нулевая выходная шина которого соединена с регистром 1. При переходе триг15 гера из положения «1», в положение «О» происходит опрос регистра и передача прямого кода его содержимого в счетчик 2. Единичная выходная шина триггера 3 соединена с ячейкой регистра 1 так, что при переходе тригге20 ра 8 из положения «О» в положение «1» вводится в счетчик 2 дополнительный код, запасенный в регистре значения подынтегральной функции. Кроме того, единичный выход триггера соединен с управляющим входом венти25 ля 4: если триггер в положении «1» вентиль открыт. Импульсные входы разрядных вентилей 4 вместе со входами ячеек счетчика 2 подключены к шине 7 тактовых импульсов.

Выходы вентилей соединены со входами раз30 рядных ячеек счетчика 5 интеграла (при ин219911

Фиг 2

Фиг. 1

Составитель А. В. Ишлейко

Редактор Л. А. Утехина Техред T. П. Курилко Корректор Л. В. Наделяева

Заказ 2381/1 Тираж 530 Подписное

L."ÍÈÈÏt4 Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 тегрировании знакопеременных функций последний выполняется реверсивным).

Перед началом интегрирования производигся сброс, а затем по шине 8 подается пусковой импульс, опрашивающий ячейки регистра 1, вводится прямой код функции в счетчик 2.

Поступающие с шины 7 тактовые импульсы фиксируются счетчиком 2, но так как вентили

4 заперты, триггеры 8 находятся в положении

«О», то на счетчик интеграла тактовые импульсы не проходят (вспомогательный такт

Л1т на фиг. 2). Через число импульсов, равное дополнению введенного в счетчик 2 значения у, функции в k-ом разряде, соответствующая ячейка счетчика 2 переполняется и опрокидывает связанный с ней триггер 3 в положение

«1». Вспомогательный такт, длившийся в течение Atт = (т — у; ) г, заканчивается.

При переходе триггера 8 в положение «1» происходит опрос связанной с ним ячейки регистра 1, и в управляемый счетчик вводится дополнительный код подынтегральной функции. При этом вентиль 4 отпирается и начинается рабочий такт (М на фиг. 2). Теперь до очередного переполнения счетчика 2 и связанного с ним возврата триггера 3 в положение «О» импульсы тактовой частоты пропускаются вентилем 4 на вход соответствующей ячейки счетчика 5 интеграла. К концу рабочего такта (Ма = у, г) в счетчик передается д импульсов.

Таким образом, в счетчик 5 интеграла за

2 шаг интегрирования At = тт передается число импульсов, соответствующее значению уи,> в некоторой средней точке а (см. фиг. 2), принадлежащей интервалу At. Это, как видно из фиг, 2, частично компенсирует погрешность так же как при интегрировании по методу средних прямоугольников.

Фиксируемая интегратором площадь bdafg, ближе к истинному значению площади под кривой bcaeg, чем площадь bchg, фиксируемая устройством, выполненным аналогично двоичному умножителю.

Предмет изобретения

15 Цифровой интегратор, содержащий регистр подынтегральной функции, преобразователь кода функции и число-импульсный накопительный счетчик, отличающийся тем, что, с целью упрощения интегратора при кодирова20 нии т-ричными невзвешенными кодами, он содержит триггер, счетный вход которого подключен к выходу разрядов счетчика преобразователя кода подынтегральной функции в число-импульсный код, единичный выход триг25 гера подсоединен ко входу вентиля переноса, выход которого соединен со входом число-импульсного накопительного счетчика, а также к шине переноса дополнительного кода из регистра подынтегральной функции в преобразова30 тель, нулевой выход триггера соединен с шиной переноса прямого кода из регистра в преобразователь.