Устройство умнож1ения

Иллюстрации

Показать всеРеферат

0nmcaHHE

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

220632

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства М

Заявлено 26.1Х.1966 (лю 1104575/26-24) с присоединением заявки 1чо

Приоритет

Опубликовано 28.VI.1968. Бюллетень М 20

Дата опубликования описания 9,IX,1968

1 л. 42тп:, 7/44

МПЬ; 6 06k

Комитет оо делам изобретений и открытий ори Совете Министров

СССР

УДЕ 681.325.57 (088.8) Авторы изобретения А. М. Шаумаи, М. К. Чирков, И. Я. Березиая и Г. H. Моисеева

Заявитель Вычислительный центр Ленинградского Государственного университета им. А. А; Жданова

УСТРОЙСТВО УМНОЖЕНИЯ

В вь1числительной технике известны устройства умножения, содержащие регистры, сумматор, блок анализа множителей и логические схемы.

Предлагаемое устройство отличается от известных тем, что с целью экономии оборудования вход регистра множителя соединен с выходами элемента запрета и первого элемента совпадения, выход регистра связан с первым входом второго элемента совпадения и входом записи элемента запрета. Второй вход второго элемента совпадения, вход запрета элемента запрета и первый вход первого элемента совпадения подключены к выходу схемы счетчика разрядов множителя. Второй вход первого элемента совпадения соединен с выходом сумматора. Вход схемы округления подключен к выходу схемы счетчика разрядов множителя, а выход — ко входу сумматора.

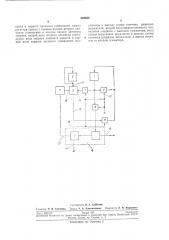

На чертеже представлена блок-схема устройства для умножения и-разрядных чисел для случая арифметического устройства последовательного счета.

Устройство содержит регистр 1 множителя и результата, регистр 2 множимого, сумматор

8, блок 4 анализа множителя, счетчик б разрядов множителя, выход б анализатора цифр множителя, элементы 7 и 8 совпадения, раз1 ешающие прохождение кода числа, хранящегося в регистре 1, элемент 9 запрета. управляющий перезаписью числа в регистре 1, элемент

10 совпадения, управляющий выдачей резуль5 тата суммирования в регистр 1 и схему 11 окру гл ени я.

Выход регистра 1 соединен с одним из входов каждого из элементов 7 и 8 совпадения и входом записи элемента 9; второй вход эле10 мента 8 соединен с устройством управления вычислительного устройства и входом запрета

12 элемента 9; второй вход элемента 7 — с выходом 18 схемы счетчика разряда множителя и входом запрета 12 элемента 9. Выход эле15 мента 7 соединен со входом 14 сумматора, выход элемента 8 — со входом блока анализа множителя, выход элемента 9 — со входом регистра 1. Выход 15 схемы счетчика соединен со входом округления, а выход 1б — с устройст20 вом управления концом операций вычислительного устройства. Выход б соединен с устройством управления вычислительного устройства, выход регистра 2 — со входом этого же регистра и входом 17 сумматора, выход схемы

25 округления — со входом 18 сумматора. Выход

19 сумматора соединен с одним входом элемента 10, другой вход этого элемента соединен с выходом 18, а выход — с выходом регистра

1. Регистры 1 и 2 допускают сдвиг только

ЗО вправо.

220632

60 а

1 при 6, i-—

Лп=

О пРи5, 1(—"

Устройство работает следующим образом (мцож1;тель записан в регистре 1, множимос-— в регистре 2).

В пачалс операции происходит сдвиг множи1сл i .;а один разряд вправо. Одновременно из устройства управления вычислительным устр 11ством поступает импульс па вход элемента

h ii вход запрета элемента 9. При этом младша;1 цифра множителя IiocT) паеет В апализаio1! цифр мно1китсля, а в счетчик разрядов множителя записывается единица.

Пусть цифра младшегс разряда множителя а, — Ile нуль, тогда начинаются сдвиги в регистрах 1 и 2. Сигналов на вход запрета элемента 9 не поступает. В результате в регистрах 1 и 2 начинается перезапись чисел, т. е. млад шие разряды чисел переписываются в старшие, и кроме того, разряды множимого, начиная с младшего, поступают в сумматор 8 (выдача с сумматора на вход регисгра 1 запрещена).

При выдаче (и — 1)-го разряда множимого происходит выдача сигнала со счетчика 5 разрядов множителя на схему 11. По этому curi алу с выхода схемы 11 на сумматор 8 подаа ется число — -, где а — основание системы

2 счисления (например, для десятичной подается число 5). Если цифра (n — 1)-го разряда больа

Ilic пли равна, в сумматоре образуется еди2 ница переноса в старший разряд, т. е. происходит округление и-го разряда множимого.

При выдаче п-го разряда из регистров прекращается перезапись в регистре 1, так как из схемы счетчика разрядов поступает сигнал на вход элемента 7 и вход запрета элементов 9.

При этом разрешается выдача на сумматор п-го разряда множителя (в первом цикле это будет нуль). Таким образом, происходит сложение п-го разряда множимого и, если есть единицы переноса, с записью результата в старший разряд регистра 1, так как открыт элемент 10.

После окончания этого цикла происходит вычитание единицы из цифры множителя, поступавшей в начале операции в блок 4, Происходит повторный анализ оставшегося значения цифры множителя. Если она не равна нулю, процесс, описанный выше, повторяется.

Только теперь происходит сложение n-ro разряда множимого с промежуточным результатом, записанным в регистре 1, и, если есть, единицей переноса от округления. Количество описанных циклов сложения будет равно цифре исследуемого разряда множителя. При этом в регистре 1 получают промежуточный результат, равный а> (b„+An), где а — младший разряд множителя, b„— старший п-ный разряд множимого.

В том случае, если анализируемое значение разряда множителя равно нулю, производится сдвиг регистра 1 вправо. При этом сигналом из устройства управления открывается элемент 8 и закрывается элемент 9. Следующая цифра множителя поступает в блок 4, и в счетчик 5 разрядов заносится еще одна единица.

При умножении на цифру следующего разряда множителя все происходит аналогично опп10 санному a исключением того, что в связи с заполнением счетчика 5 разрядов на единицу происходит округление (n — 1) -го разряда, т. е. — поступает в сумматор одновременно с

15 (п — 2) -ным разрядом множимого. При этом через элемент 9 будет переписываться (п — 2) младших разряда регистра 1, а в сумматор через элемент 7 будут переписываться 2 старших разряда. С промежуточным результатом умно20 хкения складывается теперь не старший п-й разряд множимого, а два старших, и-й и (n — 1) -й разряды множимого, В результате этого цикла происходит умножение аа (6 „+ 11 1+Хи — 1), а промежугоч25 ный результат равняется а, (b„+ Л и) + а, (b„+ b, I + Л n — 1).

При умножении на к-й разряд множителя в связи с заполнением счетчика к единицами ок30 ругление происходит (n — к+1) -го разряда а множимого, т. е. B сумматоре — будет склады2 ваться с (n — к) -ным разрядом множимого, а к промежуточному результату будут прибав35 ляться к старших разрядов множимого.

При умножении на последнюю цифру множителя происходит умножение

a„(b„+b„ I + ... + bl + Л 1), 40 и в регистре 1 записан результат, равный аЯ и+ A 6) + аЯ и + b -1 + Ah — 1) + " +

+ а„(Ь„+ b, 1+ ... + Ьд + М).

Множимое сохранено в регистре 2.

45 Счетчик 5 разрядов заполнен, и с его выхода 1б поступает сигнал конца операции в устройство управления концом операции и вычислительного устройства. Если количество значащих разрядов множимого и множителя в

50 сумме не превосходит п, то результат произведения, полученный данным способом, будет абсолютно точным. В противном случае результат будет приближенным, но в наихудшем случае относительная погрешность произведения

55 аП и — 1 не превышает

П 2х1

Предмет изобретения

Устройство умножения, содержащее регист. ры, сумматор, блок анализа множителя, логические схемы, отличиюи1ийся тем, что, с целью экономии оборудования, вход регистра

65 множителя соединен с выходами элемента за.

220632

Составитель В. А. Субботин

Техред А. А. Камышникова Корректор Л. В. Наделяева

l åäàêò0ð Е. В. Семанова

Заказ 2607715 Тираж 530 Подписное

Ц11ИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 прста и первого элемента совпадения, выход регистра связан с первым входом второго элемента совпадения и входом записи элемента запрета, второй вход второго элемента совпадения, вход запрета элемента запрета и первый вход первого элемента совпадения подкл!очсны K Выход схемы счетчика разрядов множителя, второй вход первого элемента совпадения соединен с выходом сумматора, вход схемы округления подкл1очен к выходу схемы

5 счетчика разрядов множителя, а выход соединен со входом сумматора.