Устройство для временной синхронизации импульсов

Иллюстрации

Показать всеИзобретение относится к импульсной технике и может быть использовано при построении различных цифровых устройств. Технический результат - упрощение устройства. Для этого устройство содержит два D-триггера, двухвходовый логический элемент ИЛИ, входную и выходную шину, шину синхронизации и вход обнуления. При работе устройства на выходной шине формируются импульсы, длительность которых равна периоду следования синхроимпульсов, а время формирования совпадает с временем прихода импульса на входной шине. 2 ил.

Реферат

Изобретение относится к импульсной технике и может быть использовано при построении различных цифровых устройств.

Известно устройство для синхронизации импульсов, содержащее три триггера, источник входного сигнала, источник импульсов синхронизации, инвертор [1].

Недостатком этого устройства является отсутствие необходимых временных соотношений между выходными информационными и синхронизирующими импульсами.

Известно также устройство для временной синхронизации импульсов [2], содержащее входную и выходную шины, шину синхроимпульсов, четыре триггера, два элемента ИЛИ-НЕ, элемент И, генератор импульсов и две дополнительные выходные шины.

Недостатком этого устройства является его сложность.

Задачей, на решение которой направлено данное изобретение, является упрощение устройства для временной синхронизации импульсов.

Поставленная задача достигается за счет того, что в устройстве для временной синхронизации импульсов, содержащем входную и выходную шины, шину синхроимпульсов, два D-триггера, инверсный выход одного из которых соединен с его D-входом, согласно заявленному решению прямой выход первого D-триггера соединен с D-входом второго D-триггера, прямой выход которого соединен с выходной шиной устройства и с первым входом логического элемента ИЛИ, выход которого соединен с R-входом первого D-триггера, второй вход логического элемента ИЛИ соединен с входом обнуления устройства и с R-входом второго D-триггера, С-входы первого и второго D-триггеров соединены соответственно с входной шиной и шиной синхроимпульсов устройства, a S-входы обоих D-триггеров соединены с общим проводом.

К существенным отличиям заявленного устройства по сравнению с известным (прототипом) относится особое схемное построение устройства, которое позволяет при резком сокращении числа элементов, входящих в устройство (исключены два триггера, генератор импульсов, элемент И и элемент ИЛИ-НЕ), сохранить его основные функции.

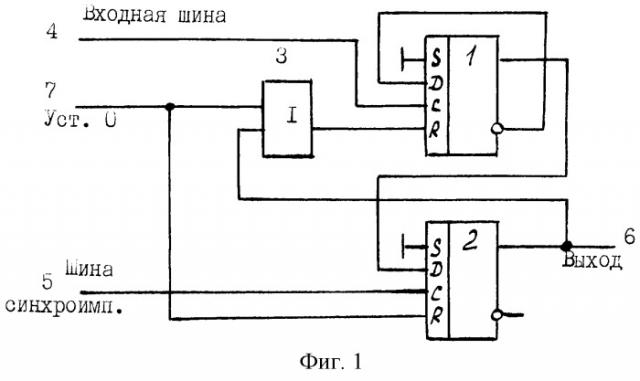

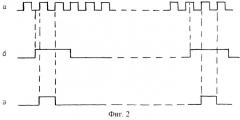

На фиг.1 представлена схема устройства, а на фиг.2 - временные диаграммы его работы.

Предлагаемое устройство содержит первый D-триггер 1, второй D-триггер 2, двухвходовый логический элемент ИЛИ 3, входную шину 4, шину 5 синхроимпульсов, выходную шину 6 и вход 7 обнуления.

Инверсный выход первого D-триггера 1 соединен с его D-входом, прямой выход первого D-триггера 1 соединен с D-входом второго D-триггера 2, прямой выход которого соединен с выходной шиной 4 и с первым входом двухвходового логического элемента ИЛИ 3, выход которого соединен с R-входом первого D-триггера 1. Второй вход логического элемента ИЛИ 3 соединен с входом 7 обнуления устройства и с R-входом второго D-триггера 2. С-входы первого и второго D-триггера 1 и 2 соответственно соединены с входной шиной 4 и шиной 5 синхроимпульсов устройства, а S-входы обоих D-триггеров 1 и 2 соединены с общим проводом.

Устройство работает следующим образом. После подачи питающего напряжения для установки первого и второго D-триггеров 1 и 2 в начальное состояние на вход 7 обнуления подается импульс обнуления, при этом на прямых выходах обоих триггеров 1 и 2 установится логическое состояние “0”.

На шину 5 синхроимпульсов поступает последовательность импульсов (фиг.2а). При поступлении на входную шину 4 импульса (фиг.2б) происходит запись логического состояния “1” на прямом выходе первого D-триггера 1, это же состояние установится и на D-входе второго D-триггера 2.

Ближайшим передним фронтом синхроимпульса шины 5 произойдет запись логического состояния “1” на прямом выходе второго D-триггера 2, а следовательно, и на выходной шине 6 (фиг. 2в), это же состояние установится на входе и выходе логического элемента ИЛИ 3 и произойдет установка первого D-триггера 1 в исходное состояние по R-входу. На его прямом выходе установится логическое состояние “0”. Это же состояние установится на D-входе второго D-триггера 2. Ближайшим передним фронтом синхроимпульса шины 5 произойдет запись логического состояния “0” на прямом выходе второго D-триггера 2, а, следовательно, и на выходной шине 6 (фиг.2в). Это же состояние установится на входе и выходе логического элемента ИЛИ 3, после этого формирование выходного импульса заканчивается. По приходе следующего импульса на входную шину 4 процесс повторяется.

Таким образом на выходной шине 6 формируются импульсы, длительность которых равна периоду следования синхроимпульсов, а время их формирования совпадает с временем прихода импульса на входной шине 4, тем самым осуществляется временная синхронизация импульсов.

Использование предложенного изобретения позволило создать устройство формирования импульсов с высокой скважностью.

Источники информации:

1. А.с. СССР 999150, кл. Н 03 К 5/153, 1980 г.

2. А.с. СССР 1054899, кл. Н 03 К 5/135, 1982 г. (прототип).

Устройство для временной синхронизации импульсов, содержащее входную и выходную шины, шину синхроимпульсов, два D-триггера, инверсный выход одного из которых соединен с его D-входом, отличающееся тем, что прямой выход первого D-триггера соединен с D-входом второго D-триггера, прямой выход которого соединен с выходной шиной устройства и с первым входом логического элемента ИЛИ, выход которого соединен с R-входом первого D-триггера, второй вход логического элемента ИЛИ соединен с входом обнуления устройства и с R-входом второго D-триггера, С-входы первого и второго D-триггеров соединены соответственно с входной шиной и шиной синхроимпульсов устройства, a S-входы обоих D-триггеров соединены с общим проводом.