Самонастраивающаяся система управления для объектов нейтрального типа с запаздыванием по управлению

Иллюстрации

Показать всеИзобретение относится к технической кибернетике и может быть использовано в системах регулирования объектами, параметры которых - неизвестные постоянные или медленно меняющиеся во времени величины. Технический результат заключается в возможности стабилизации самонастраивающейся системы при наличии объектов нейтрального типа с запаздыванием по управлению. Система содержит объект регулирования, три блока задания коэффициентов, пять сумматоров, восемь умножителей, пять интеграторов, три блока запаздывания, блок дифференцирования. 1 ил.

Реферат

Изобретение относится к технической кибернетике и может быть использовано в системах регулирования объектами, параметры которых - неизвестные постоянные или медленно меняющиеся во времени величины.

Наиболее близким техническим решением к предлагаемому является самонастраивающаяся система управления, содержащая первый блок задания коэффициентов, первый сумматор, первый умножитель, первый интегратор, второй умножитель, второй сумматор, объект регулирования, первый блок запаздывания, третий умножитель, второй интегратор, четвертый умножитель, второй блок задания коэффициентов, третий и четвертый сумматоры, блок дифференцирования, второй блок запаздывания, пятый умножитель, третий интегратор и шестой умножитель. Сигналы с выходов объекта регулирования поступают одновременно на соответствующие входы первого и второго блоков задания коэффициентов. Сигналы с выходов первого блока задания коэффициентов поступают на соответствующие входы первого сумматора. Сигналы с выходов второго блока задания коэффициентов поступают на соответствующие входы четвертого сумматора. Сигнал с выхода первого сумматора поступает на вход первого блока запаздывания, на первый вход первого умножителя и на вторые входы второго умножителя и третьего сумматора. Сигнал с выхода четвертого сумматора поступает на вход блока дифференцирования. Сигнал с выхода блока дифференцирования поступает на вход второго блока запаздывания и на первый вход третьего сумматора. Сигнал с выхода третьего сумматора поступает на вторые входы первого, третьего и пятого умножителей. Сигнал с выхода первого умножителя поступает на вход первого интегратора. Сигнал с выхода первого интегратора поступает на вход второго умножителя. Сигнал с выхода второго умножителя поступает на первый вход второго сумматора. В первом блоке запаздывания происходит задержка сигнала на время 1. Сигнал с выхода первого блока запаздывания поступает на второй вход четвертого умножителя и на первый вход третьего умножителя. Сигнал с выхода третьего умножителя поступает на вход второго интегратора. Сигнал с выхода второго интегратора поступает на первый вход четвертого умножителя. Сигнал с выхода четвертого умножителя поступает на второй вход второго сумматора. Во втором блоке запаздывания происходит задержка сигнала на время 2. Сигнал с выхода второго блока запаздывания поступает на второй вход шестого умножителя и на первый вход пятого умножителя. Сигнал с выхода пятого умножителя поступает на вход третьего интегратора. Сигнал с выхода третьего интегратора поступает на первый вход шестого умножителя. Сигнал с выхода шестого умножителя поступает на третий вход второго сумматора. Сигнал с выхода второго сумматора поступает на вход объекта регулирования.

Недостатком этой системы в случае наличия в объекте запаздывания по управлению, является неустойчивость положения равновесия.

Целью изобретения является обеспечение асимптотической устойчивости положения равновесия системы при наличии в объекте запаздывания по управлению.

Поставленная задача достигается тем, что в систему, содержащую два блока задания коэффициентов, два блока запаздывания, четыре сумматора, три интегратора, шесть умножителей, блок дифференцирования, объект регулирования; выходы объекта регулирования одновременно соединены с соответствующими входами первого и второго блока задания коэффициентов, выходы которых соединены с соответствующими входами первого и четвертого сумматоров, выход первого сумматора подключен к первому входу первого умножителя, к второму входу второго умножителя, к входу первого блока запаздывания и к второму входу третьего сумматора, выход первого умножителя связан со входом первого интегратора, выход первого интегратора подключен к первому входу второго умножителя, выход второго умножителя соединен с первым входом второго сумматора, выход первого блока запаздывания связан с первым входом третьего умножителя и со вторым входом четвертого умножителя, второй вход третьего умножителя подключен к выходу третьего сумматора, выход третьего умножителя соединен со входом второго интегратора, выход второго интегратора связан с первым входом четвертого умножителя, выход четвертого умножителя подключен к второму входу второго сумматора, выход четвертого сумматора связан со входом блока дифференцирования, выход которого соединен со входом второго блока запаздывания, выход второго блока запаздывания связан с первым входом пятого умножителя и со вторым входом шестого умножителя, второй вход пятого умножителя подключен к выходу третьего сумматора, выход пятого умножителя соединен со входом третьего интегратора, а выход третьего интегратора связан с первым входом шестого умножителя, выход шестого умножителя соединен с третьим входом второго сумматора, введены пятый сумматор, четвертый интегратор, третий блок задания коэффициентов, третий блок запаздывания, седьмой умножитель, пятый интегратор, восьмой умножитель, при этом вход третьего блока запаздывания подключен к выходу второго сумматора, выход третьего блока запаздывания связан со входом объекта регулирования, со вторым входом пятого сумматора, с первым входом седьмого умножителя и со вторым входом восьмого умножителя, первый вход пятого сумматора подключен к выходу второго сумматора, второй вход пятого сумматора подключен к выходу третьего блока запаздывания, а третий вход пятого сумматора связан с выходом третьего блока задания коэффициентов, выход пятого сумматора соединен со входом четвертого интегратора, выход четвертого интегратора связан со входом третьего блока задания коэффициентов и с первым входом третьего сумматора, второй вход седьмого умножителя связан с выходом третьего сумматора, выход седьмого умножителя соединен со входом пятого интегратора, выход пятого интегратора связан с первым входом восьмого умножителя, выход восьмого умножителя подключен к четвертому входу второго сумматора.

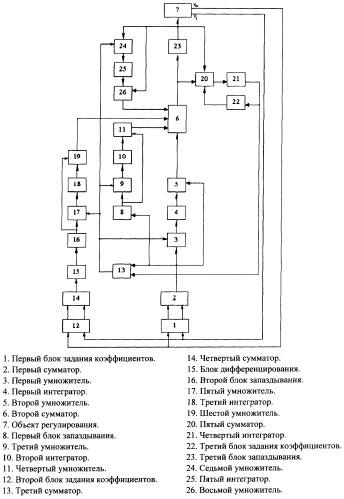

На чертеже представлена блок-схема системы. Система содержит первый блок задания коэффициентов 1, первый сумматор 2, первый умножитель 3, первый интегратор 4, второй умножитель 5, второй сумматор 6, объект регулирования 7, первый блок запаздывания 8, третий умножитель 9, второй интегратор 10, четвертый умножитель 11, второй блок задания коэффициентов 12, третий сумматор 13, четвертый сумматор 14, блок дифференцирования 15, второй блок запаздывания 16, пятый умножитель 17, третий интегратор 18, шестой умножитель 19, пятый сумматор 20, четвертый интегратор 21, третий блок задания коэффициентов 22, третий блок запаздывания 23, седьмой умножитель 24, пятый интегратор 25, восьмой умножитель 26.

Объект регулирования описывается уравнением

где х∈Rn - вектор состояния объекта регулирования, τ1>0, τ2>0, τ3>0 - известные постоянные запаздывания, y∈Rm - вектор выходных измеряемых координат, u - скалярное управляющее воздействие, ϕ(s) - начальная вектор-функция, A, D, Г, L, b - матрицы и вектор размерностей (n×n), (n×n), (n×n), (m×n), (n×l) соответственно, зависящие от вектора неизвестных параметров ξ(t)∈Ξ, Ξ - известное множество возможных значений вектора ξ(t).

К объекту подключается регулятор

где χ1, χ2, χ3, χ4 - настраиваемые параметры регулятора, g1, g2 - числовые векторы, выбираемые из следующих условий: гурвицевости полинома g

| * |

| 1 |

| * |

| 2 |

Используя критерий гиперустойчивости Попова, можно показать, что реализуемый алгоритм настройки параметров регулятора

где α>0, β>0, γ>0, λ>0 - числа, z - выход дополнительного контура, динамика которого описывается уравнением

где a0>0 - число,

обеспечивает асимптотическую устойчивость системы.

Система функционирует следующим образом.

Сигналы с выходов объекта регулирования 7 поступают одновременно на соответствующие входы первого 1 и второго 12 блока задания коэффициентов. В первом блоке 1 задания коэффициентов происходит умножение сигнала уi на коэффициент g1i. Сигналы с выходов первого блока 1 задания коэффициентов поступают на соответствующие входы первого сумматора 2, где складываются. Сигнал i=1,...,n с выхода сумматора 2 поступает на вход первого блока запаздывания 8, на первый вход первого умножителя 3 и на вторые входы второго умножителя 5 и третьего сумматора 13. Сигнал с выхода третьего сумматора 13 поступает на вторые входы первого умножителя 3, третьего умножителя 9, пятого умножителя 17, седьмого умножителя 24. В первом умножителе 3 происходит умножение сигнала с выхода сумматора 13 на сигнал с выхода сумматора 2. Сигнал с выхода первого умножителя 3 поступает на вход первого интегратора 4, где интегрируется. Сигнал с выхода первого интегратора 4 поступает на первый вход второго умножителя 5, где умножается на сигнал с выхода сумматора 2, поступающего на другой вход умножителя. Сигнал с выхода второго умножителя 5 поступает на первый вход сумматора 6. В первом блоке 8 запаздывания происходит задержка сигнала на время τ1. Сигнал с выхода первого блока запаздывания 8 поступает на второй вход четвертого умножителя 11 и на первый вход третьего умножителя 9, где умножается на сигнал с выхода сумматора 13. Сигнал с выхода третьего умножителя 9 поступает на вход второго интегратора 10, где интегрируется. Сигнал с выхода второго интегратора 10 поступает на первый вход четвертого умножителя 11, где умножается на сигнал с выхода первого блока запаздывания 8. Сигнал с выхода четвертого умножителя 11 поступает на второй вход второго сумматора 6. Во втором блоке 12 задания коэффициентов происходит умножение сигнала γi на коэффициент g2i. Сигналы с выходов второго блока 12 задания коэффициентов поступают на соответствующие входы четвертого сумматора 14, где складываются. Сигнал i=1,...,n c выхода сумматора 14 поступает на вход блока дифференцирования 15, где дифференцируется. Сигнал с выхода блока дифференцирования 15 поступает на вход второго блока запаздывания 16. Во втором блоке 16 запаздывания происходит задержка сигнала на время τ2. Сигнал с выхода второго блока запаздывания 16 поступает на второй вход шестого умножителя 19 и на первый вход пятого умножителя 17, где умножается на сигнал с выхода сумматора 13. Сигнал с выхода пятого умножителя 17 поступает на вход третьего интегратора 18, где интегрируется. Сигнал с выхода третьего интегратора 18 поступает на первый вход шестого умножителя 19, где умножается на сигнал с выхода второго блока запаздывания 16. Сигнал с выхода шестого умножителя 19 поступает на третий вход второго сумматора 6. Сигнал с выхода второго сумматора 6 поступает на первый вход пятого сумматора 20 и на вход третьего блока третьего блока запаздывания 23, сигнал с выхода третьего блока запаздывания 23 поступает на второй вход пятого сумматора 20, на второй вход восьмого умножителя 26, на вход объекта регулирования 7 и на первый вход седьмого умножителя 24, где умножается на сигнал с выхода третьего сумматора 13, сигнал с выхода седьмого умножителя 24 поступает на вход пятого интегратора 25, где интегрируется. Сигнал с выхода пятого интегратора 25 поступает на первый вход восьмого умножителя 26, где умножается на сигнал с выхода третьего блока запаздывания 23. Сигнал с выхода восьмого умножителя 26 поступает на четвертый вход второго сумматора 6. Сигнал с выхода пятого сумматора 20 поступает на вход четвертого интегратора 21, а с выхода четвертого интегратора 21 на вход третьего блока задания коэффициентов 22 и на первый вход третьего сумматора 13. Сигнал с выхода третьего блока задания коэффициентов 22 поступает на третий вход пятого сумматора 20.

Предлагаемая система обладает более широкими функциональными возможностями, так как может работать с объектами нейтрального типа, обладающими запаздыванием по управлению.

Данное устройство может быть реализовано промышленным способом, на основе стандартной элементарной базы.

Самонастраивающаяся система управления для объектов нейтрального типа с запаздыванием по управлению, содержащая первый блок задания коэффициентов, последовательно соединенные первый сумматор, первый умножитель, первый интегратор, второй умножитель, второй сумматор, последовательно соединенные первый блок запаздывания, третий умножитель, второй интегратор и четвертый умножитель, последовательно соединенные второй блок задания коэффициентов, четвертый сумматор, блок дифференцирования, второй блок запаздывания, пятый умножитель, третий интегратор, шестой умножитель, выходы объекта регулирования соединены с соответствующими входами первого и второго блоков задания коэффициентов, выходы первого блока задания коэффициентов соединены с соответствующими входами первого сумматора, подключенного выходом к второму входу второго умножителя, второму входу третьего сумматора и входу первого блока запаздывания, выход которого соединен с вторым входом четвертого умножителя, подключенного выходом к второму входу второго сумматора, выходы второго блока задания коэффициентов соединены с соответствующими входами четвертого сумматора, выход третьего сумматора соединен с вторыми входами первого, третьего и пятого умножителей, выход второго блока запаздывания соединен с вторым входом шестого умножителя, выход которого подключен к третьему входу второго сумматора, отличающаяся тем, что в систему введены пятый сумматор, четвертый интегратор, третий блок задания коэффициентов, третий блок запаздывания, последовательно соединенные седьмой умножитель, пятый интегратор и восьмой умножитель, первый вход пятого сумматора связан с выходом второго сумматора, вход третьего блока запаздывания соединен с выходом второго сумматора, выход третьего блока запаздывания подключен ко второму входу пятого сумматора, к первому входу седьмого умножителя, ко второму входу восьмого умножителя и к входу объекта регулирования, второй вход седьмого умножителя связан с выходом третьего сумматора, выход седьмого умножителя соединен с входом пятого интегратора, выход которого связан с первым входом восьмого умножителя, выход восьмого умножителя соединен с четвертым входом второго сумматора, выход пятого сумматора соединен с четвертым интегратором, выход которого подключен к входу третьего блока задания коэффициентов и к первому входу третьего сумматора, выход третьего блока задания коэффициентов соединен с третьим входом пятого сумматора.