Схема регулирования напряжения для интегральных схем чип-карт

Иллюстрации

Показать всеИзобретение относится к схеме регулирования напряжения, применяемой в области конструирования интегральных схем чип-карт. Технический результат заключается в уменьшении перерегулирования в процессе включения. Схема содержит последовательный регулятор (L) с полевым транзистором (М1). Между выводом истока, к которому приложено внешнее напряжение питания (VDDext), и выводом затвора (М1) последовательно включены конденсатор (С1) и второй полевой транзистор, предусмотренный в качестве передающего затвора (TG1), управляемый сигналом включения питания/сброса (POR). При приложении внешнего напряжения питания (VDDext) при последовательно подсоединенном передающем затворе (TG1) полевой транзистор (М1) отпирается в соответствии с происходящим при этом заряде конденсатора (С1). Так как этот заряд требует некоторого времени, за счет этого можно избежать перерегулирования внутреннего напряжения (VDDint). 2 з.п. ф-лы, 5 ил.

Реферат

Предлагаемое изобретение относится к схеме регулирования напряжения, применяемой в области конструирования интегральных схем (ИС) чип-карт.

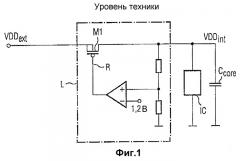

Интегральные схемы с различными зонами напряжений (внешние и внутренние напряжения) обычно содержат схемы регулирования напряжения, например, как описано на стр.10 документа LP2954/LP2954A “Регуляторы напряжения с низким выпадением из синхронизма для регулируемых микропроцессоров 5 В” от июня 1999 компании National Semiconductor Corporation. Рабочее напряжение для интегральной схемы представляет собой разность потенциалов между выводом заземления (VSS) и потенциалом питания. Это напряжение, далее называемое внутренним напряжением питания VDDint,вырабатывается посредством комплексной схемы регулирования напряжения, которая образована последовательным регулятором. Для упрощения пояснений схема соединений последовательного регулятора приведена на фиг.1 в составе известной схемы регулирования напряжения, иллюстрирующей принцип функционирования последовательного регулятора.

Показанная на фиг.1 схема содержит последовательный регулятор L, который содержит транзистор последовательного регулятора и преобразует внешнее напряжение питания VDDext во внутреннее напряжение питания VDDint. На выводе затвора транзистора М1 последовательного регулятора в качестве вывода R регулирования последовательного регулятора прикладывается электрический потенциал, предусмотренный для управления преобразованием напряжения. Этот сигнал является внутренним для регулятора аналоговым сигналом. Внутреннее напряжение питания VDDint предусмотрено для питания напряжением ИС чип-карты. Внутренняя емкость Ccore показана для пояснения функционирования схемы. Схема последовательного регулятора обычно существенно сложнее и не совпадает с показанным на чертеже упрощенным примером, но имеет тот же принцип функционирования.

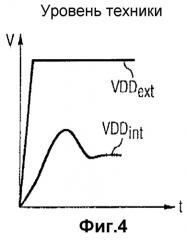

Показанная на фиг.1 схема регулирования напряжения имеет тот недостаток, что при быстром включении внешнего напряжения питания VDDext возникают перерегулирования (выбросы) внутреннего напряжения питания VDDint, которые, начиная с определенного уровня интеграции, становятся недопустимыми, так как они приводят к повреждению тонкого оксидного затвора транзистора, связанного с VDDint. На фиг.4 приведены характеристики изменения VDDint и VDDext в зависимости от времени для процесса включения.

Кроме того, для ИС чип-карт задается количество (пять) контактных площадок выводов, обычно называемых контактными площадками (VDDext, VSS, Clock (тактовый вывод), IO (ввод/вывод), Reset (сброс)), и последовательность их включения, соответствующая норме ISO/GSM. Поэтому нет никакой возможности за счет обеспечения дополнительных контактных площадок или другой последовательности включения реализовать желательную переходную характеристику.

Задачей настоящего изобретения является предложить максимально простую схему регулирования напряжения для ИС чип-карт, в которой не проявляется проблема перерегулирования в процессе включения.

Эта задача решается схемой регулирования напряжения с признаками пункта 1 формулы изобретения. Дальнейшие варианты осуществления изобретения отражены в зависимых пунктах формулы изобретения.

Соответствующая изобретению схема регулирования напряжения снабжена последовательным регулятором, известным как таковой и предназначенным для выработки внутреннего напряжения питания VDDint, причем между выводом внешнего напряжения питания VDDext и регулирующим выводом последовательного регулятора включены последовательно соединенные емкость и полевой транзистор, предусмотренный в качестве передающего затвора. Для этого передающего затвора предусмотрен электрический потенциал, изменяемый соответственно управляющему сигналу ИС чип-карты. Последовательный регулятор включает в себя, в частности, транзистор последовательного регулятора, который включен своим истоком и стоком последовательно между внешним напряжением питания VDDext и внутренним напряжением питания VDDint, и вывод затвора которого является регулирующим выводом последовательного регулятора или по меньшей мере соединен с регулирующим выводом. Приложенный к затвору потенциал транзистора последовательного регулятора является регулируемым.

На чертежах, поясняющих изобретение, показано следующее:

Фиг.1 - описанная выше схема регулятора напряжения, известная из уровня техники;

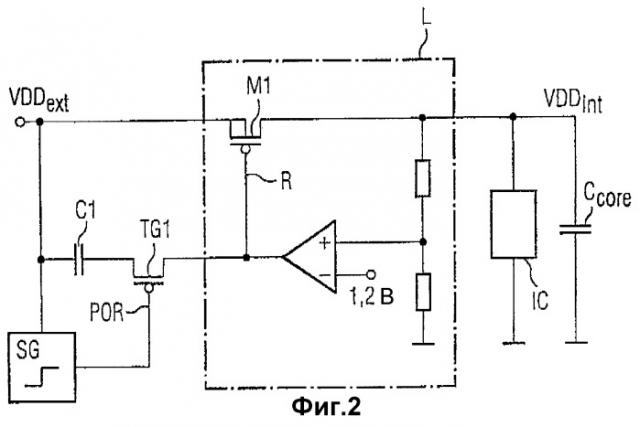

Фиг.2 – предпочтительный вариант осуществления соответствующей изобретению схемы регулятора напряжения;

Фиг.3 – диаграмма сигнала включения питания/сброса (POR-сигнала);

Фиг.4 – диаграмма VDDint и VDDext для схемы по фиг.1;

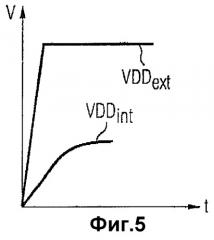

Фиг.5 – диаграмма, соответствующая диаграмме по фиг.4, для схемы, приведенной на фиг.2.

На фиг.2 показан пример выполнения соответствующей изобретению схемы регулятора напряжения, в котором представлен последовательный регулятор L для пояснения принципа функционирования схемы, как на фиг.1. Варианты выполнения последовательного регулятора дают соответствующие примеры осуществления соответствующей изобретению схемы, которые не требуют специального описания. Между истоком и затвором транзистора М1 последовательного регулятора, промежуток исток-сток которого используется для преобразования напряжения, включены последовательно соединенные конденсатор С1 и передающий затвор TG1, образованный полевым транзистором. Остальные компоненты схемы соответствуют обычной схеме, например, показанной на фиг.1.

Управление передающим затвором осуществляется с помощью сигнала, который вырабатывается предусмотренным для этого генератором SG сигнала в качестве сигнала включения питания/сброса и в типовом случае имеет временную зависимость, представленную на диаграмме по фиг.3. Этот сигнал включения питания/сброса представляет собой цифровой сигнал и имеет два значения, а именно: потенциал заземления или VSS и внешнее напряжение питания VDDext. Он вырабатывается в ИС чип-карты независимо от части схемы, предусмотренной в соответствии с изобретением, и применяется для процесса включения.

В момент включения конденсатор С1 разряжен. Когда прикладывается внешнее напряжение питания VDDext, транзистор М1 последовательного регулятора отпирается при последовательно подсоединенном передающем затворе в соответствии с осуществляемым зарядом конденсатора С1. Так как этот заряд требует определенного времени, то последовательный регулятор L отпирается медленно. Соответствующие изобретению схемные элементы С1 и TG1, как существенные для изобретения компоненты, предусматриваются независимо от конкретного выполнения последовательного регулятора. Предпочтительно они рассчитываются с постоянной времени, которая больше, чем (внутренняя) постоянная времени регулятора напряжения. Тем самым достигается то, что и (внутренняя) емкость Ccore также заряжается медленно, благодаря чему можно избежать перерегулирования внутреннего напряжения питания VDDint. Поэтому в данной схеме временные зависимости напряжения соответствуют кривым, представленным на диаграммах по фиг.5.

После завершения внутреннего переходного процесса передающий затвор постоянно запирается сигналом POR. Так как дополнительная емкость С1 зависит только от внешнего напряжения питания VDDext, а передающий затвор во время работы остается постоянно запертым, схема регулирования напряжения не оказывает влияния на динамический режим функционирования ИС чип-карты. Кроме того, в процессе работы также не оказывается влияние на статическое и динамическое потребление тока. Снижение возникающих выбросов тока обеспечивает преимущество, состоящее в уменьшении миграции электронов.

1. Схема регулирования напряжения для интегральных схем (ИС) чип-карт, содержащая схему последовательного регулятора (L) для выработки внутреннего напряжения питания (VDDint) из внешнего напряжения питания (VDDext), в которой последовательный регулятор (L) содержит транзистор (М1) последовательного регулятора, который своим истоком и стоком размещен последовательно между внешним напряжением питания (VDDext) и внутренним напряжением питания (VDDint), и регулирующий вывод (R), предусмотренный для регулирования потенциала, приложенного к выводу затвора транзистора (М1) последовательного регулятора, отличающаяся тем, что между выводом внешнего напряжения питания (VDDext) и регулирующим выводом (R) последовательно включены конденсатор (С1) и полевой транзистор, предусмотренный в качестве передающего затвора (TG1), при этом для упомянутого передающего затвора (TG1) предусмотрен изменяющийся электрический потенциал, который в течение переходного процесса отпирает схему передающего затвора, так что осуществляется заряд конденсатора (С1), и после завершения переходного процесса передающий затвор постоянно запирается.

2. Схема регулирования напряжения по п.1, в которой вывод передающего затвора (TG1) связан с частью схемы, которая вырабатывает сигнал напряжения, который во времени принимает два следующих один за другим различных значения.

3. Схема регулирования напряжения по п.2, в которой двухступенчатый сигнал напряжения представляет собой сигнал включения питания/сброса, соответствующий управляющему сигналу ИС чип-карты.