Компонентный декодер и способ декодирования в системе мобильной связи

Иллюстрации

Показать всеИзобретение относится к радиотехнике. Технический результат заключается в увеличении точности поиска состояния на границе кадра и дополнительном выполнении поиска состояния на границе кадра в соответствии с размером окна поиска состояния. Сущность изобретения заключается в том, что декодер содержит блок вычисления метрик ветвления, схему суммирования-сравнения-выбора, блок поиска состояния максимального правдоподобия, блок задержки, блок обновления логарифмического отношения правдоподобия и селектор. 5 н. и 6 з.п. ф-лы, 1 табл., 14 ил.

Реферат

Настоящее изобретение относится в целом к декодеру и способу декодирования в системе мобильной связи и, в частности, к компонентному декодеру и способу для декодирования данных, модулированных с помощью турбокода, использующего рекурсивные систематические сверточные коды (RSC).

Канальные коды широко используются для надежной передачи данных в системах мобильной связи, таких как спутниковые системы, широкополосные системы с множественным доступом и кодовым разделением каналов (W-CDMA) и CDMA2000. Канальные коды включают сверточные коды и турбокоды. Обычно сигнал, закодированный сверточным кодом, декодируется с использованием алгоритма Витерби на основе декодирования по критерию максимального правдоподобия (ML). Алгоритм Витерби получает "мягкое" (нестрого определенное) значение (soft value) на входе и создает "жесткое" (строго определенное) искомое значение (hard decision value). Однако во многих случаях необходимо иметь декодеры с мягкими выходными данными для того, чтобы улучшить рабочие характеристики на протяжении всего процесса каскадного декодирования. В этом контексте было предложено множество схем для получения мягких выходных данных либо информации о достоверности декодированных символов. Известны два способа декодирования с мягкими входными данными/мягкими выходными данными (SISO), а именно алгоритм декодирования по критерию максимума апостериорной вероятности (MAP), и алгоритм Витерби с мягкими выходными данными (SOVA). Алгоритм MAP лучше всего рассматривать с точки зрения частоты ошибок по битам (BER), поскольку он выдает жесткое искомое значение вместе с апостериорной вероятностью, но требует определенных затрат, связанных со сложностью его реализации. J.Hagenauer в 1989 году предложил схему SOVA, обобщающую алгоритм Витерби. SOVA выдает искомое жесткое значение, а также информацию о достоверности, которая представляет собой мягкие выходные данные, связанные с искомым жестким значением. Однако J.Hagenauer не предложил реальную конфигурацию схемы SOVA и не дал описание ее работы.

По сравнению с известными алгоритмами Витерби алгоритм SOVA создает жесткое искомое значение и информацию о достоверности этого жесткого решения. То есть мягкие выходные данные обеспечивают достоверность декодированного символа, а также полярность декодированного символа, -1 или +1, для последующего декодирования. Для получения указанной информации о достоверности алгоритм SOVA вычисляет метрики путей (РМ) для выбранного пути (SP) и конкурентного пути (СР) и в качестве информации о достоверности создает абсолютное значение разности между РМ для SP и РМ для СР. Информация о достоверности δ задается выражением

Метрики РМ вычисляются так же, как в обычном алгоритме Витерби.

Для подробного описания алгоритма SOVA предположим, что есть решетка, в которой имеется S=2k-1 (k - длина кодового ограничения) состояний, и в каждое состояние входят две ветви.

При наличии достаточной величины задержки W все выбранные пути сливаются в один путь в обычном алгоритме Витерби. Величина W используется также в качестве размера окна ячейки состояния. Другими словами, при установке достаточного значения размера окна ячейки состояния W все выбранные пути сливаются в один путь. Этот путь называется путем максимального правдоподобия (ML). Алгоритм Витерби находит минимальную из РМ, вычисленных по уравнению 2, чтобы выбрать состояние Sk на этом пути в данный момент времени k.

где x

| (m) |

| jn |

| (m) |

| jn |

| (m) |

| jn |

Если в уравнении (3) путем с меньшей Pm является путь 1, то алгоритм Витерби выбирает путь 1. Здесь вероятность выбора неправильного пути вычисляется по формуле

где Δ =P2-P1>0. Пусть информационные биты в момент j на пути 1 и пути 2 составляют U

| (1) |

| j |

| (2) |

| j |

| (1) |

| j |

| (2) |

| j |

в предположении, что был выбран путь 1.

В уравнении (5) Pj(1-Psk) - вероятность выбора правильного пути, a (1-Pj)Psk - вероятность выбора неправильного пути. Уравнение (5) представляет вероятность, обновляемую путем добавления вероятности выбора правильного пути к вероятности выбора неправильного пути. Указанная итеративная операция управления реализуется с помощью логарифмического отношения правдоподобия (LLR), выражаемого как

где Δ равно P2-P1, a α - константа.

В заключение в случае, когда оцениваемые информационные биты на выбранном пути (путь 1) и конкурентном пути (путь 2) отличаются, а именно U

| (1) |

| j |

| (2) |

| j |

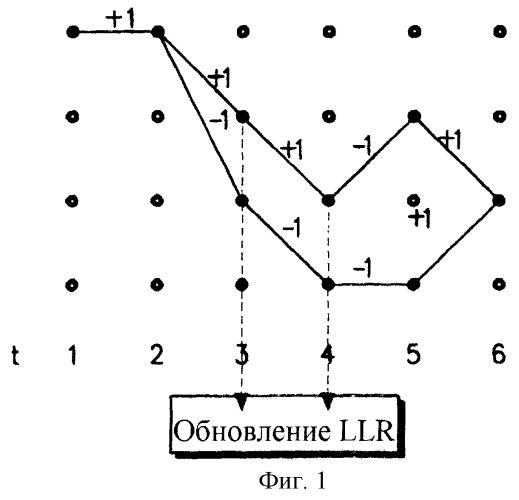

На фиг.1 показан пример обновления LLR на решетке с четырьмя состояниями. В частности, при переходе от момента t1 к моменту t2 информационные биты на выбранном пути (путь1) и конкурентном пути (путь 2) идентичны. Обновление LLR на этом переходе из состояния в состояние не применяется. С другой стороны, при переходе от t2 к t3 и от t3 к t4 информационные биты для этих двух путей отличаются, и LLR обновляется. Значение LLR для t3 и t4 сравнивается с предыдущим значением LLR и обновляется, если это LLR меньше предыдущего.

Вышеописанная схема SOVA может быть реализована с помощью алгоритма SOVA с обратным прослеживанием, или "назад по цепочке", (определенного здесь как TBSOVA). Путь ML прослеживается обратно в окне размером W при каждом декодировании в алгоритме TBSOVA. Результирующая задержка декодирования создает проблемы при практической реализации в случае высокоскоростных систем, например при использовании указанного алгоритма в мобильном терминале.

Следовательно, целью настоящего изобретения является создание устройства и способа для декодирования данных, закодированных с использованием турбокодов, с помощью алгоритма SOVA с регистровым обменом (RESOVA) в системе мобильной связи.

Другой целью настоящего изобретения является создание устройства декодирования RESOVA и способа для декодирования данных, закодированных с использованием турбокодов, и данных, закодированных с использованием сверточных кодов, в системе мобильной связи.

Еще одной целью настоящего изобретения является создание устройства и способа декодирования RESOVA в системе мобильной связи, где окно поиска состояния ML (окно ячейки состояния ML) выдает значение состояния ML в момент (k-Ds) в соответствии с произвольным моментом k, а окно обновления LLR выдает LLR, выбираемое на основе значения состояния ML примерно в момент времени (k-Ds-DL) в компонентном декодере.

Следующей целью настоящего изобретения является создание устройства и способа декодирования в системе мобильной связи, где компонентный декодер, имеющий окно поиска состояния ML и окно обновления LLR, принимает виртуальный код для увеличения точности поиска состояния ML на границе кадра и дополнительно выполняет поиск состояния ML на границе кадра в соответствии с размером окна поиска состояния ML.

Вышеуказанные цели могут быть достигнуты путем создания декодера и способа декодирования для декодирования данных, принимаемых от передатчика. Данные кодируются с помощью RSC в системе мобильной связи. В декодере схема (ВМС) вычисления метрик ветвления вычисляет значения метрик (ВМ) ветвления, связанные с множеством входных символов. Схема суммирования - сравнения - выбора (ACS) получает ВМ и предыдущие значения метрики путей (РМ) и создает множество бит выбора путей и данные LLR (логарифмическое отношение правдоподобия), включающие множество бит выбора путей и информацию о достоверности, в первый момент времени. Блок поиска состояния максимального правдоподобия (ML) имеет множество ячеек в матрице со строками и столбцами, соединенными друг с другом в соответствии с решеткой кодера, причем ячейки в каждой строке имеют время обработки Ds для выдачи того же значения ячеек в последнем столбце, что и значение состояния ML, представляющее путь ML в соответствии с селекторами путей. Блок задержки задерживает данные LLR, получаемые от ACS, на время тактового интервала Ds. Схема обновления LLR имеет множество элементов обработки (РЕ) в матрице со строками и столбцами, соединенными в соответствии с решеткой кодера, причем РЕ в каждой строке имеют время обработки DL, для создания обновленных значений LLR, поступающих из элементов РЕ, в некоторый момент времени (первый момент времени, примерно определяемый как Ds+DL) в соответствии с задержанными данными LLR, получаемыми из блока задержки. Селектор выбирает одно из обновленных значений LLR на основе значения состояния ML.

Вышеуказанные и другие цели, признаки и преимущества настоящего изобретения станут более очевидными из последующего подробного описания вместе с сопроводительными чертежами, на которых:

фиг.1 - схема решетки, на которую ссылаются при описании способа обновления LLR, используемого в настоящем изобретении;

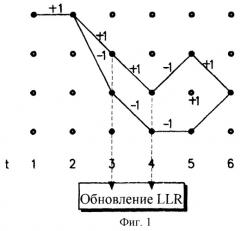

фиг.2 - блок-схема декодера RESOVA согласно варианту настоящего изобретения;

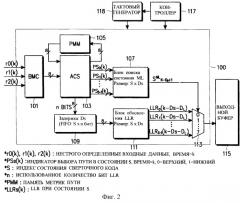

фиг.3 - способ синхронизации ячейки LLR по ячейке состояния в декодере RESOVA, показанном на фиг.2;

фиг.4 - схема решетки, показывающая процесс декодирования в окне ячейки состояния и в окне ячейки LLR в декодере RESOVA, показанном на фиг.2;

фиг.5 - блок-схема, иллюстрирующая весь процесс функционирования декодера RESOVA, показанного на фиг.2;

фиг.6 - структура блока ВМС, показанного на фиг.2;

фиг.7 - блок-схема блока ACS, показанного на фиг.2;

фиг.8 - блок-схема компонентного блока ACS, показанного на фиг.7;

фиг.9 - структура памяти РМ (РММ), показанной на фиг.2, в случае, когда в решетке имеется восемь состояний, согласно настоящему изобретению;

фиг.10А - структура блока поиска состояния ML, показанного на фиг.2;

фиг.10В - структура ячейки памяти, показанной на фиг.10А;

фиг.11А - блок обновления LLR, показанный на фиг.2;

фиг.11В - структура элемента обработки (РЕ), показанного на фиг.11А;

фиг.12А - структура блока задержки, показанного на фиг.2;

фиг.12В - структура ячейки памяти, показанной на фиг.12А;

фиг.13 - схема решетки, иллюстрирующая процесс декодирования в окне поиска состояния ML и окне обновления LLR в случае, когда виртуальные символы принимаются в декодере RESOVA, согласно другому варианту настоящего изобретения; и

фиг.14 - блок-схема декодера RESOVA с входным сигналом, состоящим из виртуальных кодированных символов, согласно второму варианту настоящего изобретения.

Ниже со ссылками на сопроводительные чертежи описываются предпочтительные варианты настоящего изобретения В приведенном ниже описании известные функции и конструкции подробно не описываются, чтобы не затемнить суть изобретения ненужными подробностями.

Здесь дается подробное описание конфигурации и работы декодера на основе алгоритма RESOVA, который имеет наилучшие характеристики среди всех предложенных на сегодняшний день схем декодирования.

На фиг.2 представлена блок-схема декодера RESOVA согласно варианту настоящего изобретения. Обратимся к фиг.2, где декодер RESOVA 100 работает под управлением контроллера 117 и активизируется тактовым сигналом, поступающим от тактового генератора 118. Тактовый генератор 118 генерирует тактовый сигнал под управлением контроллера 117 и подает его в декодер RESOVA 100 согласно настоящему изобретению. Следует отметить, что работа декодера RESOVA 100 в части, касающейся операций управления, осуществляемых контроллером 117, и тактового сигнала, генерируемого тактовым генератором 118, здесь не описывается.

Положим, что в этом изобретении турбокодер 1/3 имеет три запоминающих устройства (то есть k=4). Приняв демоду-лированные кодовые символы r0(k), r1(k) и r2(k), блок 101 вычисления метрик ветвления ВМС вычисляет метрики ветвлений (ВМ) для всех возможных путей между состояниями в текущий момент времени (k) и состояниями в предыдущий момент времени. При практической реализации, коль скоро текущее состояние известно, предыдущие состояния легко определяются по решетке. В случае сверточного кода или турбокода создаются две метрики ВМ для каждого состояния, в которое произошел переход из предыдущих состояний. Если задано восемь состояний, то в каждое состояние в любой момент времени входят две ветви, и вычисляется 16 метрик ВМ для всех возможных путей. Метрики ВМ представляют собой систему корреляционных мер, то есть корреляционных мер всех возможных кодовых слов с0, с1 и c2, запомненных в ВМС, с полученными кодовыми символами r0, r1 и r2. Кодовые слова, которые уже были запомнены в ВМС, представляют собой все возможные кодовые слова, созданные на основе порождающего многочлена кодера g(х) в решетке. Например, для скорости кода R=1/3, одна ВМ для каждого состояния может быть выражена в виде уравнения (7) в соответствии с восемью комбинациями из с0, c1, c2∈ {0,1}. В то время как для каждого состояния может быть создано две метрики ВМ, путем комбинирования с0, c1 и c2 может быть создано восемь кодовых слов. Следовательно, фактически потребуется восемь блоков 101 ВМС. Восемь метрик ВМ подаются в схему 103 ACS параллельно.

где верхняя строка представляет операцию вычисления ВМ с использованием кодовых символов с0, c1 и c2 и принятых кодовых символов r0, r1 и r2, а нижняя строка представляет собой обобщение верхнего уравнения. Кодовые символы с0, c1 и c2 известны приемнику, причем каждый из них принимает значение 0 или 1. Принятые кодовые символы r0, r1 и r2 представляют собой символы, которые приемник получил от передатчика. Принятые кодовые символы (r0, r1, r2) имеют мягкое значение. В случае турбокода r0 имеет восемь бит, а r1 и r2 по шесть бит согласно настоящему изобретению. Символ r0 имеет 8 бит, поскольку к систематическому кодовому символу добавляется внешняя информация, создаваемая во время декодирования. При начальном декодировании внешняя информация составляет 0 бит, и, следовательно, в качестве r0 принимается 6-битовый систематический код. На фиг.6 показан блок 101 ВМС, который реализует уравнение (7) для одного состояния. Умножители 121 умножают полученные кодовые символы r0, r1 и r2 на кодовые символы с0, с1 и с2, которые запоминает ВМС, и выводят результаты М0, M1 и М2 в сумматор 123. Таким образом, выход сумматора 123 также составляет 8 бит, кроме r0, который при начальном декодировании имеет шесть бит.

При практической реализации блока 101 ВМС, показанного на фиг.6, аппаратными средствами операции умножения опускаются, а М0, M1 и М2 получают путем инвертирования бит входных символов, в зависимости от кодового слова (с0, с1, с2). В таблице 1 показана операция ВМС в 6-битовой двоичной системе. Обратимся к таблице 1, где, если кодовое слово составляет 0, то изменений в битах входного символа во время операции ВМС не происходит. Если кодовое слово равно 1, то каждый бит входного символа инвертируется, а затем добавляется 000001.

| Таблица 1 | ||||

| Положим, что полученная выборка составляет [r0r1r2] | Пример внутреннего произведения в дополнении до 2 | |||

| с0с1с2 | (1-2*ci) | Операция ВМС | Положим, что ri=[011111]=(+31) | |

| (000) | (+++) | +r0+r1+r2 | Если Ci=0 | ci*ri=[011111]=(+31) |

| (001) | (++-) | +r0+r1-r2 | Если ci=1 | ri*ri=[100000]+[000001]=[100001]=(-31) |

| (010) | (+-+) | +r0-r1+r2 | Положим, что ri=[011111]=(-31) | |

| (Oil) | (+--) | +r0-r1-r2 | Если ci=0 | ci*ri=[100001]=(-31) |

| (100) | (-++) | -r0+r1+r2 | Если ci=1 | ci*ri=[011110]+[000001]=[011111]=(+31) |

| (101) | (-+-) | -r0+rl-r2 | Положим, что ri=[000000]=(0) | |

| (110) | (--+) | -r0-rl+r2 | Если ci=0 | ci*ri=[000000]=(0) |

| (111) | (-) | -r0-l-r2 | Если ci=0 | ci*ri=[111111]+[000001]=[000000]=(0) |

Схема 103 ACS подробно описывается со ссылками на фиг.7 и 8.

На фиг.7 представлена блок-схема 103 ACS в случае решетки с восемью состояниями согласно данному варианту настоящего изобретения. На фиг.7 схема 103 ACS имеет восемь компонентных ACS 125. Это подразумевает, что суммирование, сравнение и выбор выполняются одновременно для восьми состояний. ACS 103 получает из ВМС 101 восемь метрик ВМ (с МВО по МВ7), причем каждая метрика ВМ имеет b бит, а предыдущие метрики путей РМ (управляемые ACS) (с РМО по РМ7) из памяти 105 метрик путей (РММ). В соответствии с взаимосвязью состояний по данной решетке компонентные схемы ACS (с #0 по #7) получают две метрики ветвлений из метрик ВМ (с МВ0 по МВ7) для каждого состояния соответственно. Метрика для верхней ветви, которая переходит вниз к соответствующему состоянию, называется МВU, а метрика для нижней ветви, которая идет вниз к соответствующему состоянию, называется МВL. Компонентные ACS (с #0 по #7) также получают РМU и PML, соответствующие ВМU и BML, в соответствии с состоянием соединения по решетке. Связь между каждой компонентной схемой ACS 125 и ВМU и ВМL, а также РМU и РМL определяется взаимосвязью между состояниями по решетке, как было установлено выше.

Для вычисления метрик РМ для всех возможных состояний в текущий момент времени выбирается одна из двух гипотез (выбранный путь или конкурентный путь), установленных для каждого состояния. Метрика следующего пути (NPM) вычисляется с использованием заданных ВМU и BML, а также РМU и PML двух состояний в предыдущий момент времени, из которых оказался возможным переход в данное состояние, следующим образом:

СЛОЖИТЬ

NPMU:=PMU+ВМU

npmL:=pmL+ВМL

СРАВНИТЬ И ВЫБРАТЬ

ЕСЛИ (РМU<РМL)РМ:=РМL; В ПРОТИВНОМ СЛУЧАЕ РМ:=РМU (8)

На фиг.8 представлена подробная блок-схема компонентной ACS 125. Обратимся к фиг.8, где компонентная ACS 125 имеет два сумматора 126 и 127, компаратор 129, селектор 121 и блок 122 вычисления информации о достоверности. Первый сумматор 126 суммирует ВМU и РМU, а второй сумматор 127 суммирует ВМL и РМL. Компаратор 129 сравнивает выходы первого и второго сумматоров 126 и 127 и выдает бит выбора пути, указывающий путь вверх или вниз к блоку 122 вычисления информации о достоверности и селектору 121. Блок вычисления информации о достоверности 122 вычисляет информацию о достоверности δ на основе выходных данных от первого и второго сумматоров 126 и 127. Блок 122 вычисления информации о достоверности выдает LLR путем добавления информации о достоверности δ к биту выбора пути, полученному от компаратора 129. Информация о достоверности δ задается выражением

где α - константа, равная 1/2. Согласно настоящему изобретению информация о достоверности δ вычисляется не с использованием выбранного пути и конкурентного пути, а с использованием верхних и нижних метрик РМ, то есть РМU и РМL.

Как было описано выше, блок вычисления информации о достоверности 122 выдает данные о достоверности (LLR), включающие бит выбора пути плюс δ . Данные о достоверности (LLR) содержат 1 бит выбора пути на позиции самого старшего разряда (MSB) и (n-1)-битовые данные δ , начинающийся с самого младшего разряда (LSB). Бит выбора пути, представляющий знаковый бит, в MSB для LLR или расчетный информационный бит могут быть получены только тогда, когда кодер использует RSC. Причиной этого является то, что в случае использования типового сверточного кода входная информация на двух путях, которые достигают одного состояния, имеет одинаковое значение. Например, если входная информация на одном из путей равна 0, то входная информация на другом пути также равна 0. Наоборот, в случае использования рекурсивного итеративного сверточного кода информационный бит 0 приводит к переходу в заданное состояние по одному из двух путей, которые входят в данное состояние, а информационный бит 1 приводит к переходу в это состояние по другому пути. Здесь необходимо определить выбор верхнего/нижнего пути. Например, бит выбора пути 1 или 0 может быть определен как верхняя бифуркация и нижняя бифуркация, либо наоборот. Селектор 121 получает метрики РМ из первого и второго сумматоров 126 и 127, а бит выбора пути из компаратора 129, и выбирает одну из метрик РМ в качестве значения состояния. В заключение схема 103 ACS выдает восемь значений LLR и восемь значений состояния для следующего момента времени.

Память 105 РММ запоминает значения метрик РМ, полученные из схемы 103 ACS. На фиг.9 показана структура РММ с восемью состояниями, каждое из которых выражается 8 битами. Память РММ 105 запоминает 8-битовые значения метрик РМ, связанные с восьмью состояниями, которые вычисляются в текущий момент времени, и подает в схему 103 ACS запомненные значения РМ в качестве предыдущих значений РМ для следующего момента времени. В частности, каждая из компонентных РММ (с РММЕ 0 по РММЕ 7) представляет собой 8-разрядный регистр. В компонентной памяти РММЕ 0 запоминается восемь бит значения метрики путей РМО, полученного из схемы 103 ACS. Аналогичным образом в компонентных РММ (с РММЕ 1 по РММЕ 7) запоминаются 8-битовые значения метрик путей с РМ 1 по РМ 7, полученные из схемы 103 ACS соответственно.

Блок 107 поиска состояния ML имеет значения состояния, являющиеся метками заданных состояний; он получает ряд бит выбора путей параллельно от схем 103 ACS и выполняет поиск значения состояния ML среди указанных значений состояния, используя способ регистрового обмена.

На фиг.10А представлена блок-схема блока 107 поиска состояния ML согласно данному варианту настоящего изобретения. Конфигурация и работа блока поиска состояния ML на основе схемы регистрового обмена раскрыта в патентной заявке Кореи №1998-62713, которая может быть включена в данное изобретение по ссылке. Блок 107 поиска состояния ML включает множество ячеек матрицы, состоящей из строк и столбцов, а также множество шин выбора пути. Каждая шина выбора соединена с соответствующей строчной ячейкой для приема бита выбора пути. Множество ячеек матрицы соединены таким образом, что каждая ячейка получает два значения состояния от предыдущей ячейки, в соответствии с решеткой, предопределенной порождающим многочленом кодера, за исключением первого столбца ячеек. Ячейки в первом столбце получают два входных значения, верхнее входное значение и нижнее входное значение, как показано на фиг.10А. Ячейка в каждом столбце запоминает одно из двух входных значений состояния на основе полученного соответствующего бита выбора пути и подает запомненное значение состояния в две ячейки в соответствующих строках в следующем столбце в следующий момент времени в соответствии с взаимосвязью между состояниями решетки. При последовательном выполнении вышеописанной процедуры в течение заранее определенного времени значения состояний в отдельных ячейках столбца сходятся в определенный момент времени к одному и тому же значению. Это значение представляет собой значение состояния ML. На последнем столбце ML блок 107 поиска выдает значение сходимости в виде состояния ML. Работа блока 107 поиска ML для поиска состояния ML занимает время тактового интервала Ds (например, 4*k, где k=номер памяти кодера +1).

Например, при наличии восьми состояний блок 107 поиска состояния ML получает 0 и 1 в ячейке первой строки первого столбца, 2 и 3 в ячейке второй строки первого столбца, 4 и 5 в ячейке третьей строки первого столбца и 6 и 7 в ячейке четвертой строки первого столбца. Входные данные ячеек с пятой по восьмую строки первого столбца такие же, как у ячеек с первой по четвертую строки первого столбца. Каждая ячейка в первом столбце выбирает одно из значений состояния на основе бита выбора пути, полученного в соответствии с тактовым сигналом из соответствующей шины выбора, и подает выбранное значение состояния на ячейки в следующем столбце в соответствии с взаимосвязями состояний решетки. При итеративном выполнении этой процедуры в течение заранее определенного тактового интервала (Ds) значения состояний ячеек последнего столбца сходятся к одному и тому же значению, а именно одному из значений состояния от 0 до 7. Например, если значение сходимости равно 5, то ячейки в последнем столбце имеют одинаковое значение состояния, равное 5. Здесь 5 определено как значение состояния ML. Блок 107 поиска состояния ML имеет временную задержку Ds для получения начальных значений состояний в первом столбце, которые затем сходятся к одному значению состояния, и это значение сходимости выводится из крайнего правого столбца.

На фиг.10В показана структура ячейки в блоке 107 поиска состояния ML. Ячейка имеет селектор и память в виде регистра. Селектор имеет два входных порта для получения значений состояния от предшествующих ячеек, либо начальных входных данных и один порт выбора для получения бита выбора пути. То есть данная ячейка выбирает одно из двух входных значений состояния на основе бита выбора пути и запоминает выбранное значение состояния в регистровой памяти. Память выдает значение состояния по входному тактовому сигналу.

Обратимся вновь к фиг.2, где блок 109 задержки получает из схемы 103 ACS n-битовые значения LLR, 1-битовый бит выбора пути и (n-1)-битовую информацию δ о достоверности для каждого состояния и задерживает выходные данные на величину задержки тактового интервала Ds, введенную в блок 107 поиска состояния ML. На фиг.12А показана структура блока 109 задержки, имеющего ячейки памяти, которые образуют восемь строк, что равно количеству состояний. Блок 109 задержки задерживает полученные значения LLR на время задержки Ds для выдачи полученного значения LLR. На фиг.12В показана структура ячеек, из которых состоит память, действующая как буфер. Ячейки памяти получают значения LLR, хранят их в течение заранее определенной временной задержки и выдают значения LLR в следующую ячейку памяти по тактовому сигналу. Блок 111 обновления LLR получает задержанные на тактовом интервале Ds значения LLR из блока 109 задержки, сравнивает значения LLR с предыдущими значениями LLR и обновляет их, если они меньше предыдущих значений LLR.

На фиг.11А представлена структура блока 111 обновления LLR, имеющая элементы обработки (РЕ), которые образуют заранее определенные столбцы и строки, составляющие одинаковое количество состояний и имеющие множество начальных входных значений 0.d_max или 1.d_max. Значение d_max определяется максимальным уровнем квантования (например, 127, для 7 бит). Следовательно, начальные входные значения выражаются 8 битами, причем MSB равен 0 или 1, а все другие биты равны 1. Работа блока 111 обновления LLR занимает тактовый период DL (например, 16*k, где k=номер памяти кодера (3)+1=4). Обратимся к фиг.11А, где блок 111 обновления LLR, являющийся модификацией ячеек RESOVA, содержит элементы РЕ в матрице, состоящей из строк и столбцов, и множество шин выбора. Шины выбора получают биты выбора пути и δ , при этом они соединены параллельно элементам РЕ в соответствующих строках. Блок 111 обновления LLR обновляет не жесткое искомое однобитовое значение, а (n)-битовое мягкое значение LLR. Следовательно, шина передачи внутренних данных в блоке 111 обновления LLR имеет (n)бит. Здесь величину δ представляют n-1 бит, а оставшийся один бит представляет бит выбора пути. Каждый элемент РЕ включает также логическую схему для обновления предыдущего значения LLR. Блок 111 обновления LLR получает значения LLR, задержанные на Ds или Ds-1, из блока 109 задержки 109 генерации каждого тактового сигнала тактовым генератором 118. Эти значения LLR уже были вычислены посредством операции ACS для восьми состояния до того, как закончился тактовый интервал Ds или (Ds-1). Каждый РЕ кроме шины выбора имеет два входных порта. Каждый РЕ в первом столбце получает информационный бит 0 через верхний (или нижний) входной порт и информационный бит 1 через другой, нижний (или верхний) входной порт, как показано на фиг.11А. Каждый РЕ в других столбцах соединен с двумя РЕ в предыдущем столбце в соответствии со структурой решетки для получения значений предыдущих РЕ.

Конфигурация и работа элемента РЕ подробно описывается со ссылками на фиг.11В. Прежде всего следует отметить, что LLR определяется как (n-1)-битовое значение δ и однобитовый селектор выбора. Обратимся к фиг.11В, где один РЕ получает два (n)-битовых LLR через верхний входной порт и нижний входной порт от предыдущих РЕ. Исключение состоит в том, что каждый РЕ в первом столбце получает (n)-битовое начальное входное значение. Первый мультиплексор 141 получает два бита выбора пути (первый и второй бит выбора соответственно) двух LLR от РЕ в предыдущем столбце, соединенном с РЕ в соответствии с данной решеткой, и выбирает один из битов выбора пути на основе бита выбора пути (определенный как третий бит выбора пути), принимаемого из соответствующей шины выбора. Второй мультиплексор 143 принимает два (n-1)-битовых значений δ двух LLR через два своих входных порта и выбирает одно из значений δ на основе третьего бита выбора пути. Компаратор 147 сравнивает (n-1)-битовые значения δ , полученные из второго мультиплексора 143, со значением δ для LLR, полученного в данный момент через соответствующую шину выбора. Пусть значение δ , полученное от второго мультиплексора 143, составляет "а", а значение δ , полученное в данный момент в РЕ через шину выбора, равно "b". Если а больше b, то компаратор 147 выдает сигнал высокого уровня 1 (либо сигнал низкого уровня), а если b больше а, то он выдает сигнал низкого уровня 0 (или сигнал высокого уровня). Логический элемент 145 "исключающее ИЛИ" выполняет операцию "исключающее ИЛИ" над двумя битами выбора пути, полученными от предыдущих РЕ. Выходы компаратора 147 и логического элемента 145 "исключающее ИЛИ" имеют каждый один бит. Логический элемент 149 "И" выполняет операцию "И" над выходами логического элемента 145 и компаратора 147. Третий мультиплексор 151 получает (n-1)-битовое значение δ от второго мультиплексора 143 и (n-1)-битовое значение δ из шины выбора и выбирает одно из значений δ на основе выходного сигнала логического элемента 149 "И" в качестве сигнала выбора. Памяти 146 и 148 запоминают выходной сигнал первого мультиплексора 141 и третьего мультиплексора 151 соответственно. Бит выбора пути, выдаваемый из памяти 148, и значение δ , выдаваемое из памяти 146, образуют обновленное (n)-битовое значение LLR.

Вновь обратимся к фиг.2, где селектор 113 LLR получает восемь обновленных LLR из блока 111 обновления LLR и выбирает одно из LLR на основе значения состояния ML, полученного из блока 107 поиска состояния ML. Например, селектор 113 LLR получает значение сходимости 5 от блока 107 поиска состояния и выдает обновленное значение LLR, равное 5. Выходной буфер 115 последовательно буферизирует значения LLR, выбранные селектором 113. В настоящем изобретении для эффективного использования памяти и уменьшения временной задержки при декодировании используются два скользящих окна. Одно из них представляет собой окно тактового интервала Ds поиска состояния ML, действующее под управлением блока 107 поиска состояния ML 107 и предназначенное для поиска значения состояния ML, а другое - это окно DL обновления LLR, действующее под управлением блока 111 обновления LLR и предназначенное для выдачи оптимального значение LLR. В окне поиска состояния ML выполняется поиск значения состояния ML после времени задержки, примерно равное тактовому интервалу Ds, а в окне обновления LLR выбирается обновленное LLR, соответствующее значению состояния ML, среди множества обновленных LLR, и выдается выбранное значение LLR после временной задержки, составляющей примерно DS+DL.

На фиг.3 показана оперативная взаимосвязь между окном поиска состояния ML и окном обновления LLR во времени, а на фиг.4 показаны моменты времени, когда выдаются значение состояния ML и значение LLR при операциях для окна поиска состояния ML и окна обновления LLR. Пусть операция ACS выполняется в момент К. Тогда значение состояния ML выдается после временной задержки (K-Ds+1), как показано на фиг.3. Оптимальное значение LLR выбирается в момент времени, когда выводится значение состояния ML, и выводится после временной задержки (DL+1) с момента (K-Ds+1). Поскольку обновленное значение LLR выдается после временной задержки (DL+DS-2) с момента К, конечное значение LLR выдается после временной задержки (K-DL-Ds+2) с момента К. На фиг.5 представлена блок-схема, иллюстрирующая работу декодера RESOVA согласно настоящему изобретению. Обратимся к фиг.5, где при отсутствии тактового сигнала из системы на шаге 501 блок 109 задержки, память 105 РММ, блок 107 поиска состояния ML и блок 111 обновления LLR инициализируют свои ячейки, или РЕ, путем их установки в начальное состояние. После получения тактового сигнала блок 101 ВМС на шаге 503 принимает входные данные из входного буфера (не показан). На шаге 505 блок 101 ВМС вычисляет значения ВМ для путей между состояниями в предыдущий момент времени и состояниями в данный момент времени, используя входные данные и кодовые слова, известные декодеру, и подает значения ВМ в схему 103 ACS. Схема 103 ACS на шаге 510 получает верхние (через верхний входной порт) и нижние (через нижний входной порт) значения РМ, связанные с каждым состоянием, из значений ВМ, и вычисляет информацию о достоверности по уравнению (9) и значения LLR на шаге 510.

Если рассмотреть шаг 510 более подробно, то видно, что на шаге 506 схема 103 ACS вычисляет значения LLR и биты выбора пути, на шаге 507 вычисляет значения РМ, используя значения ВМ, и на шаге 508 нормализует значения РМ. Нормализация РМ - это процесс вычитания из РМ заранее определенного значения, если РМ больше заранее определенной величины, с целью предотвращения переполнения значений РМ. За подробностями следует обратиться к патентной заявке Кореи №1998-062724. Схема 103 ACS на шаге 511 подает значения LLR в блок 109 задержки, а на шаге 513 биты выбора путей в блок 107 поиска состояния ML. Биты выбора путей представляют собой информацию, рассчитанную в результате жесткого решения для соответствующих состояний. Блок 109 задержки задерживает значения LLR на время тактового интервала Ds (задержка, связанная с поиском состояния ML) и подает задержанные значения LLR в блок 111 обновления LLR, а блок 107 поиска состояния ML выполняет поиск значения состояния ML на основе битов выбора путей. На шаге 515 блок 111 обновления LLR получает задержанные значения LLR и обновляет их, используя способ, аналогичный показанному на решетке по фиг.1. Селектор 113 LLR получает обновленные значения LLR, выбирает одно из них на основе значения состояния ML, полученного от блока 107 поиска состояния ML, и буферизирует выбранное LLR в выходном буфере 115 на шаге 517.

Контроллер 117 на шаге 519 увеличивает количество тактовых импульсов CLK на 1 и на шаге 521 определяет, больше ли CLK длины кадра. Если CLK больше длины кадра, то контроллер 117 прекращает операцию декодирования, а, если CLK меньше длины кадра, то контроллер 117 итеративно выполняет шаги с 503 по 519.

В вышеописанном варианте настоящего изобретения, когда окно поиска состояния ML достигает границы кадра, операция на основе кадра заканчивается путем завершения с обнулением. В этом случае выдается только состояние ML на выходной стороне окна поиска состояния ML, а не другие состояния ML внутри окна поиска состояния ML.

Следовательно, согласно другому варианту настоящего изобретения конфигурация декодера RESOVA такова, что могут быть выведены все состояния ML в окне поиска состояний ML.

На фиг.13 показано декодирование в окне поиска состояний ML и окне обновления LLR в декодере RESOVA с виртуальными символьными входн