Дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для использования в различных микроэлектронных устройствах усиления. Технический результат заключается в расширении диапазона активной работы и повышении максимальной скорости нарастания выходного напряжения. Дифференциальный усилитель содержит первый и второй параллельно включенные по входу параллельно-балансные каскады (К) (1, 2), с входными транзисторами (Т) (1.1, 1.2), имеющие другой тип проводимости по отношению к Т (2.1, 2.2) второго К (2), эмиттеры Т (1.1, 1.2) связаны с базой первого дополнительного Т (5), эмиттер которого через первый вспомогательный резистор (Р) (6) подключен к объединенным эмиттерам Т (2.1, 2.2), а объединенные эмиттеры Т (2.1, 2.2) соединены с базой второго дополнительного Т (7), эмиттер которого через второй вспомогательный Р (8) соединен с объединенными эмиттерами Т (1.1, 1.2). 1 з.п. ф-лы, 15 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления импульсных сигналов, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителей (ОУ)).

Известны дифференциальные усилители (ДУ) на базе двух параллельно включенных параллельно-балансных каскадов, которые стали основой построения современных операционных усилителей, например AD8631, НА2539, НА5190 и др. [1, 2, 3|. Однако они имеют недостаточно высокое быстродействие из-за нелинейных режимов работы при большом импульсном сигнале [4, 5]. Проблема повышения быстродействия ОУ на основе ДУ данного подкласса, относящихся к числу наиболее широкополосных двухтактных структур, является одной из актуальных проблем современной аналоговой микросхемотехники.

Ближайшим прототипом заявляемого устройства является дифференциальный усилитель [2], содержащий первый и второй параллельно включенные (по входу) параллельно-балансные каскады, каждый из которых содержит первый и второй входные транзисторы с объединенными эмиттерами, связанными с источником стабильного тока, причем транзисторы первого параллельно-балансного каскада имеют противоположный тип проводимости по отношению к транзисторам второго параллельно-балансного каскада.

Существенный недостаток известного ДУ состоит в том, что он имеет недостаточно широкий диапазон активной работы, измеряемый напряжением ограничения (Uгр) [4], небольшие величины которого отрицательно влияют на максимальную скорость нарастания выходного напряжения (ϑвых) различных операционных преобразователей (ОП) [4, 5], а также невысокое собственное быстродействие при работе с импульсными сигналами большой амплитуды. Так, в работе [4] показано, что максимальная скорость нарастания выходного напряжения типового операционного усилителя ϑвых определяется по формуле

где fсp - малосигнальная частота среза амплитудно-частотной характеристики петлевого усиления ОУ;

Uгр - диапазон активной работы входного каскада ОУ.

Из уравнения (1) следует, что существуют два независимых способа повышения ϑвых - увеличение fcр и увеличение Uгр.

Основная цель предлагаемого изобретения состоит в расширении диапазона активной работы (Uгр) (без ухудшения статических параметров и коэффициента усиления по напряжению) и повышении собственного быстродействия при работе с импульсными сигналами большой амплитуды (уменьшении времени фронта выходного тока ДУ).

Поставленная цель достигается тем, что в дифференциальный усилитель, содержащий первый и второй параллельно включенные (по входу) параллельно-балансные каскады, каждый из которых содержит первый и второй входные транзисторы с объединенными эмиттерами, причем транзисторы первого параллельно-балансного каскада имеют противоположный тип проводимости по отношению к транзисторам второго параллельно-балансного каскада, вводятся новые связи и элементы - эмиттеры первого и второго транзисторов первого параллельно-балансного каскада связаны с базой первого дополнительного транзистора, эмиттер которого через первый вспомогательный резистор подключен к объединенным эмиттерам первого и второго транзисторов второго параллельно-балансного каскада, а объединенные эмиттеры первого и второго транзисторов второго параллельно-балансного каскада соединены с базой второго дополнительного транзистора, эмиттер которого через второй вспомогательный резистор соединен с объединенными эмиттерами первого и второго транзисторов первого параллельно-балансного каскада.

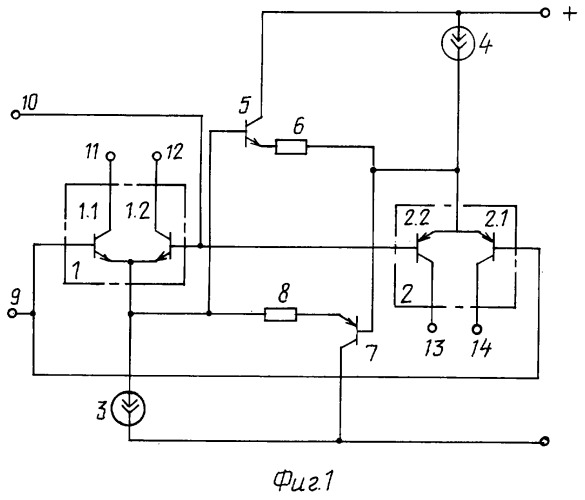

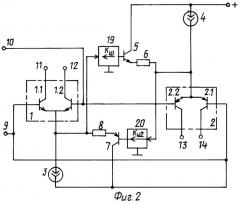

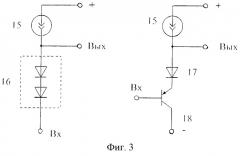

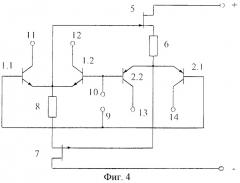

Схема заявляемого устройства показана на фиг.1. На фиг.2 приведена схема ДУ фиг.1 в соответствии с п.2 формулы изобретения. На фиг.3 показаны варианты выполнения согласующих повторителей напряжения в ДУ фиг.2. На фиг.4 изображен заявляемый усилитель для случая, когда согласующие повторители напряжения отсутствуют (п.1 формулы изобретения), а в качестве первого и второго дополнительных транзисторов используются полевые транзисторы, устанавливающие статический режим осей схемы без дополнительных источников стабильного тока.

На фиг.5 изображена частная схема заявляемого ДУ фиг.2, которая в отличие от схемы фиг.4 реализована только на биполярных транзисторах.

На фиг.6 показаны направления токов и напряжений в заявляемом устройстве при работе с сигналами большой амплитуды положительной и отрицательной полярностей. На фиг.7 приведена теоретическая проходная характеристика заявляемого ДУ фиг.6 - зависимость выходных токов от дифференциального напряжения uвх положительной и отрицательной полярностей. Проходные характеристики ДУ фиг.6, полученные в результате компьютерного моделирования схемы в среде PSpice с использованием моделей интегральных транзисторов ГУП НПП “Пульсар” (г.Москва), изображены на фиг.8. Переходные процессы в заявляемом ДУ фиг.6 приведены на фиг.9 и 10. Пример применения заявляемого устройства в структуре сверхбыстродействующего ОУ показан на фиг.11 - 13, на фиг.14 приведена схема элементов обвески, в таблице 1 (фиг.15) приведены данные о параметрах этого операционного усилителя, реализованного на основе заявляемого устройства.

Устройство, фиг.1, содержит первый 1 и второй 2 параллельно включенные по входу параллельно-балансные каскады, каждый из которых содержит первый 1.1 (2.1) и второй 1.2 (2.2) входные транзисторы с объединенными эмиттерами, связанными в частном случае с источниками стабильного тока 3 и 4. Транзисторы 1.1, 1.2 и 2.1, 2.2 имеют разные типы проводимости. Объединенные эмиттеры первого и второго входных транзисторов первого 1 параллельно-балансного каскада связаны с базой первого дополнительного транзистора 5, эмиттер которого через первый вспомогательный резистор 6 подключен к объединенным эмиттерам первого и второго транзисторов второго 2 параллельно-балансного каскада. Объединенные эмиттеры первого и второго транзисторов второго 2 параллельно-балансного каскада соединены с базой второго дополнительного транзистора 7, эмиттер которого через второй вспомогательный резистор 8 соединен с объединенными эмиттерами первого и второго транзисторов первого 1 параллельно-балансного каскада. Входами усилителя являются узлы 9 и 10. Токовые выходы, которые подключаются к традиционным активным нагрузкам [4, 5], - узлы 11, 12 и 13, 14.

В качестве согласующих эмиттерных повторителей напряжения могут применяться подсхемы, показанные на фиг.3. Они содержат источник опорного тока 15, цепи смещения статического уровня 16, 17 и транзистор 18. В схеме фиг.2, в отличие от схемы фиг.1, в соответствии с п.2 формулы изобретения введены согласующие повторители напряжения 19 и 20.

Заявляемое устройство работает следующим образом (фиг.6) (фиг.1-5). Если напряжение на входе 10 получает большое (импульсное) приращение относительно входа 9, то транзистор 2.2 практически мгновенно закрывается, а приращение с единичным коэффициентом усиления передается в общую эмиттерную цепь параллельно-балансного каскада 1. В результате напряжение между базой транзистора 7 и общей эмиттерной цепью первого параллельно-балансного каскада увеличивается. Как следствие, при некотором транзистор 7 переходит из режима отсечки в активный режим, что создает приращение его тока iэ.7 и тока эмиттера транзистора 1.2. В результате на характеристиках передачи (фиг.7) появляется дополнительный участок III, угол наклона которого определяется резистором 8 (или 6):

Таким образом, в заявляемом устройстве обеспечивается расширение диапазона активной работы от уровня [4], до уровня Uгр.2=1-5 В, которое зависит от произведения β7I15. Это позволяет без увеличения частоты среза fcp на один-два порядка увеличить быстродействие ОУ с заявляемым входным каскадом, которая также определяется быстродействием входного ДУ (временем нарастания и спада его выходного тока при импульсном входном воздействии). Компьютерное моделирование схемы ОУ на базе функциональных узлов фиг.11-13 показывает, что более высокое быстродействие относительно выходов 12 и 13 позволяет получить что недостижимо при других вариантах построения ДУ с широким диапазоном активной работы. При R1=R2=∞ (то есть при отключении нелинейной коррекции ДК) максимальная скорость нарастания ОУ Таким образом, введение новых элементов и связей в известное устройство решает одновременно две задачи:

1. Расширяет диапазон активной работы ДУ с 50-60 мВ до единиц вольт, что на 1-2 порядка улучшает динамические параметры широкого класса операционных преобразователей, например, операционных усилителей в нелинейных режимах.

2. При решении первой задачи начинает проявляться ограничение на ϑвых, обусловленноe конечным быстродействием ДУ [5]. В заявляемом ДУ это быстродействие существенно повышается за счет динамического увеличения токов, что позволяет достичь предельных значений максимальной скорости нарастания выходного напряжения ОП, соизмеримых с его быстродействием в линейных режимах.

Компьютерное моделирование операционного усилителя фиг.11 - 13 на основе заявляемого ДУ в среде PSpice с использованием моделей отечественных интегральных транзисторов, предоставленных ГУН НПП “Пульсар” (г.Москва), показывает высокую эффективность предлагаемых схемотехнических решений в сравнении с разработками ведущих производителей аналоговых микросхем США. Следует особенно отметить, что данные показаны на отечественных микронных технологиях.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - Рис.6.11.

2. Двухтактный операционный усилитель. Патент РФ №2193273, Н 03 f 3/45.

3. Дифференциальный усилитель. Патент США №4649352, кл. 330-261.

4. Операционные усилители с непосредственной связью каскадов / В.И.Анисимов, М.В.Капитонов, Н.Н.Прокопенко, Ю.М.Соколов. - Л., 1979.

5. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983. - 216 с.

1. Дифференциальный усилитель, содержащий первый и второй параллельно включенные по входу параллельно-балансные каскады, каждый из которых содержит первый и второй входные транзисторы с объединенными эмиттерами, причем транзисторы первого параллельно-балансного каскада имеют противоположный тип проводимости по отношению к транзисторам второго параллельно-балансного каскада, отличающийся тем, что эмиттеры первого и второго транзисторов первого параллельно-балансного каскада связаны с базой первого дополнительного транзистора, эмиттер которого через первый вспомогательный резистор подключен к объединенным эмиттерам первого и второго транзисторов второго параллельно-балансного каскада, а объединенные эмиттеры первого и второго транзисторов второго параллельно-балансного каскада соединены с базой второго дополнительного транзистора, эмиттер которого через второй вспомогательный резистор соединен с объединенными эмиттерами первого и второго транзисторов первого параллельно-балансного каскада.

2. Устройство по п.1, отличающееся тем, что эмиттеры первого и второго транзисторов первого параллельно-балансного каскада связаны с базой первого дополнительного транзистора через первый согласующий повторитель напряжения, а объединенные эмиттеры первого и второго транзисторов второго параллельно-балансного каскада соединены с базой второго дополнительного транзистора через второй согласующий повторитель напряжения.