Устройство для управления предъявлением информации в системе дистанционного обучения

Иллюстрации

Показать всеИзобретение относится к вычислительной технике, в частности к устройствам для управления предъявлением информации в системах дистанционного обучения. Техническим результатом является повышение быстродействия устройства за счет сокращения временных затрат на поиск и формирование адресов документов, содержание которых должно быть предъявлено обучаемому. Указанный технический результат достигается за счет того, что устройство содержит селектор базового адреса, регистры, элементы задержки, элементы ИЛИ групп, элементы ИЛИ, блок памяти, реверсивный счетчик, компаратор. 3 ил.

Реферат

Изобретение относится к вычислительной технике, в частности к устройствам для управления предъявлением информации в системах дистанционного обучения.

Известны устройства, которые могли бы быть использованы для решения поставленной задачи (1, 2).

Первое из известных устройств содержит вычислительный блок, соединенный с блоками ввода данных и логической обработки, выходы которых подключены к блоку памяти, блок отображения, подключенный к вычислительному блоку и к блоку принятия решений (1).

Существенный недостаток данного устройства состоит в его невысоком быстродействии, обусловленном тем, что для предъявления кадров с обучающей информацией необходимо каждый раз при повторном обращении к необходимым данным осуществлять их повторный поиск.

Известно и другое устройство, содержащее блоки памяти, регистры первой и второй групп, триггеры, одновибратор, группы элементов И, ИЛИ, элементы задержки и формирователи импульсов (2).

Последнее из перечисленных выше технических решений наиболее близко к описываемому.

Его недостаток также заключается в ограниченном быстродействии, обусловленном потерей времени на формирование адресов документов - представителей предметных областей, содержание которых должно быть предъявлено обучаемому.

Последнее обстоятельство обусловлено тем, что конструктивное выполнение данного устройства не предусматривает его использования в качестве клиентского рабочего места в системе дистанционного обучения.

Цель изобретения - повышение быстродействия устройства за счет сокращения временных затрат на поиск и формирование адресов документов, содержание которых должно быть предъявлено обучаемому.

Поставленная цель достигается тем, что в устройство, содержащее первый регистр, информационный вход которого является первым информационным входом устройства, а синхронизирующий вход - первым синхронизирующим входом устройства, второй и третий регистры, информационные входы которых соединены с выходом блока памяти, а выходы подключены к одним входам элементов И первой и второй групп соответственно, выходы которых соединены с входами соответствующих элементов ИЛИ группы, выходы которых подключены к адресному входу блока памяти, первый элемент задержки, вход которого соединен с первым синхронизирующим входом устройства, второй элемент задержки, выход которого соединен с синхронизирующими входами второго и третьего регистров с одним входом первого элемента ИЛИ, первый элемент И, один вход которого является первым управляющим входом устройства, а выход подключен к другому входу первого элемента ИЛИ, триггер, единичный вход которого является вторым управляющим входом устройства, установочный вход соединен с выходом первого элемента ИЛИ, а единичный выход подключен к одному входу второго элемента И и к другим входам элементов И второй группы, третий элемент задержки, вход которого подключен к второму управляющему входу устройства, а выход соединен с другим входом второго элемента И, и элемент ИЛИ, первый и второй входы которого подключены к выходам первого и второго элементов И, введены селектор базового адреса, информационный вход которого соединен с выходом первого регистра, синхронизирующий вход подключен к выходу первого элемента задержки, информационные входы подключены к третьим входам соответствующих элементов ИЛИ группы, а синхронизирующий выход селектора базового адреса соединен с третьим входом элемента ИЛИ, выход которого соединен с входом второго элемента задержки и с входом считывания блока памяти, выход которого является информационным выходом устройства, реверсивный счетчик, суммирующий вход которого соединен с выходом первого элемента ИЛИ, вычитающий вход подключен к выходу второго элемента И, а установочный вход соединен с выходом первого элемента задержки, и компаратор, один информационный вход которого подключен к выходу реверсивного счетчика, другой информационный вход является вторым информационным входом устройства, прямой выход компаратора соединен с управляющим входом селектора базового адреса, а инверсный выход подключен к другим входам элементов И первой группы и к другим входам первого и второго элементов И, при этом инверсный выход триггера соединен с другими входами элементов И первой группы.

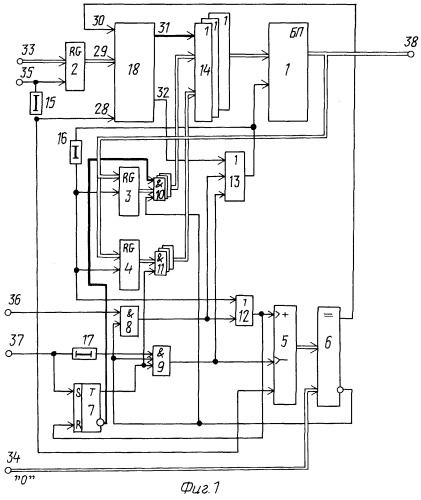

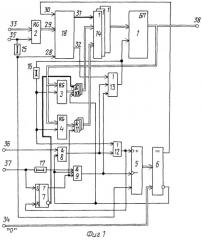

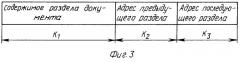

Сущность изобретения поясняется чертежами, где на фиг.1 представлена структурная схема устройства, на фиг.2 приведен пример конкретного конструктивного выполнения селектора базового адреса, а на фиг.3 представлена структура хранящихся в блоке памяти документов.

Устройство (фиг.1) содержит первый 1 блок памяти, первый 2, второй 3 и третий 4 регистры, реверсивный счетчик 5, компаратор 6, триггер 7, первый 8 и второй 9 элементы И, первую 10 и вторую 11 группы элементов И, первый 12 и второй 13 элементы ИЛИ, группу 14 элементов ИЛИ, первый 15, второй 16, третий 17 элементы задержки, селектор базового адреса 18.

Селектор базового адреса (фиг.2) содержит дешифратор 19, блок памяти 20, выполненный в виде постоянного запоминающего устройства, регистр 21, элементы 22-24 И, группа элементов 25 И, элементы 26, 27 задержки. Кроме того, на чертеже показаны синхронизирующий вход 28, информационный вход 29, управляющий вход 30, а также информационный выход 31 и синхронизирующий выход 32.

На фиг.1 также показаны первый 33 и второй 34 информационные входы устройства, синхронизирующий 35 вход устройства, первый 36 и второй 37 управляющие входы устройства и информационный 38 выход устройства.

Все узлы и элементы устройства выполнены на стандартных потенциально-импульсных элементах.

Устройство работает следующим образом.

Как и в известном устройстве, рабочее место обучаемого состоит из терминала, имеющего экран для отображения содержания разделов изучаемой темы, и клавиатуру, подразделяющуюся на стандартную (клавиатуру персонального компьютера) и функциональную, представляющую собой набор клавишных формирователей.

На экран дисплея рабочего места обучаемому последовательно предъявляются разделы изучаемой темы. Однако в отличие от прототипа описываемое устройство работает в системе дистанционного обучения в режиме клиент - сервер, при котором с сервера на клиентское рабочее место выдается только код темы для изучения. Вся изучаемая тематика в памяти блока 1 представлена в виде структуры, показанной на фиг.3, где первые К1-разрядов представляют собой содержание первого раздела изучаемой темы, вторые К2-разрядов содержат адрес предыдущего раздела по указанной теме, а третьи К3-разрядов содержат адрес следующего раздела по данной теме (3).

С началом очередного цикла работы с сервера в регистр 2 записывается код темы, которая предъявляется для изучения обучаемому. Для этого на вход 33 устройства сервер выдает код номера темы, который синхросигналом сервера, поступающим на вход 35, заносится в регистр 2, откуда он поступает на информационный вход селектора базового адреса 18.

Код номера темы расшифровывается дешифратором 19 и на одном из его выходов формируется высокий потенциал, открывающий один из соответствующих элементов 22-24 И. Параллельно с этим синхронизирующий сигнал сервера с входа 35 задерживается элементом 15 задержки (на время срабатывания дешифратора 19) и с выхода элемента 15 задержки поступает, во-первых, на установочный вход реверсивного счетчика 6, сбрасывая его в исходное состояние.

Во-вторых, этот же импульс, поступает на вход 28 селектора базового адреса и далее, пройдя открытый по второму входу один из элементов 22-24 И, поступает на вход считывания фиксированной ячейки памяти постоянного запоминающего устройства 20. В фиксированной ячейке этого блока памяти хранится базовый адрес первого раздела темы, выбранной для изучения. Содержимое фиксированной ячейки блока 2 памяти считывается на вход регистра 21, куда оно заносится синхронизирующим импульсом, поступающим с выхода элемента задержки 26 на синхронизирующий вход регистра 21.

Код базового адреса с выхода регистра 21 поступает на одни входы элементов 25 И, состояние которых по другим входам определяется потенциалом с прямого выхода компаратора 6, на информационные входы которого поступают код с выхода реверсивного счетчика 6 и код, соответствующий “нулевому” с входа 34.

Учитывая то обстоятельство, что реверсивный счетчик 6 в данный момент обнулен, компаратор 6 зафиксирует факт равенства кодов на его входах выдачей высокого потенциала на его прямом выходе и низкого потенциала на инверсном выходе. Высокий потенциал с прямого выхода компаратора поступает на вход 30 селектора 18 базового адреса и далее открывает элементы 25 ИЛИ, подключая тем самым выход регистра 21 через выход 31 селектора 18 к адресному входу блока 1 памяти.

Параллельно с этим импульс с выхода элемента 27 задержки, задержанный на время подключения выхода регистра 21 к адресному входу блока 1 памяти, через выход 32 селектора 18 и элемент 13 ИЛИ поступает на вход считывания блока 1 памяти. В результате этого содержимое базового адреса считывается как на экран дисплея через выход 38, так и на информационные входы регистров 3 и 4 в точном соответствии со структурой данных (фиг.3).

Тем же импульсом считывания, задержанным элементом 16 задержки на время считывания данных из блока 1 памяти, в регистр 3 заносится код адреса предыдущего раздела, а в регистр 4 - код адреса последующего раздела. Учитывая тот факт, что никаких предыдущих разделов еще не было, при считывании базового адреса он используется и в качестве предыдущего адреса при первоначальном считывании базового адреса.

Одновременно с этим импульс с выхода элемента 16 задержки через элемент 12 ИЛИ поступает на суммирующий вход реверсивного счетчика и изменяет код счетчика, делая его отличным от ″нулевого″. Этот факт зафиксирует компаратор 6, который, выдавая низкий потенциал на прямой выход и далее через вход 30 селектора 18 на входы элементов 25 И группы, заблокирует подключение выхода регистра 21 к адресному входу блока 1 памяти. В то же время высоким потенциалом с инверсного выхода компаратор 6 открывает элементы 8,9 И и группу 10 элементов И, подключая выход регистра 3 через элементы 10 И группы и элементы 14 ИЛИ группы к адресному входу блока 1 памяти. Тем самым на адресный вход блока 1 памяти выдается адрес следующего раздела изучаемой темы.

По готовности обучаемого к изучению следующего раздела темы он нажимает клавишу “Следующий” и на входе 36 появляется импульс, который, пройдя элемент 8 И, во-первых, через элемент 12 ИЛИ поступает как на суммирующий вход реверсивного счетчика, увеличивая его показания, так и на установочный вход триггера 7, подтверждая его исходное состояние, при котором высокий потенциал с его инверсного выхода открывает по одному входу группу элементов 10 И.

Во-вторых, через элемент 13 ИЛИ этот же импульс поступает на вход считывания блока 1 памяти и содержимое следующего раздела выдается на выход 38, а новые значения предыдущего и следующего адресов заносятся в соответствующие регистры 8 и 9.

Если в процессе изучения очередного раздела возникнет необходимость возврата к предыдущему разделу данной темы, то обучаемый нажимает клавишу ″Предыдущий″. В этом случае на входе 37 появляется импульс, который устанавливает триггер 7 в единичное состояние, переходя в которое последний низким потенциалом с инверсного выхода закроет элементы 10 И группы, заблокировав возможность подключения следующего адреса регистра 3 к адресному входу блока.

В то же время высоким потенциалом с единичного выхода будут открыты элементы 11 И группы и элемент 9 И. В результате этого выход регистра 4 с адресом предыдущего раздела через элементы 11 И группы и элементы 14 ИЛИ группы подключается к адресному входу блока 1 памяти.

Параллельно с этим импульс с входа 37 задерживается на время срабатывания триггера 7 элементом задержки 17 и поступает через элемент 9 И как на вычитающий вход реверсивного счетчика 5, так и через элемент 13 ИЛИ на вход считывания блока 1 памяти, считывая содержимое предыдущего раздела темы.

Таким образом, в отличие от прототипа в процессе процедуры изучения последовательности различных тем по всем предметным областям обучаемый сразу же получает возможность доступа к требуемым разделам изучаемых тем без каких-либо затрат времени на поиск адресов нахождения соответствующих тем.

Источники информации

1. Патент ЕПВ (ЕР) №0505651, кл. G 06 F 13/40, 13/38, 1992.

2. Описание к авторскому свидетельству №1474680, кл. G 06 F 15/40, 1989 (прототип).

3. Романов А.Н. и др. Технология дистанционного обучения – М.: ЮНИТИ-ДАНА, 2000. – 303 с.

Устройство для управления предъявлением информации в системе дистанционного обучения, содержащее первый регистр, информационный вход которого является первым информационным входом устройства, а синхронизирующий вход - первым синхронизирующим входом устройства, второй и третий регистры, информационные входы которых соединены с выходом блока памяти, а выходы подключены к одним входам элементов И первой и второй групп соответственно, выходы которых соединены с входами соответствующих элементов ИЛИ группы, выходы которых подключены к адресному входу блока памяти, первый элемент задержки, вход которого соединен с первым синхронизирующим входом устройства, второй элемент задержки, выход которого соединен с синхронизирующими входами второго и третьего регистров, с одним входом первого элемента ИЛИ, первый элемент И, один вход которого является первым управляющим входом устройства, а выход подключен к другому входу первого элемента ИЛИ, триггер, единичный вход которого является вторым управляющим входом устройства, установочный вход соединен с выходом первого элемента ИЛИ, а единичный выход подключен к одному входу второго элемента И и к другим входам элементов И второй группы, третий элемент задержки, вход которого подключен к второму управляющему входу устройства, а выход соединен с другим входом второго элемента И, и элемент ИЛИ, первый и второй входы которого подключены к выходам первого и второго элементов И, отличающееся тем, что оно содержит селектор базового адреса, информационный вход которого соединен с выходом первого регистра, синхронизирующий вход подключен к выходу первого элемента задержки, информационные выходы селектора базового адреса подключены к третьим входам соответствующих элементов ИЛИ группы, а синхронизирующий выход селектора базового адреса соединен с третьим входом элемента ИЛИ, выход которого соединен с входом второго элемента задержки и с входом считывания блока памяти, выход которого является информационным выходом устройства, реверсивный счетчик, суммирующий вход которого соединен с выходом первого элемента ИЛИ, вычитающий вход подключен к выходу второго элемента И, а установочный вход соединен с выходом первого элемента задержки, и компаратор, один информационный вход которого подключен к выходу реверсивного счетчика, другой информационный вход является вторым информационным входом устройства, прямой выход компаратора соединен с управляющим входом селектора базового адреса, а инверсный выход подключен к другим входам элементов И первой группы и к другим входам первого и второго элементов И, при этом инверсный выход триггера соединен с другими входами элементов И первой группы.