Импульсный кодовый преобразователь

Иллюстрации

Показать всеИзобретение относится к периферийным устройствам и может быть использовано для ввода-вывода информации, обмена с другим дистанционно удаленным периферийным устройством вычислительной машины. Технический результат изобретения - расширение функциональных возможностей за счет обеспечения возможности производить контроль изменения состояния (ситуации) связанного с ним объекта при эксплуатации. Сущность: кодовый преобразователь включает в себя устройство ввода информации, тактовый генератор, подключенный к адресному счетчику с дешифратором, выходы которого соединены с входами запоминающего устройства, входы которого подключены к выходу устройства программирования, формирователь сигнала и мультиплексоры. Устройство фиксации состояния объекта подключено к выходу дешифратора адреса ячеек устройства фиксации состояния объекта. Формирователь сигнала включает в себя ячейки для фиксации контрольной суммы. Первый вход формирователя сигналов подключен к выходу дешифратора адреса ячеек контрольной суммы, второй вход - к выходу запоминающего устройства, первый выход - к первым входам мультиплексоров, а второй выход - к первому входу двоичного сумматора, выходом соединенного с третьим входом формирователя сигнала и контрольной суммы. Выходы дешифратора адреса ячеек контрольной суммы и дешифратора адреса ячеек устройства фиксации состояния объекта соединены со вторым выходом адресного счетчика, который соединен со вторыми входами мультиплексоров. Запоминающее устройство является программируемым. 1 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к области автоматики, вычислительной технике и микроэлектронике, в частности к периферийным устройствам, и может быть использовано для ввода-вывода информации, обмена с другим дистанционно удаленным периферийным устройством вычислительной машины.

В уровне техники известно программируемое устройство, описанное в а.с. SU 1789979 А1, в котором осуществляется программирование порога срабатывания. Это известное программируемое устройство содержит n-1 (n - разрядность входного информационного слова) элементов ИЛИ, два демультиплексора и многофункциональный логический модуль, содержащий 2n-1 канальный мультиплексор. Оно также имеет n информационных входов, 1 до 2 n настроечных входов и один выход. Устройство работает следующим образом. На информационные входы подаются двоичные переменные xi...хn; на настроечные входы - сигналы настройки Ui...Uk. Если (111,...Uk) - двоичное представление числа r - 1, то на выходе устройства реализуется фундаментальная симметрическая булева функция F

| n |

| r |

| t |

| n |

| t |

| n |

Известно устройство для регистрации информации (А.С. N 1314328, G 06 F 3/02, Б.И. N 20, 1987), в состав которого входит блок приемопередачи, клавиатура, коммутатор, блок синхронизации, блок управления, индикаторы, блок формирования адреса и блок формирования вызова. Недостатком данного устройства является низкая достоверность передаваемой информации, которая формируется в приемном устройстве, кроме того, его использование не позволяет произвести контроль изменения состояния (ситуации) связанного с ним объекта при эксплуатации.

Известно устройство для обмена информацией (А. С. 1497619, G 06 F 13/10, N 28, 1989), содержащее блок приемопередачи, блок источников информации, блок индикации, блок синхронизации, блок центрального управления, пять дешифраторов, блок сигнализации, причем стробирующие входы первого, второго, третьего и четвертого дешифраторов соединены соответственно с первым, вторым, третьим и четвертым выходами команды блока управления, группа выходов первого дешифратора соединена с группой входов выборки блока источников информации, группа информационных выходов которого подключена через шину данных к информационным входам первого и второго регистров, блокам индикации и информационному входу-выходу блока приемопередачи, информационные вход и выход которого являются соответствующими входом и выходом устройства для подключения к информационном выходу и входу ЭВМ, первый и второй тактовые входы, вход строба байта состояния и сброса блока управления подключены соответственно к первому, второму, третьему и четвертому выходам блока синхронизации, вход сброса которого соединен с выходом начальной установки блока источников информации, а пятый выход - с тактовым входом блока приемопередачи, выходы первого и второго регистров подключены к соответствующим информационным входам блока приемников, группа выходов второго дешифратора подключена к группе режимных входов блока сигнализации, первый, второй выходы третьего дешифратора подключены соответственно к стробирующим входам первого регистра и блока индикации, сбросовый вход которого соединен со сбросовым входом второго регистра и блока синхронизации и подключен к пятому выходу команды блока управления, шестой выход команды которого подключен к синхронизирующему входу блока синхронизации, а также устройство содержит блок памяти, блок прерываний, блок задания режима работы, причем адресные входы блока приемопередачи, блока памяти, второго регистра и информационные входы первого-пятого дешифраторов через шину адреса подключены к адресному выходу блока управления, вход-выход данных которого соединен через шину данных с информационным выходом блока выбора режима работы, информационными входами-выходами блока прерываний, блока памяти, группа входов запросов блока прерываний подключена к соответствующим выходу сопровождения данных блока задания режима работы, выходам запроса прерывания блока источников информации, блока приемопередачи и группе выходов запроса прерывания блока приемников, тактовый и стробирующий входы и вход разрешения блока прерываний подключены соответственно к пятому выходу блока синхронизации и седьмому и восьмому выходам команды блока управления, первый и девятый выходы команды которого подключены соответственно к входам чтения и записи блока памяти, а вход запросов прерывания - к выходу блока прерываний, выход четвертого дешифратора подключен к стробирующему входу блока задания режима работы, первый и второй выходы пятого дешифратора - к стробирующим входам блока приемопередачи и второго регистра, управляющий вход которого соединен с третьим выходом команды блока управления и входом записи блока приемопередачи, входы выборки, чтения и сброса которого соединены соответственно с третьим выходом пятого дешифратора и четвертым и пятым выходом команды блока управления, вход выборки блока прерывания соединен с третьим выходом третьего дешифратора, десятый выход команд блока управления соединен с входом выборки блока приемников. Недостатком данного устройства является низкая достоверность информации, сформированной в приемном устройстве, определяемая наличием помех разной природы в передающей среде, кроме того, его использование не позволяет произвести контроль изменения состояния (ситуации) связанного с ним объекта при эксплуатации.

Известно устройство для обмена информацией (патент RU 2130642 С1, опубл.20.05.1999), в котором повышена достоверность передачи информации за счет организации режима работы приемного устройства по командам, поступающим от периферийного передающего устройства, являющимся центром сбора информации. Устройство для обмена информацией содержит блок центрального управления и блок приемопередачи, причем последний содержит первый блок памяти, приемник и передатчик, блок сигнализации, дополнительно введены четыре элемента ИЛИ, три формирователя импульсов, элемент сравнения, семь элементов задержки импульсов, два преобразователя кодов, приемник и передатчик, три одновибратора, триггер, два элемента И, два устройства выделения импульса управления, второй блок памяти и делитель частоты, выход которого соединен с входом блока сигнализации, а установочные входы данного делителя частоты соединены с входами задания числа проверок достоверности передаваемой информации устройством, выход элемента сравнения соединен с первым формирователем импульсов, выход которого 2 непосредственно соединен с входом "Сброс" первого блока памяти и через второй элемент задержки импульсов соединен с первым входом триггера, через последовательно соединенный первый одновибратор и первый вход первого элемента ИЛИ с вторым формирователем импульсов, через второй элемент задержки импульсов с входом "Сброс" делителя частоты, а через первый вход второго элемента ИЛИ с входом "Сброс" второго блока памяти, информационные выходы первого и второго блока памяти соединены с соответствующими входами элемента сравнения, вход синхронизации которого соединен с выходом третьего элемента задержки импульсов и через четвертый элемент задержки импульсов с счетным входом делителя частоты и с первым входом первого элемента И, второй вход которого соединен с первым выходом триггера и входом второго одновибратора, выход первого элемента И соединен с вторым входом второго элемента ИЛИ, а через первый вход третьего элемента ИЛИ с входом управления первого преобразователя кодов и с первым входом четвертого элемента ИЛИ, выход второго одновибратора соединен с входом третьего элемента задержки импульсов, а через пятый элемент задержки импульсов с входом "Запись" второго блока памяти, второй выход триггера соединен с первым входом второго элемента И, второй вход которого соединен с выходом приемника и входом третьего формирователя импульсов, выход которого соединен через первое устройство выделения импульсов управления с управляющим входом второго преобразователя кодов и непосредственно с его информационным входом, выходы второго преобразователя кодов соединены с информационными входами второго блока памяти, выходы которого также соединены с информационными входами блока центрального управления, информационные выходы которого соединены с информационными входами первого блока памяти, выход управления блока центрального управления соединен с входом "Запись" первого блока памяти и через шестой элемент задержки импульсов с вторым входом третьего элемента ИЛИ, информационные входы первого преобразователя кодов соединены с выходами первого блока памяти, первый выход первого преобразователя кодов соединен с вторым входом первого элемента ИЛИ, а второй выход первого преобразователя кодов подключен через седьмой элемент задержки импульса с вторым входом триггера и непосредственно к второму входу четвертого элемента ИЛИ, выход которого через третий одновибратор соединен с третьим входом первого элемента ИЛИ, выход второго элемента соединен с четвертым входом первого элемента ИЛИ и через второе устройство выделения импульсов управления с входом "Запись" блока центрального управления, выход второго формирователя импульсов соединен с входом передатчика. Использование этого известного устройства не позволяет произвести контроль изменения состояния (ситуации) связанного с ним объекта при эксплуатации.

Предлагаемое изобретение направлено на расширение функциональных возможностей за счет обеспечения возможности производить контроль изменения состояния (ситуации) связанного с ним объекта при эксплуатации.

Этот технический результат обеспечивается за счет того, что импульсный кодовый преобразователь включает устройство ввода информации о состоянии объекта, тактовый генератор, подключенный к адресному счетчику с дешифратором, первые выходы которого соединены с адресными входами запоминающего устройства, информационные входы которого подключены к выходу устройства программирования, и формирователь сигнала, а также снабжен мультиплексорами, устройством фиксации состояния объекта, вход которого подключен к выходу дешифратора адреса ячеек устройства фиксации состояния объекта, формирователь сигнала включает в себя ячейки для фиксации контрольной суммы, причем первый вход формирователя сигналов подключен к выходу дешифратора адреса ячеек контрольной суммы, второй вход - к выходу запоминающего устройства, первый выход - к первым входам мультиплексоров, а второй выход - к первому входу двоичного сумматора, выход которого соединен с третьим входом формирователя сигнала и контрольной суммы, входы дешифратора адреса ячеек контрольной суммы и дешифратора адреса ячеек устройства фиксации состояния объекта соединены со вторым выходом адресного счетчика, адресный счетчик соединен со вторыми входами соответственно первого, второго и третьего мультиплексоров, запоминающее устройство является программируемым, а его ячейки разделены на две группы, программируемые раздельно и независимо одна от другой, одна из указанных групп предназначена для хранения служебной информации, предназначенной только для чтения, а другая - для информации пользователя и может быть им перепрограммирована, в каждой из указанных групп организовано три банка данных, причем запоминающее устройство содержит устройство

объединения банков, предназначенное для объединения кодовых последовательностей из выбранных банков данных в единую последовательность, а для выбора конкретного банка данных и подключения его к устройству объединения банков предусмотрен соответствующий ключ, при этом мультиплексоры предназначены для приведения передаваемой кодовой последовательности в соответствие с заданным стандартом передачи сигналов, а их выходом образован выход импульсного кодового преобразователя. Устройство ввода информации о состоянии объекта связано с устройством фиксации состояния объекта через устройство защиты от “дребезга”.

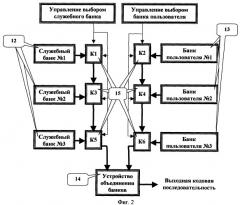

На фиг.1 изображена функциональная схема программируемого импульсного кодового преобразователя, на фиг.2 изображена функциональная схема матрицы памяти программируемого импульсного кодового преобразователя.

Импульсный кодовый преобразователь включает в себя устройство ввода информации о состоянии объекта 1, тактовый генератор 2, подключенный к адресному счетчику 3 с дешифратором. Первые выходы адресного счетчика 3 с дешифратором соединены с адресными входами запоминающего устройства 4, информационные входы которого подключены к выходу устройства программирования 5. Импульсный кодовый преобразователь включает также формирователь 6 сигнала и контрольной суммы, а также снабжен мультиплексор 7, связанными с устройством 8 фиксации состояния объекта, другим входом подключенного к выходу дешифратора 9 адреса ячеек устройства фиксации состояния объекта. Формирователь 6 сигнала и контрольной суммы включает в себя ячейки для фиксации контрольной суммы, причем первый вход формирователя 6 сигнала и контрольной суммы подключен к выходу дешифратора 10 адреса ячеек контрольной суммы, второй вход - к выходу запоминающего устройства 4, первый выход - к первым входам мультиплексоров 7, а второй выход - к первому входу двоичного сумматора 11, вторым входом соединенного со вторым выходом формирователя 6 сигнала и контрольной суммы, а выходом - с третьим входом формирователя 6 сигнала. Входы дешифратора 10 адреса ячеек контрольной суммы и дешифратора 9 адреса ячеек устройства фиксации состояния объекта соединены со вторым выходом адресного счетчика 3 с дешифратором, адресный счетчик 3 соединен со вторыми входами соответственно первого, второго и третьего мультиплексоров 7. Запоминающее устройство 4 является программируемым, а его ячейки разделены на две группы, программируемые раздельно и независимо одна от другой. Одна из указанных групп ячеек 12 предназначена для хранения служебной информации, предназначенной только для чтения, а другая 13 - для информации пользователя и может быть им перепрограммирована. В каждой из указанных групп ячеек 12 и 13 организовано три банка данных, причем запоминающее устройство содержит устройство 14 объединения банков, предназначенное для объединения кодовых последовательностей из выбранных банков данных в единую последовательность, а для выбора конкретного банка данных и подключения его к устройству 14 объединения банков предусмотрен соответствующий ключ 15. Мультиплексоры 7 предназначены для приведения передаваемой кодовой последовательности в соответствие с заданным стандартом передачи сигналов, а их выходом образован выход импульсного кодового преобразователя. Устройство 1 ввода информации о состоянии объекта связано с устройством 8 фиксации состояния объекта через устройство 17 защиты от “дребезга”.

Импульсный кодовый преобразователь осуществляет генерирование и выдачу на вывод “QOUT” циклически повторяющейся кодовой последовательности разрядностью - 128 двоичных разрядов, каждый разряд которой выполнен в Манчестер коде, и, в соответствии со стандартом ISO 10374, состоит из восьми бит информации. Основным устройством импульсного кодового преобразователя является запоминающее устройство 4 (матрица памяти (МП)), предназначенная для ввода при программировании и хранения полной информации об объекте, например, тип объекта, идентификационный номер, месяц, год изготовления и т.д. На фиг.2, где изображена функциональная схема запоминающего устройства, показано, что полный банк данных (12×8×6) разбит на отдельные банки, по 64 двоичных разряда в каждом (8×8) ячеек. Для повышения надежности работы запоминающего устройства 4, т.е. матрицы памяти, в ней предусмотрено избыточное кодирование согласно коду Хэмминга, поэтому каждый банк состоит из (12×8) ячеек памяти, образуя тем самым шесть банков хранения информации. Образовавшиеся банки памяти условно разбиты на две группы 12 и 13: три служебных банка 12 (СБ) и три банка пользователя 13 (БП). Банки СБ, размерами (3×64) двоичных разряда, предназначены для хранения такой информации, как: вид объекта, принадлежность и т.д. Банки 13 БП, размерами (3×64) двоичных разряда, предназначены для хранения информации пользователя, например, места установки изделия на объект, даты установки, данных установщика и т.д.

Такое разделение основного объема памяти на два типа предназначено для обеспечения возможности раздельного и независимого программирования как при изготовлении импульсного кодового преобразователя, так и непосредственно перед его эксплуатацией, например, перед установкой на охраняемый объект, если он используется в составе охранной электронной метки (см., например, патент RU 2203820). При этом пользователь может лишь просмотреть служебную информацию в банке 12 (СБ), а изменить ее не может. Для обеспечения этого в состав импульсного кодового преобразователя введены устройства, позволяющие по окончании программирования банка СБ заблокировать возможность изменения информации в нем. Кодовая последовательность из каждого банка 12, 13 поступает на устройство 14 объединения банков через последовательно включенные ключи 15 (Ki), соответственно из служебных банков 12 СБ через ключи с нечетными номерами, а из банков пользователя 13 БП – через

ключи с четными номерами. В исходном состоянии устройство 14 объединения банков включает ключи 15 - К1 и К2. Кодовая последовательность через замкнутые выше указанные ключи 15 К1 и К2 и выключенные остальные ключи 15 поступает на устройство 14 объединения банков. По окончании программирования первого служебного банка 12 СБ1, если оно прошло успешно, фиксируется состояние ключа 15 К1. Одновременно фиксируются состояния ключей 15 – К3 и К5. Далее доступа к остальным служебным банкам 12 нет. Если программирование первого служебного банка 12 СБ1 завершилось неудачей, то ключ 15 К1 выключается, а ключ 15 КЗ включается. Проводится программирование следующего служебного банка 12 СБ3 и т.д. По окончании программирования служебного банка 12 и фиксации состояния ключей 15 с нечетными номерами на устройство 14 объединения банков поступает кодовая последовательность из выбранного служебного банка 12. Информация из выбранного служебного банка 12 может быть прочитана, но не может быть изменена. Аналогично осуществляется работа с банками пользователя 13. Основной задачей устройства 14 объединения банков является объединение кодовых последовательностей из банков 12 и 13, т.е. разного назначения, в единую кодовую последовательность. При этом появляется один банк размером 128 двоичных разрядов (без учета избыточности, обусловленной применением кода Хэмминга).

Работа запоминающего устройства 4 осуществляется под управлением адресного счетчика 3 с дешифратором. На тактовый вход адресного счетчика 3 с дешифратором поступает тактовая частота с выхода тактового генератора 2. Тактовый генератор 2 собран на основе RC генератора с внутренними RC элементами. Предусмотрена возможность применения кварцевого резонатора, подключаемого между выводами G1 и Gт. При использовании внутреннего RC генератора имеется возможность работы с внутренним конденсатором “С” и набором встроенных резисторов “RП”, подключаемых программно, либо с внешним резистором “Rн”. Формирование кодовой последовательности осуществляется с помощью мультиплексоров 7: единицы, нуля и маркера. С выхода мультиплексоров 7 сформированная кодовая последовательность поступает на вывод “QOUT”, который является выходом импульсного кодового преобразователя.

Для осуществления ввода в выходную кодовую последовательность информации о состоянии объекта в схему импульсного кодового преобразователя введены: дешифратор 9 адреса ячеек устройства фиксации состояния объекта, дешифратор 10 адреса ячеек контрольной суммы, устройство 1 ввода информации о состоянии объекта, устройство 8 фиксации информации о состоянии объекта, устройство 17 защиты от “дребезга”, двоичный сумматор 11.

Биты информации о состоянии объекта зарезервированы в выходной кодовой последовательности, но информация о состоянии контролируемого объекта не программируется при установке импульсного кодового преобразователя на объект. Таким образом, необходимо из указанной последовательности “вырезать” информацию о состоянии объекта и вставить на это место текущую информацию. Дешифратор 9 адреса ячеек устройства фиксации состояния объекта определяет место в выходной кодовой последовательности, а устройства 1 и 8 соответственно ввода и фиксации информации о состоянии объекта, получив информацию со входа “Iinf”, вводят текущую информацию в выходную кодовую последовательность. В том случае, если импульсный кодовый преобразователь используется в составе электронной метки, при пломбировании объекта, когда отрезок троса проходит через зажимное устройство и перемещается относительно скользящего контакта, возможен переходный процесс, в течение которого информация о состоянии объекта может произвольно изменяться (“дребезг”). Для исключения влияния переходного процесса в импульсный кодовый преобразователь введено устройство 17 защиты от “дребезга”, представляющее собой таймер с временем выдержки, например, 20...60 секунд, по истечении которого информация о состоянии объекта фиксируется устройствами ввода и фиксации информации о состоянии объекта. При перекусывании отрезка троса, т.е. при изменении состояния объекта, когда переходной процесс отсутствует, информация фиксируется без задержки на “дребезг”.

В выходной кодовой последовательности передается контрольная сумма, представляющая собой сумму всех двоичных разрядов кода. При изменении информации в выходной кодовой последовательности, вызванной вводом дополнительных бит состояния объекта, необходимо изменить контрольную сумму. Для этого в импульсный кодовый преобразователь введены: формирователь 6 сигнала и контрольной суммы и двоичный сумматор 11. Из выходной кодовой последовательности “вырезается” информация о контрольной сумме, к ней добавляется, с помощью двоичного сумматора 11, информация о текущем состоянии объекта, и полученная новая контрольная сумма “врезается” на место прежней контрольной суммы.

1. Импульсный кодовый преобразователь, включающий в себя устройство ввода информации о состоянии объекта, тактовый генератор, подключенный к адресному счетчику, первые выходы которого соединены с адресными входами запоминающего устройства, информационные входы которого подключены к выходу устройства программирования, и формирователь сигнала, отличающийся тем, что снабжен мультиплексорами, устройством фиксации состояния объекта, вход которого подключен к выходу дешифратора адреса ячеек устройства фиксации состояния объекта, формирователь сигнала включает в себя ячейки для фиксации контрольной суммы, причем первый вход формирователя сигналов подключен к выходу дешифратора адреса ячеек контрольной суммы, второй вход - к выходу запоминающего устройства, первый выход - к первым входам мультиплексоров, а второй выход - к первому входу двоичного сумматора, выход которого соединен с третьим входом формирователя сигнала, входы дешифратора адреса ячеек контрольной суммы и дешифратора адреса ячеек устройства фиксации состояния объекта соединены со вторым выходом адресного счетчика, адресный счетчик соединен со вторыми входами первого, второго и третьего мультиплексоров, запоминающее устройство является программируемым, а его ячейки разделены на две группы, программируемые раздельно и независимо одна от другой, одна из указанных групп предназначена для хранения служебной информации, предназначенной только для чтения, а другая - для информации пользователя и может быть им перепрограммирована, в каждой из указанных групп организовано три банка данных, причем запоминающее устройство содержит устройство объединения банков, предназначенное для объединения кодовых последовательностей из выбранных банков данных в единую последовательность, а для выбора конкретного банка данных и подключения его к устройству объединения банков предусмотрен соответствующий ключ, при этом мультиплексоры предназначены для приведения передаваемой кодовой последовательности в соответствие с заданным стандартом передачи сигналов, а их выходами образован выход импульсного кодового преобразователя.

2. Преобразователь по п.1, отличающийся тем, что устройство ввода информации о состоянии объекта связано с устройством фиксации состояния объекта через устройство защиты от “дребезга”.