Защита ядра вычислительного устройства от несанкционированных изменений извне

Иллюстрации

Показать всеИзобретение относится к защите данных вычислительного устройства от несанкционированных изменений извне и, прежде всего, к защите данных, хранящихся в ядре вычислительного устройства, соответственно центрального процессора (ЦП), и может найти применение, в частности, в чип-картах. Его использование позволяет получить технический результат в виде повышения степени защиты вычислительного устройства от несанкционированных изменений. Технический результат достигается за счет того, что на основании содержимого регистров ЦП, получаемого в конце выполнения этим процессором какой-либо команды, путем математической логической операции формируют и сохраняют в памяти некоторую конечную контрольную сумму, а на основании содержимого регистров, получаемого перед началом выполнения указанным процессором непосредственно следующей команды, формируют некоторую начальную контрольную сумму, при этом при несовпадении начальной контрольной суммы с конечной контрольной суммой выдают сообщение об ошибке, что может сопровождаться приостановкой работы процессора или же блокировкой чип-карты с ее изъятием из обращения. 2 с. и 12 з.п. ф-лы, 2 ил.

Реферат

Настоящее изобретение относится к защите данных вычислительного устройства от несанкционированных изменений извне, прежде всего к защите данных, хранящихся в ядре вычислительного устройства, соответственно центрального процессора (ЦП). Изобретение может найти применение, в частности, в чип-картах, поскольку их данные должны быть особенно надежно защищены от несанкционированных изменений извне.

Известно, что области памяти вычислительного устройства защищают от несанкционированных изменений, например, путем кодирования передаваемых по шине данных, кодирования хранящихся в памяти данных и т.п. Из DE 3709524 С2 известна, например, программа для контроля содержимого ячеек программной памяти. В соответствии с этой программой каждый раз в начале или в ходе выполнения программы на основании содержимого ячеек памяти вычисляется контрольная сумма, которая затем сравнивается с предварительно сохраненной в программной памяти контрольной суммой, что позволяет выявлять наличие изменений первоначального содержимого ячеек памяти или же изменений, возникающих лишь в процессе работы устройства, и при наличии таких изменений выдавать сообщение об ошибке.

В основу настоящего изобретения была положения задача разработать более эффективный подход по защите данных вычислительного устройства от несанкционированных изменений извне.

Указанная задача решается согласно изобретению с помощью способа, центрального процессора для осуществления этого способа и вычислительного устройства, соответственно чип-карты, которые оснащены подобным центральным процессором, в соответствии с отличительными признаками независимых пунктов формулы изобретения. Предпочтительные варианты осуществления изобретения представлены в соответствующих зависимых пунктах формулы.

Основная идея изобретения состоит в том, что защита данных, хранящихся в ядре вычислительного устройства, т.е. в его центральном процессоре (ЦП), от несанкционированного изменения извне позволяет повысить степень защиты этого вычислительного устройства, поскольку данные хранятся в ядре вычислительного устройства в незакодированном виде и поэтому легко подвержены несанкционированным изменениям.

Для распознавания подобных несанкционированных изменений после отработки центральным процессором какой-либо команды на основании содержимого нескольких регистров ЦП с помощью математической логической операции, например операции исключающее ИЛИ, определяется контрольная сумма, которая сохраняется в памяти в качестве конечной контрольной суммы. Перед отработкой процессором следующей команды вновь вычисляется контрольная сумма, которая является начальной контрольной суммой. Сравнение начальной и конечной контрольных сумм, которые должны совпадать, позволяет определить, вносились ли в содержимое регистров ЦП после выполнения последней команды несанкционированные изменения. В качестве содержимого регистров рассматривается содержимое тех областей памяти ЦП, которые могут принимать состояние, отличное от состояния логического 0, таких, например, как накапливающий регистр, двоичный накапливающий регистр, указатели данных (DPTR, DPL, DPH), регистры (Р0-Р7) банков регистров, регистр слова состояния программы (PSW), указатель стека (SP), регистр специальных функций (SPR) и т.п. в процессоре типа 8051.

В целях дальнейшего повышения защиты от несанкционированного доступа дополнительно при вводе команды можно запускать счетчик, подсчитывающий количество тактов, необходимое для отработки или выполнения команды. Счетчик при этом предпочтительно выполняют на аппаратном уровне.

Логическая схема, которая на основании кода операции выполняемой команды получает информацию о количестве тактов, необходимых для выполнения команды, преобразует эту информацию в показание счетчика. После этого счетчик работает параллельно с выполняемой командой.

Кроме того, проверяется, укладывается ли выполнение отрабатываемой команды в пределы указанного количества тактов. В том случае, если команда не была выполнена в пределах заданного промежутка времени, то, например, прекращается подача тактовых импульсов, что делает невозможным дальнейшее выполнение команд. В другом варианте может также инициироваться сброс и возврат таким образом центрального процессора в исходное состояние.

Аналогичные меры могут приниматься и при преждевременном завершении выполнения команды, т.е. в случае, если счетчик команд еще не достиг порогового значения в тот момент, когда уже был зарегистрирован код новой операции.

Логическая связь между важными для защиты данных регистров может быть реализована на аппаратном или программном уровне. Так, например, формирование контрольной суммы в промежутке времени между двумя последовательными командами может происходить на основании случайных или некоторых определенных событий либо вычисление такой контрольной суммы может происходить постоянно.

Ниже изобретение более подробно рассмотрено со ссылкой на прилагаемые чертежи, на которых показано:

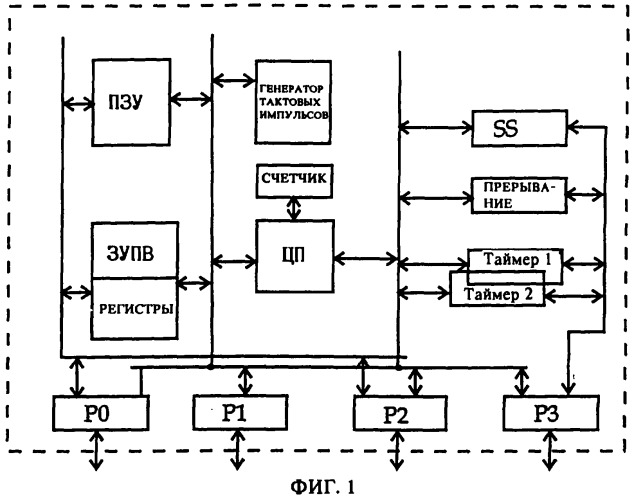

на фиг.1 - структура микроконтроллера на примере процессора 8051 и

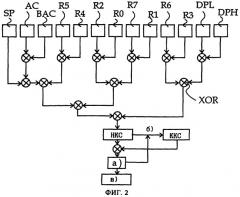

на фиг.2 - логическая схема для логического сопряжения нескольких областей памяти центрального процессора.

На фиг.1 показана структура процессора 8051, представляющего собой 8-разрядный процессор. Поскольку известные методы кодирования предусматривают защиту данных от несанкционированного изменения путем их кодирования при передаче по шине или при хранении в памяти, данные хранятся в ядре вычислительного устройства, т.е. в центральном процессоре, в незакодированном виде. Предлагаемый в изобретении способ позволяет определить наличие несанкционированных изменений в одном или нескольких регистрах ЦП.

На фиг.2 в качестве примера показаны подобные важные для защиты данных области памяти ЦП, данные в которых потенциально могут быть подвергнуты несанкционированным изменениям, а именно указатель стека SP, накапливающий регистр АС, двоичный накапливающий регистр ВАС, регистры R0-R7, указатели данных DPL и DPH соответственно для нижней и верхней областей памяти внутреннего запоминающего устройства с произвольной выборкой (ЗУПВ). Эти регистры логически соединяют друг с другом с целью формирования контрольной суммы. Согласно фиг.2 по два 8-разрядных регистра логически связаны между собой вентилем Исключающее ИЛИ (XOR). Так, в частности, благодаря выполнению логической операции Исключающее ИЛИ над содержимым регистров R0 и R2 образуется новая 8-разрядная кодовая комбинация, которая в свою очередь логически объединяется в вентиле Исключающее ИЛИ с 8-разрядной кодовой комбинацией, которая образуется в результате выполнения логической операции Исключающее ИЛИ над содержимым регистров R1 и R7. В результате выполнения последующих логических операций Исключающее ИЛИ над соответствующими 8-разрядными кодовыми комбинациями в результате получают 8-разрядную кодовую комбинацию, которая служит в качестве контрольной суммы и обозначена на фиг.2 как "начальная контрольная сумма" (НКС). Для формирования контрольной суммы вместо логической операции Исключающее ИЛИ, которая является предпочтительной прежде всего с учетом малого объема вычислений, можно, как очевидно, использовать и другие варианты.

В том случае, когда логические операции выполняются над содержимым регистров на аппаратном уровне с помощью логических элементов, контрольная сумма изменяется непосредственно с изменением содержимого регистра. Иными словами, в процессе выполнения отрабатываемой ЦП команды контрольная сумма при необходимости многократно изменяется. Однако решающее значение для осуществления способа имеет только контрольная сумма, полученная после выполнения какой-либо команды и перед выполнением непосредственно следующей команды, поскольку обе эти контрольные суммы (конечная контрольная сумма (ККС), полученная для определенной команды, и начальная контрольная сумма для непосредственно следующей команды) сравниваются между собой в компараторе.

Указанное сравнение осуществляется следующим образом. Контрольная сумма, получаемая в конце выполнения первой команды, сохраняется в качестве конечной контрольной суммы в памяти ЦП. С целью установить, не произошло ли после выполнения первой команды и перед загрузкой в ЦП следующей, второй команды несанкционированного изменения данных в процессоре, параллельно с вводом этой второй команды формируется, как указано в начале описания, начальная контрольная сумма. При этом на первом шаге а) начальная контрольная сумма сравнивается компаратором с хранящейся в памяти конечной контрольной суммой, полученной для выполненной перед этим первой команды.

Если данные в ЦП не подвергались несанкционированному изменению, то начальная и конечная контрольные суммы будут совпадать, а полученное в результате их сравнения значение будет равно нулю. При этом компаратор выдает сигнал, на основании которого на втором шаге б) после выполнения второй команды имеющаяся на данный момент контрольная сумма сохраняется в памяти в качестве новой конечной контрольной суммы, т.е. выполнение второй команды в этом случае не прерывается. Если же в противном случае значение, полученное при сравнении начальной и конечной контрольных сумм, окажется отличным от нуля, то этот факт будет свидетельствовать о несанкционированном изменении хранящихся в ЦП данных. В этом случае по выходному сигналу компаратора вместо выполнения второго шага б) осуществляется переход к шагу в), на котором выдается сообщение об ошибке, по которому в представленном на фиг.2 случае прекращается обработка команд. При этом, например, может быть приостановлена работа процессора, активизирован датчик защиты или блокировки либо в случае чип-карты она может быть заблокирована в терминале.

Описанный выше механизм защиты может быть реализован и исключительно на программном уровне за счет формирования и сравнения друг с другом контрольных сумм, во-первых, в конце выполнения команды, а во-вторых, в начале выполнения следующей команды. Соответствующая программа может храниться в постоянном запоминающем устройстве (ПЗУ), соответственно в стираемом программируемом ПЗУ (СППЗУ) процессора, а конечную контрольную сумму можно сохранять в ЗУПВ процессора, имеющем побитовую адресацию.

Рассмотренный выше способ не обязательно осуществлять перед выполнением каждой команды. В одном из вариантов предусмотрена возможность осуществления способа в зависимости от наступления какого-либо случайного или некоторого определенного события. Согласно одному из вариантов осуществление способа может начинаться в зависимости от времени.

В другом варианте выполнение предусмотренных предлагаемым способом операций может начинаться при соответствии содержимого одного или нескольких регистров ЦП какой-либо предварительно заданной кодовой комбинации.

В другом варианте осуществление способа может начинаться после выполнения некоторого заданного количества команд.

Осуществление способа предпочтительно начинать лишь при условии, когда между командой, после выполнения которой контрольная сумма была сохранена в памяти в качестве конечной контрольной суммы, и начальной контрольной суммой, полученной в начале выполнения непосредственно следующей команды, проходит определенный, достаточно длительный промежуток времени. Такой подход позволяет снизить нагрузку на вычислительное устройство при выполнении программы, предусматривающей выполнение большого количества команд. Если исходить из того, что несанкционированное изменение данных в ЦП, прежде всего в случае чип-карт, будет происходить не во время выполнения программы, а при изъятой из соответствующего терминала чип-карте, то и в этом случае обеспечивается надежное выявление несанкционированных изменений данных в ЦП.

1. Способ защиты имеющего центральный процессор (ЦП) вычислительного устройства от несанкционированных изменений извне хранящихся в его памяти данных, отличающийся тем, что на основании содержимого регистров ЦП, получаемого в конце выполнения этим процессором какой-либо команды, путем математической логической операции формируют и сохраняют в памяти некоторую конечную контрольную сумму, а на основании содержимого регистров, получаемого перед началом выполнения указанным процессором непосредственно следующей команды, формируют некоторую начальную контрольную сумму, при этом при несовпадении начальной контрольной суммы с конечной контрольной суммой выдают сообщение об ошибке.

2. Способ по п.1, отличающийся тем, что по вводу команды запускают счетчик, подсчитывающий количество тактов, необходимое для выполнения команды, и выдающий сигнал ошибки в том случае, если это количество тактов отличается от заданного количества тактов в большую или меньшую сторону.

3. Способ по п.2, отличающийся тем, что по сигналу ошибки инициируется прерывание или прекращается подача тактовых импульсов.

4. Способ по п.2 или 3, отличающийся тем, что данные о количестве тактов, необходимом для выполнения команды, получают с помощью логической схемы на основании кода операции выполняемой команды.

5. Способ по любому из пп.1-3, отличающийся тем, что математическая логическая операция заключается в выполнении операции Исключающее ИЛИ над содержимым регистров.

6. Способ по любому из пп.1-3, отличающийся тем, что выполнение предусмотренных способом операций начинается при наступлении случайных или некоторых заданных событий.

7. Способ по п.6, отличающийся тем, что выполнение предусмотренных способом операций начинается в зависимости от времени.

8. Способ по п.6, отличающийся тем, что выполнение предусмотренных способом операций начинается в том случае, когда содержимое одного или нескольких регистров ЦП соответствует некоторой предварительно заданной кодовой комбинации.

9. Способ по п.6, отличающийся тем, что выполнение предусмотренных способом операций начинается каждый раз после выполнения заданного количества команд.

10. Центральный процессор (ЦП) вычислительного устройства для осуществления способа по п.1, имеющий схему выполнения логических операций над содержимым нескольких регистров ЦП с помощью логических элементов для формирования контрольной суммы, память для хранения формируемой с помощью логических элементов первой контрольной суммы, компаратор для сравнения сформированной с помощью логических элементов второй контрольной суммы с хранящейся в указанной памяти первой контрольной суммой и устройство управления, предназначенное для управления сохранением первой контрольной суммы в предусмотренной для ее хранения памяти и для управления компаратором.

11. Центральный процессор по п.10, отличающийся тем, что он имеет счетчик, предназначенный для подсчета количества тактов, необходимого для выполнения команд.

12. Центральный процессор по п.10 или 11, отличающийся тем, что он имеет логическую схему для определения на основании кода операции выполняемой команды количества тактов, необходимого для отработки этой команды.

13. Центральный процессор по любому из пп.10-12, отличающийся тем, что он предназначен для применения в вычислительном устройстве.

14. Центральный процессор по любому из пп.10-12, отличающийся тем, что он предназначен для применения в чип-карте.