Полупроводниковое запоминающее устройство

Иллюстрации

Показать всеИзобретение относится к полупроводниковому запоминающему устройству и полупроводниковому элементу памяти. Техническим результатом является защищенность полупроводникового запоминающего устройства от сбоев в работе, связанных с явлениями случайного вероятностного характера. Устройство содержит большое количество элементов памяти, каждый из которых содержит области истока и стока, изолирующую пленку, канальную область, электрод затвора, область для хранения электрических зарядов, устройство также содержит большое количество периферийных схем, содержащих усилитель считывания, регистр для сохранения записанной информации элементов памяти, регистр, который удерживает флажок, показывающий окончание записи при ее проверке, и схему, которая после операции записи сравнивает значение, считанное с ячейки памяти, со значением, зафиксированным флажком в конце записи, и переписывает значение, которое показывает флажок. 5 н. и 30 з.п. ф-лы, 71 ил.

Реферат

Настоящее изобретение относится к полупроводниковому запоминающему устройству и полупроводниковому элементу памяти.

В настоящее время известны энергонезависимые запоминающие устройства, такие как электрически стираемые программируемые постоянные запоминающие устройства (ЭСППЗУ) флэш-типа, в которых используются МОП-транзисторные устройства с плавающими и управляющими затворами. В таких устройствах хранение и считывание информации осуществляется за счет того, что при накоплении носителей заряда на плавающем затворе происходит изменение порогового напряжения МОП-транзистора. Обычно в плавающем затворе используют поликристаллический кремний. Использование МОП-транзисторных устройств с плавающим затвором позволяет с помощью только одного транзистора хранить один бит информации в течение длительных промежутков времени. В качестве примеров ЭСППЗУ флэш-типа можно назвать обычную ячейку памяти и бесконтактную ячейку памяти, которые описаны в Nikkei Electronics, № 444, стр.151-157 (1988).

Технология изготовления подобных устройств описана в работе К. Yano и др., 1993 IEEE International Electron Devices Meeting, Digest of technical papers, стр.541-545 и в работе К.Yano и др., 1996 IEEE International Solid-State Circuits Conference, Digest of technical papers, стр.266-267 и 458, в которых речь идет об одноэлектронных запоминающих устройствах, в которых используется поликристаллический кремний. По этой технологии в тонком слое поликристаллического кремния одновременно формируются канал, который является проводником тока, и область хранения, в которой происходит захват электронов. Хранение информации осуществляется за счет изменения пороговых напряжений при захвате электронов в области захвата заряда. Особенностью такого способа является то, что хранение одного бита информации происходит при захвате одного электрона. Такая технология позволяет изготовить устройства, меньшие по своим размерам, чем устройства, изготовленные при использовании кристаллитов поликристаллического кремния, и при этом изготовленные таким способом устройства могут работать при комнатной температуре.

С целью проверить изменение порогового напряжения в ЭСППЗУ флэш-типа при инжекции и стоке носителя заряда с плавающего затвора (операция записи и операция стирания) осуществляется контроль его состояния после подачи напряжения высокого уровня (или низкого уровня), а затем выполняется проверка, во время которой происходит повторная подача напряжения и регулирование величины пороговых напряжений в тех ячейках памяти, в которых заданное пороговое напряжение не было достигнуто.

Технология такой проверки запоминающего устройства описана в работах Т. Tanaka и др., IEEE J. Solid-State Circuits, т. 29, № 11, стр.1366-1372 (1994), и К. Kimura и др., IEICE Transactions of Electronics, т. Е78-С, № 7, стр.832-837 (1995).

Технология, которую ранее использовали авторы настоящего изобретения, описана в выложенных патентах Японии №№ Hei 7-111295, Hei 8-288469, Hei 9-213822 и Hei 9-213898.

Широкое использование в последние годы методов литографии позволило добиться большого прогресса в создании небольших по площади ячеек памяти, в частности таких, как динамические запоминающие устройства с произвольной выборкой (ДЗУПВ), статические запоминающие устройства с произвольной выборкой (СЗУПВ) и запоминающие устройства типа флэш-памяти. Имеющие небольшую площадь ячейки памяти обладают существенными преимуществами, заключающимися в возможности уменьшения размеров и увеличения выхода готовых микросхем, а также снижения их стоимости за счет увеличения количества микросхем, изготовленных из одной и той же по размерам полупроводниковой пластины. Еще одним преимуществом небольших по площади ячеек памяти является возможность уменьшения длины соединений и обусловленного этим увеличения их быстродействия.

Технологические размеры и габариты ячейки определяются главным образом методом изготовления. Если базовый технологический размер принять равным F, то ДЗУПВ с согнутой разрядной шиной будет иметь размер, равный 8F2, а флэш-память со схемой типа "И" будет иметь размер, равный 6F2. Ячейки памяти с меньшими размерами можно изготовить путем выполнения флэш-памяти на одном транзисторе, при этом полагают, что создание ячеек памяти с меньшими размерами в сравнении с ячейками, изготовленными в виде МОП-транзисторов, выполненных на поверхности подложки, практически невозможно. Для создания ячеек с меньшими габаритами необходимо, как очевидно, использовать объемные конструкции кубической формы. При уменьшении размеров запоминающих устройств за счет придания им кубической формы и при снижении шага между информационными шинами или словарными (или числовыми) шинами до величины, меньшей минимального размера 2F, возникают серьезные и трудноразрешимые проблемы, связанные с расположением информационных шин и словарных шин, с необходимостью соединения ячеек с периферийными схемами и с необходимостью управления матрицами памяти, состоящими из отдельных ячеек, такими периферийными схемами.

С другой стороны, при инжекции и экстракции электронов в микроскопических по размерам частицах металла или полупроводника можно эффективно использовать возникающую в электростатическом поле отталкивающую силу, и при этом теоретически один электронный элемент, контролирующий процесс переноса электронов в отдельных модулях, может работать в очень небольших по размерам структурах порядка 10 нм, потребляя при этом крайне незначительную электрическую мощность. Одноэлектронная память, представляющая собой одноэлектронное запоминающее устройство, способна хранить информацию при накоплении небольшого количества электронов. Одноэлектронная память может хранить один или несколько битов информации в одном элементе, и, поскольку управление хранящимся в памяти электрическим зарядом может быть выполнено в отдельных модулях, такие запоминающие устройства могут работать при толщине порядка одного нанометра. Кроме того, при небольшом количестве сохраненных или накопленных в памяти электронов такие устройства должны обладать существенным преимуществом за счет уменьшения времени перезаписи и увеличения количества возможных перезаписей. Однако реально при изготовлении таких элементов их технологические размеры зависят от ограничений, которые накладываются на ток самим процессом литографии. Кроме того, из-за достаточно большого размера удаляемых участков области стока и истока не удается на базе существующих элементов создать элемент, который благодаря небольшим размерам можно было бы успешно использовать в различных интегральных микросхемах.

Было изготовлено и исследовано работающее при комнатной температуре одноэлектронное запоминающее устройство. Установлено, что для накопления электрического заряда при подаче на одно и то же устройство одного и того же напряжения записи в течение одного и того же времени требуется затратить разное время. Иными словами, было обнаружено, что при подаче одного и того же напряжения записи в течение одного и того же времени в таком устройстве накапливается разное количество электронов. Такое явление можно объяснить случайным вероятностным характером протекающих в устройстве процессов, в частности процесса, связанного с туннельным эффектом, или процесса теплового возбуждения, обусловленных небольшим количеством электронов, участвующих в работе одноэлектронного запоминающего устройства.

Прогресс, достигнутый в создании интегрированных полупроводниковых запоминающих устройств и позволивший повысить плотность расположения в них отдельных ячеек памяти и увеличить емкость устройства, связан с увеличением стоимости оборудования, которое используется для изготовления устройств с высокой степенью интеграции. Плотность устройства памяти можно существенно повысить при многозначной логике сохранения в одной ячейке двух или более битов, не прибегая при этом к еще большей интеграции образующих устройство ячеек памяти. При многозначном хранении данных особую важность приобретает проблема, связанная с возможностью четко различать состояния ячеек памяти, выполняющих операции записи, считывания и стирания накопленной информации.

Использование одноэлектронных запоминающих устройств требует того, чтобы величина заряда была небольшой и чтобы периферийные схемы не создавали большого шума. В полупроводниковых запоминающих устройствах в качестве усилителей считывания часто используют дифференциальные усилители. При этом усилитель считывания обычно располагают относительно информационной шины таким образом, чтобы согласующие информационные шины были выполнены либо открытыми и располагались с обеих сторон усилителя считывания, либо согнутыми в одном и том же направлении. Открытое выполнение согласующих шин обладает определенным преимуществом, поскольку при этом ячейки памяти можно разместить во всех точках пересечения информационных шин и словарных шин, обеспечив тем самым высокую степень интеграции устройства. Однако такая схема обладает и определенным недостатком, связанным с большим уровнем шума, возникающего в словарных шинах. Преимуществом устройств, в которых согласующие шины выполнены согнутыми, является низкий уровень шума, возникающего в словарных шинах, но такие устройства обладают и недостатками, которые связаны с невозможностью расположения ячеек памяти во всех точках пересечения информационных шин и словарных шин и с невозможностью обеспечить в таких устройствах высокую степень интеграции.

К периферийным схемам, под размещение которых требуется большая площадь, помимо усилителя считывания, относятся регистр, который временно сохраняет записанную информацию во время записи, регистр, который удерживает флажок, показывающий окончание записи при ее проверке, и схема, которая после операции записи сравнивает значение, считанное с ячейки памяти, со значением, зафиксированным флажком в конце записи, и переписывает значение, которое показывает флажок.

С учетом всего вышесказанного для расширения пределов, накладывающих определенные ограничения на существующие в настоящее время запоминающие устройства, в настоящем изобретении ставятся следующие задачи: создание одноэлектронной ячейки памяти, наиболее пригодной для разработки запоминающих устройств с высокой степенью интеграции на небольшой по размерам площади, создание полупроводникового запоминающего устройства, защищенного от возможных сбоев в работе, связанных с явлениями случайного вероятностного характера, создание полупроводникового запоминающего устройства, решающего проблему удержания нескольких хранящихся в его памяти значений, создание занимающей небольшую площадь периферийной схемы, не оказывающей отрицательного влияния на характеристики занимающего небольшую площадь устройства памяти и одноэлектронного запоминающего устройства с высокой степенью интеграции, а также создание обладающей низким уровнем шума периферийной схемы, наиболее пригодной для одноэлектронных запоминающих устройств, работающих с небольшими электрическими зарядами и чувствительных к влиянию шума.

В частности, в настоящем изобретении в его основном варианте предлагается полупроводниковое запоминающее устройство, содержащее большое количество элементов памяти, каждый из которых содержит область истока и область стока, расположенные друг над другом, изолирующую пленку, расположенную между областями стока и истока, канальную область, содержащуюся в полупроводнике и соединяющую область истока с областью стока, электрод затвора для создания электрического поля в канальной области, область для хранения электрических зарядов, отделенную от канальной области потенциальным барьером, в котором запоминается указанное большое количество элементов памяти при изменении проводимости указанной канальной области в соответствии с количеством зарядов, при этом полупроводниковое запоминающее устройство содержит также большое количество периферийных схем, предназначенных для передачи сигналов к информационным и словарным шинам и содержащих усилитель считывания, регистр для сохранения записанной информации элементов памяти, регистр, который удерживает флажок, показывающий окончание записи при ее проверке, и схему, которая после операции записи сравнивает значение, считанное с ячейки памяти, со значением, зафиксированным флажком в конце записи, и переписывает значение, которое показывает флажок, причем по меньшей мере часть этих периферийных схем представляет собой элементы КМОП, состоящие из n-канальных МОП-транзисторов и р-канальных МОП-транзисторов.

В изобретении предлагается еще один вариант полупроводникового запоминающего устройства, имеющего многослойную структуру и содержащего первую локальную информационную шину, первый промежуточный слой над первой локальной информационной шиной, шину истока над первым промежуточным слоем, второй промежуточный слой над шиной истока, вторую локальную информационную шину над вторым промежуточным слоем, причем эти первый и второй промежуточные слои являются изолирующими пленками, первую канальную область, соединенную с шиной истока и первой локальной информационной шиной и расположенную на боковой стороне многослойной структуры, и вторую канальную область, соединенную со второй шиной истока и второй локальной информационной шиной и расположенную на боковой поверхности многослойной структуры над первой канальной областью, область захвата электрического заряда, окруженную потенциальным барьером и расположенную в непосредственной близости от первой и второй канальных областей или внутри канальной области, расположенной на боковой стороне многослойной структуры, и словарную шину, соединенную с канальной областью через изолирующую пленку затвора, и два полупроводниковых элемента памяти, расположенных над точками пересечения и под точками пересечения первой и второй локальных информационных шин и словарной шины, в которых хранение информации осуществляется изменением порогового напряжения полупроводника за счет контролируемого изменения количества носителей в области захвата электрического заряда, при этом полупроводниковые элементы памяти объединены последовательно в матрицу большим количеством локальных информационных шин и словарных шин, а первая и вторая локальные информационные шины соединены с одной и той же общей информационной шиной через транзисторы выборки.

При этом транзисторы выборки имеют управляемые индивидуально электроды затвора.

Предпочтительно выполнение устройства, при котором общая информационная шина перекрывает первую и вторую локальные информационные шины.

Причем контактное отверстие, соединяющее общую информационную шину с транзистором выборки, предпочтительно расположить между контактными отверстиями, соединяющими первую и вторую локальные информационные шины с транзистором выборки.

В одном из предпочтительных вариантов выполнения полупроводникового запоминающего устройства первая и вторая локальные информационные шины, соединенные с одной и той же общей информационной шиной через отдельные МОП-транзисторы выборки, имеют отдельную структуру диффузионного слоя для транзистора выборки, а контактное отверстие для общей информационной шины и этого отдельного участка диффузионного слоя проходит по крайней мере через одну локальную информационную шину.

Полупроводниковое запоминающее устройство в соответствии с изобретением может иметь вспомогательную информационную шину, выполненную из такого же материала, что и основная локальная информационная шина, расположенную параллельно ей и имеющую по существу равную с ней ширину, причем вспомогательная шина не используется для хранения информации.

Предложенное полупроводниковое запоминающее устройство может иметь изолирующую пленку, выполненную на внутренней стенке контактного отверстия шины истока или локальной информационной шины, при этом полупроводниковый материал, нанесенный на боковую поверхность изолирующей пленки, отделяющей шину истока от локальной информационной шины, имеет окисленную изолирующую пленку.

В одном из предпочтительных вариантов выполнения полупроводниковое запоминающее устройство имеет полупроводниковый элемент, выполненный на поверхности полупроводниковой подложки, и в этом устройстве контактное отверстие перекрывает электрод затвора или диффузионный слой полупроводникового элемента, выполненного на полупроводниковой подложке, и по крайней мере шину истока или локальную информационную шину.

Кроме того, в этом устройстве целесообразно предусмотреть вспомогательную структуру, которая не используется в качестве локальной информационной шины, но изготовлена из того же материала, что и локальная информационная шина, и структуру, в которой контактное отверстие для словарной шины расположено на этой вспомогательной структуре.

В этом устройстве может быть также вспомогательная структура, которая не используется в качестве локальной информационной шины, но изготовлена из того же материала, что и локальная информационная шина, и полупроводниковая пленка, перекрывающая на 1 мкм или больше в продольном направлении боковую сторону изолирующей пленки вспомогательной структуры.

Целесообразно в предложенном полупроводниковом запоминающем устройстве шину от источника питания, по которой напряжение подается в схему считывания информации из полупроводникового элемента памяти, расположить параллельно словарной шине.

Целесообразно в предложенном устройстве в качестве общей информационной шины использовать второй слой снизу или верхний слой изготовленных из металла межсоединений.

В еще одном предпочтительном варианте выполнения предложенное полупроводниковое запоминающее устройство имеет схему считывания информации из полупроводникового элемента памяти, которая соединена с общей информационной шиной через слой изготовленных из металла межсоединений, расположенный ниже общей информационной шины.

Предпочтительно в предложенном устройстве локальную информационную шину соединить с общей информационной шиной МОП-транзистором.

В данном устройстве первая и вторая локальные информационные шины могут быть соединены с одной и той же общей информационной шиной отдельными МОП-транзисторами выборки, которые имеют разные электроды затвора, при этом на вход первой и второй локальных информационных шин через соответствующие электроды затворов подаются взаимоинверсные сигналы.

В еще одном из предпочтительных вариантов выполнения полупроводниковое запоминающее устройство имеет устройство управления, предназначенное для выполнения первой операции стирания информации, хранящейся в полупроводниковом элементе памяти, второй операции повторного стирания информации, оставшейся в этом полупроводниковом элементе памяти при неполном стирании информации во время первой операции стирания, третьей операции записи информации "0" или "1" в этот полупроводниковый элемент памяти, четвертой операции повторной записи информации в этот полупроводниковый элемент памяти при неполной записи информации во время третьей операции и пятой операции считывания информации, хранящейся в полупроводниковом элементе памяти, а также имеет регистр для хранения информации "0" или "1" во внешней части полупроводникового устройства, и устройство для хранения перечня полупроводниковых элементов памяти, в которых стирание информации было выполнено полностью, или перечня полупроводниковых элементов памяти, в которых стирание информации после первой операции стирания было выполнено не полностью, и устройство для хранения информации, записанной в полупроводниковом элементе памяти во время третьей операции записи, и устройство для хранения перечня полупроводниковых элементов памяти, в которых стирание информации было выполнено полностью, или перечня полупроводниковых элементов памяти, в которых после третьей операции стирание информации было выполнено не полностью, и устройство, использующее этот регистр для хранения информации, считанной с полупроводникового элемента памяти во время пятой операции считывания.

При этом упомянутое выше полупроводниковое запоминающее устройство выполняет первую операцию записи в полупроводниковый элемент информации "0" или "1", вторую операцию повторной записи информации в полупроводниковый элемент при неполной записи информации во время первой операции записи и имеет регистр для хранения перечня полупроводниковых элементов памяти, в которые информация была записана полностью, или перечня полупроводниковых элементов памяти, в которые информация была записана не полностью после первой операции записи, и имеет устройство для повторной записи значений регистра в полупроводниковые элементы памяти, в которые информация была записана полностью.

В предпочтительном варианте выполнения устройство для перезаписи значений регистра, выполняемой в том случае, когда информация, свидетельствующая о полной записи информации, представляет собой напряжение высокого уровня, состоит из одного р-канального МОП-транзистора и одного n-канального МОП-транзистора и в котором исток n-канального МОП-транзистора соединен с источником напряжения высокого уровня, сток р-канального МОП-транзистора соединен со стоком n-канального МОП-транзистора, информация, свидетельствующая о полной записи информации, подается на вход затвора n-канального МОП-транзистора, сток n-канального МОП-транзистора соединен с входом регистра, хранящего информацию, свидетельствующую о том, что запись информации была выполнена полностью, а сигнал управления подается на вход затвора р-канального МОП-транзистора.

В предпочтительном варианте выполнения устройство для перезаписи значений регистра, выполняемой в том случае, когда информация, свидетельствующая о полной записи информации, представляет собой напряжение низкого уровня, состоит из одного n-канального МОП-транзистора и одного р-канального МОП-транзистора и в котором исток р-канального МОП-транзистора соединен с источником напряжения низкого уровня, сток n-канального МОП-транзистора соединен со стоком р-канального МОП-транзистора, информация, свидетельствующая о полной записи информации, подается на вход затвора р-канального МОП-транзистора, сток р-канального МОП-транзистора соединен со входом регистра, хранящего информацию, свидетельствующую о том, что запись информации была выполнена полностью, а сигнал управления подается на вход затвора n-канального МОП-транзистора.

В соответствии с изобретением предлагается еще один предпочтительный вариант выполнения полупроводникового запоминающего устройства, которое выполнено на подложке и состоит из большого количества ячеек памяти для хранения информации путем накапливания или разрядки электрических зарядов и в котором группа из двух ячеек памяти расположена вертикально на подложке, причем эти ячейки памяти соответствующим образом соединены с информационными шинами и словарными шинами, и в котором при выборе по крайней мере одной из всех ячеек памяти адресный сигнал поступает на вход преддешифратора адреса и дешифратора локальной информационной шины, причем по сигналу от преддешифратора адреса выбирается одна словарная шина, по сигналу от дешифратора локальной информационной шины выбирается информационная шина, а при выборке пригодной для использования информации информационные шины для группы из двух вертикально расположенных ячеек памяти в случаях стирания выбираются одновременно, а в случаях считывания выбираются раздельно.

В соответствии с изобретением предлагается еще один вариант предпочтительного выполнения полупроводникового запоминающего устройства, содержащего большое количество элементов памяти, каждый из которых содержит область истока и область стока, канальную область, содержащуюся в полупроводнике и соединяющую область истока с областью стока, область для хранения электрических зарядов, отделенную от канальной области потенциальным барьером, в которой запоминается указанное большое количество элементов памяти при изменении проводимости указанной канальной области в соответствии с количеством зарядов, при этом полупроводниковое запоминающее устройство содержит также большое количество локальных информационных шин и общую информационную шину, а большое количество элементов памяти включает в себя расположенные друг над другом элементы памяти, указанные локальные информационные шины включают в себя расположенные друг над другом и разделенные изолирующей пленкой локальные информационные шины, причем область стока или истока элемента памяти, расположенного в верхнем слое элементов памяти, соединена с локальной информационной шиной, расположенной в указанном верхнем слое, а область стока или истока элемента памяти, расположенного в нижнем слое элементов памяти, соединена с локальной информационной шиной указанного нижнего слоя, указанные локальные информационные шины указанных слоев соединены с общей информационной шиной через МОП-транзисторы выборки, имеющие разные по длине электроды затвора.

В соответствии с изобретением предлагается также еще один вариант предпочтительного выполнения полупроводникового запоминающего устройства, содержащего блоки ячеек памяти, каждый из которых состоит из большого количества ячеек памяти, расположенных в точках пересечения пересекающихся словарных шин и информационных шин, и периферийных схем, подающих сигналы к словарным и информационным шинам, причем ячейка памяти состоит из подложки, первой многослойной области, расположенной на подложке, второй многослойной области, расположенной над первой областью, изолирующей пленки, расположенной между первой и второй областями, канальной области, соединяющей друг с другом первую и вторую области, электрода затвора, который создает электрическое поле в канальной области, и области захвата электрического заряда, причем периферийные схемы включают в себя усилитель считывания, регистр для сохранения записанной информации элементов памяти, регистр, который удерживает флажок, показывающий окончание записи при ее проверке, и схему, которая после операции записи сравнивает значение, считанное с ячейки памяти, со значением, зафиксированным флажком в конце записи, и переписывает значение, которое показывает флажок, при этом хранение заряда осуществляется изменением порогового напряжения полупроводника при контролируемом изменении количества носителей заряда в области захвата электрического заряда, при этом по меньшей мере часть периферийных схем представляют собой комплементарную МОП-структуру, состоящую из n-канальных МОП-транзисторов и р-канальных МОП-транзисторов.

Область захвата электрического заряда образована предпочтительно мелкими частицами из металла или полупроводникового материала со средним размером до 10 нм.

Канальная область в предпочтительном виде выполнения полупроводникового элемента памяти представляет собой тонкий слой полупроводника, средняя толщина которого не превышает 10 нм.

В соответствии с изобретением канальная область в полупроводниковом запоминающем устройстве выполняет функцию области захвата электрического заряда.

Целесообразно по крайней мере первую или вторую области сформировать в подложке полупроводникового запоминающего устройства.

При этом первая область или область стока предпочтительно выполнить из поликристаллического кремния.

Целесообразно, чтобы минимальное значение эффективной ширины канальной области в полупроводниковом элементе памяти не превышало 20 нм.

Предпочтительно в полупроводниковом элементе памяти блок, состоящий из большого количества ячеек памяти, выполнить в виде многослойной структуры из двух или более слоев.

Предпочтительно в предложенном полупроводниковом запоминающем устройстве две ячейки памяти первой области, расположенные одна над другой, соединить с одной и той же информационной шиной через соответствующий транзистор выборки.

Полупроводниковое запоминающее устройство целесообразно оснастить схемой управления, выполняющей три операции, включая первую операцию, заключающуюся в подаче напряжения записи к ячейке памяти, вторую операцию, заключающуюся в считывании информации, сохраненной в ячейке памяти после выполнения первой операции, и третью операцию, заключающуюся в повторной подаче к ячейке памяти напряжения записи в том случае, если при выполнении второй операции будет установлено, что информация в ячейку памяти была записана не в полном объеме.

Предложенное в изобретении полупроводниковое запоминающее устройство может иметь схему хранения информации, которая хранит записанную в ячейке памяти информацию (или перечень элементов для записи информации "0" или информации "1") во внешней части ячейки памяти, при этом операция записи выполняется вторично, если будет установлено, что информация, которая хранится в схеме хранения, после приложения напряжения записи не соответствует состоянию информации полупроводникового элемента памяти.

В соответствии с изобретением полупроводниковое запоминающее устройство за счет подачи на ячейку памяти разных по величине напряжений записи имеет возможность в этой ячейке хранить два или более битов информации.

Другие элементы, преимущества и отличительные особенности предлагаемого изобретения более подробно рассмотрены ниже в описании различных вариантов его выполнения.

Ниже изобретение поясняется со ссылкой на чертежи, на которых показано:

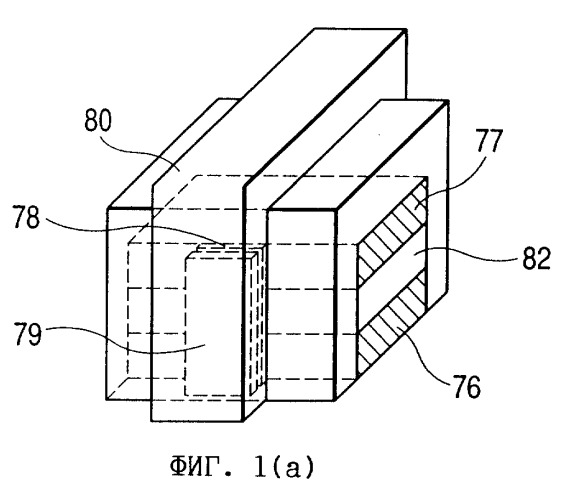

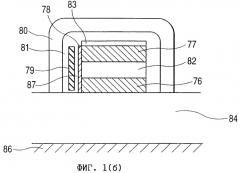

на фиг.1 (а) и 1 (б) - полупроводниковый элемент согласно первому варианту выполнения, при этом на фиг.1(а) показан вид в изометрии, а на фиг.1 (б) показано поперечное сечение,

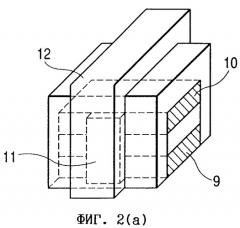

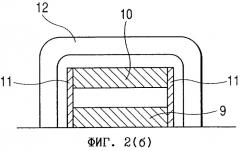

на фиг.2 (а) и 2 (б) - полупроводниковый элемент согласно третьему варианту выполнения, при этом на фиг.2 (а) показан вид в изометрии, а на фиг.2 (б) показано поперечное сечение,

на фиг.3(а) и 3 (б) - полупроводниковый элемент согласно четвертому варианту выполнения, при этом на фиг.3 (а) показан вид в изометрии, а на фиг.3 (б) показано поперечное сечение,

на фиг.4 (а), 4 (б) и 4 (в) - полупроводниковый элемент согласно пятому варианту выполнения, при этом на фиг.4 (а) показан вид в изометрии, на фиг.4 (б) показано поперечное сечение, включая поперечное сечение каналов, а на фиг.4 (в) показано поперечное сечение, включая поперечное сечение истока,

на фиг.5 (а) и 5 (б) - полупроводниковый элемент согласно шестому варианту выполнения, при этом на фиг.5 (а) показан вид в изометрии в процессе формирования канала, а на фиг.5 (б) показан вид в изометрии после формирования затворов,

на фиг.6 - полупроводниковый элемент согласно седьмому варианту выполнения,

на фиг.7 (а) и 7(б) - полупроводниковый элемент согласно восьмому варианту выполнения, при этом на фиг.7 (а) показан вид в изометрии в процессе формирования канала, а на фиг.7(б) показан вид в изометрии после формирования затворов,

на фиг.8 (а) - вид в изометрии полупроводникового устройства согласно девятому варианту выполнения, а на фиг.8 (б) показан вид сверху,

на фиг.9 (а) и 9 (б) - полупроводниковый элемент согласно десятому варианту выполнения, при этом на фиг.9 (а) показан вид в изометрии, а на фиг.9 (б) показан вид сверху,

на фиг.10 (а) и 10 (б) - виды сверху, на которых показан процесс изготовления полупроводникового устройства согласно одиннадцатому варианту выполнения,

на фиг.11 (а) и 11 (б) - виды сверху, на которых показан процесс изготовления полупроводникового устройства согласно одиннадцатому варианту выполнения,

на фиг.12(а) и 12 (б) - виды сверху, на которых показано полупроводниковое устройство согласно одиннадцатому варианту выполнения и процесс его изготовления,

на фиг.13 (а) и 13 (б) - полупроводниковый элемент согласно двенадцатому варианту выполнения,

на фиг.14 - полупроводниковый элемент согласно тринадцатому варианту выполнения,

на фиг.15 (а) и 15 (б) - полупроводниковый элемент согласно второму варианту выполнения, при этом на фиг.15 (а) показан вид в изометрии, а на фиг.15 (б) показано поперечное сечение,

на фиг.16 (а) и 16 (б) - изображение в изометрии полупроводникового устройства согласно первому варианту выполнения в процессе его изготовления,

на фиг.17 - поперечное сечение, на котором показана контактная часть полупроводникового устройства согласно одиннадцатому варианту выполнения,

на фиг.18 (а) и 18 (б) - полупроводниковый запоминающий элемент, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения, при этом на фиг.18 (а) показан вид после формирования канала, а на фиг.18 (б) показан вид в изометрии после формирования словарных шин,

на фиг.19 - вид сверху полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения,

на фиг.20 - чертеж, иллюстрирующий принцип работы полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового устройства согласно четырнадцатому варианту выполнения,

на фиг.21 - вид сверху плоского полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения, в состоянии до формирования запоминающего элемента,

на фиг.22 - вид сверху плоского полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения, после формирования информационных шин,

на фиг.23 - вид сверху плоского полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения, после нанесения сетки резиста для формирования каналов,

на фиг.24 - вид сверху плоского полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения, после формирования словарных шин,

на фиг.25 - вид сверху плоского полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения, после формирования контактных отверстий,

на фиг.26 - вид сверху плоского полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения, после формирования первого слоя соединительных проводников,

на фиг.27 - вид сверху плоского полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения, после формирования второго слоя соединительных проводников,

на фиг.28 - вид сверху плоского полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения, после формирования контактных отверстий, при этом, в частности, показана сеть контактов словарных шин, расположенных в конце матрицы запоминающих элементов,

на фиг.29 - поперечное сечение контактной структуры МОП-транзистора выборки плоского полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно четырнадцатому варианту выполнения,

на фиг.30 (а) и 30 (б) - изображение полупроводникового запоминающего элемента, который является конструктивным элементом полупроводникового запоминающего устройства согласно пятнадцатому варианту выполнения, при этом на фиг.30 (а) показан вид сверху после формирования каналов, а на фиг.30 (б) показан вид сверху после формирования словарных шин,

на фиг.31 (а) и 31 (б) - изображение другого по форме варианта плоского полупроводникового запоминающего элемента, который является конструктивным элементом полупроводник