Делитель на нейронах

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано для синтеза арифметико-логических устройств, для создания быстродействующих и высокопроизводительных цифровых систем, выполняющих операцию деления чисел в прямых кодах. Техническим результатом является снижение аппаратных средства повышение надежности работы цифрового делителя, упрощение алгоритма работы блока управления устройства. Для этого устройство содержит блок регистра делителя, блок ввода данных, блок регистра делимого, блок суммы и формирования разрядов частного, блок анализа переполнения разрядной сетки, блок регистра остатка, блок регистра частного, блок управления. 13 ил.

Реферат

Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для синтеза арифметико-логических устройств, для создания быстродействующих и высокопроизводительных цифровых устройств деления чисел в прямых кодах.

Известно "Устройство для деления" (патент №4380519/24, от 12.08.88 г. Бюл. №48 1987), позволяющее выполнять операцию деления чисел в двоичной системе счисления.

Известно также "Устройство для деления" (патент №346605/18, от 07.07.82 г. Бюл. №39 1983 г.), позволяющее делить двоичные числа.

В качестве прототипа выбрано "Устройство для деления чисел" (3888716/24, от 19.04.1985. Бюл №11, 1990 г.), которое выполняет операцию деления.

Задача заключалась в следующем:

1) уменьшить аппаратные затраты устройства,

2) упростить алгоритм блока управления,

3) повысить скорость операции деления чисел в прямых кодах,

4) повысить надежность работы делителя.

В представленном делителе происходит деление двоичных чисел. Предлагаемый делитель позволит значительно снизить аппаратные средства, что ведет к упрощению комбинационной схемы, а также значительно упростит алгоритм работы устройства.

Решение задачи осуществляется тем, что делитель на нейронах, содержащий блок регистра делителя, отличающийся тем, что дополнительно введены: блок ввода данных, блок регистра делимого, блок суммы и формирования разрядов частного, блок анализа переполнения разрядной сетки, блок регистра остатка, блок регистра частного, блок управления, причем первый управляющий выход блока управления соединен с управляющим входом блока ввода данных, информационный выход которого соединен с информационным входом блока управления, и с информационным входом блока регистра делителя, и с информационным входом блока регистра делимого, с первого по третий управляющие входы которого соединены соответственно со вторым по четвертый управляющими выходами блока управления, с пятого по седьмой управляющие выходы которого соединены соответственно с первым по третий управляющими входами блока регистра делителя, информационный выход которого соединен с третьим информационным входом блока суммы и формирования разрядов частного, первый информационный вход которого соединен с информационным выходом блока регистра делимого, информационный выход блока регистра остатка соединен со вторым информационным входом блока суммы и формирования разрядов частного, информационный выход которого соединен с информационным входом блока регистра остатка, с первого по третий управляющие входы которого соединены соответственно с одиннадцатым по тринадцатый управляющими выходами блока управления, с восьмого по десятый управляющие выходы которого соединены соответственно со вторым по четвертый управляющими входами блока регистра частного, управляющий выход которого соединен с первым управляющим входом блока управления, четырнадцатый и пятнадцатый управляющие выходы которого соединены соответственно со вторым и третьим управляющими входами блока анализа переполнения разрядной сетки, второй управляющий выход которого соединен со вторым управляющим входом блока управления, управляющий выход блока ввода данных соединен с первым управляющим входом блока регистра частного, пятый управляющий вход которого соединен с первым управляющим выходом блока анализа переполнения разрядной сетки, первый управляющий вход которого соединен с управляющим выходом блока суммы и формирования разрядов частного, третий и четвертый управляющие входы блока управления "ПУСК" и "СБРОС" являются внешними входами устройства.

БВД - блок ввода данных служит для ввода операндов со своими знаками.

БРДМ - блок регистра делимого служит для хранения введенного делимого.

БРОСТ - блок регистра остатка служит для хранения и преобразования двоичного кода остатка.

БСФРЧ - блок суммы и формирования разряда частного служит для выполнения операций сложения или вычитания над делимым или остатком и делителем и формирования разрядов частного на основании результата этих операций.

БРДТ - блок регистра делителя служит для хранения введенного делителя.

БАПРС - блок анализа переполнения разрядной сетки служит для анализа разрядности.

БРЧС - блок регистра частного служит для хранения полученного частного.

БУ - блок управления служит для управления устройством.

Операция деления в ЭВМ может выполняться по двум алгоритмам: без восстановления остатка и с восстановлением остатка. Деление в ЭВМ проще всего выполнять по алгоритму без восстановления остатка в прямом коде. Знак частного при делении в прямом коде определяется как сумма по модулю 2 знаковых цифр делимого и делителя и присваивается частному в конце операции деления. Частное определяется путем деления модулей исходных чисел. Чтобы определить следующую цифру частного, необходимо сдвинуть текущий остаток влево на один разряд, а затем алгебраически прибавить к нему модуль делителя, которому приписывается знак, противоположный знаку текущего остатка. Знак полученного таким образом следующего остатка и определяет следующую цифру частного: если остаток положительный, то в частном записывается 1, если отрицательный - записывается 0. Операция сдвигов и алгебраических сложений повторяется до тех пор, пока в частном не получится требуемое количество цифр.

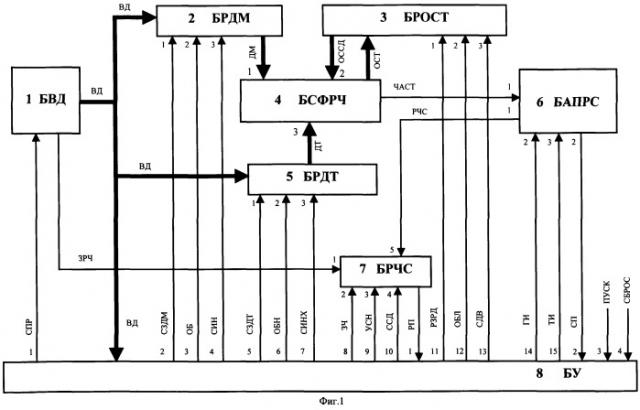

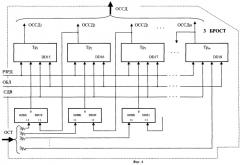

На фиг.1 изображена структурная схема делителя на нейронах.

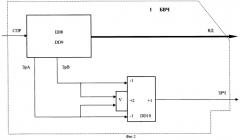

На фиг.2 представлен вариант технической реализации блока ввода данных.

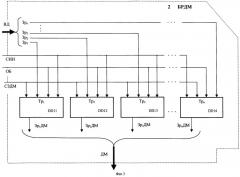

На фиг.3 показана функциональная схема блока регистра делимого.

На фиг.4 показана функциональная схема блока регистра остатка.

На фиг.5 показана принципиальная схема логических элементов дизъюнкции блока суммы и формирования разрядов частного.

На фиг.6 показана функциональная схема сумматоров-вычитателей блока суммы и формирования разрядов частного.

На фиг.7 представлен вариант технической реализации первого одноразрядного сумматора-вычитателя блока суммы и формирования разрядов частного.

На фиг.8 показана функциональная схема блока регистра делителя.

На фиг.9 представлен вариант технической реализации блока анализа переполнения разрядной сетки.

На фиг.10 показана функциональная схема блока регистра частного.

На фиг.11 представлен вариант технической реализации i-ого одноразрядного сумматора-вычитателя блока суммы и формирования разрядов частного.

На фиг.12 - содержательная граф-схема алгоритма работы устройства.

На фиг.13 - размеченная граф-схема алгоритма работы устройства.

Делитель на нейронах (фиг.1) содержит: блок 1 ввода данных, блок 2 регистра делимого, блок 5 регистра делителя, блок 3 регистра остатка, блок 7 регистра частного, блок 4 суммы и формирования разрядов частного, блок 6 анализа переполнения разрядной сетки, блок 8 управления, пороговые элементы, нейроны.

Для описания алгоритма работы блока 8 управления используются следующие идентификаторы.

1. СПР - сигнал пуска работы

2. СЗДМ - сигнал разрешения записи делимого в регистр делимого

3. ОБ - сигнал обнуления регистра блока регистра делимого

4. СИН - сигнал синхронизации регистра блока регистра делимого

5. СЗДТ - сигнал разрешения записи делителя в регистры блока делителя

6. ОБН - обнуление регистра блока регистра делителя

7. СИНХ - сигнал синхронизации регистра блока регистра делителя

8. РЗРД - разрешение записи остатка в регистры блока регистра остатка

9. ОБЛ - обнуление регистра блока регистра остатка

10. СДВ - сигнал сдвига информации на один разряд влево регистра остатка блока регистра остатка

11. ДМ - двоичная информация делимого

12. ДТ - двоичный код делителя

13. ВД - двоичная информация входных данных, поступающая с выхода блока ввода данных

14. ЧАСТ - знаковый разряд остатка

15. ГИ - генератор прямоугольных импульсов

16. ТИ - генератор тактовых импульсов

17. СП - сигнал признака переполнения разрядной сетки

18. РЧС - разряд частного

19. ЗЧ - сигнал разрешения записи разряда частного в блок регистра частного

20. РП - признак регистра "полон" блока регистра частного

21. ССД - сигнал сдвига влево информации на один разряд в регистре частного блока регистра частного

22. ЗРЧ - знаковый разряд частного

23. УСН - сигнал установки в нулевое состояние регистра частного блока регистра частного

24. ОСТ - двоичный сигнал остатка частного

25. ОССД - двоичная информация сдвинутого остатка

26. ЗрА - двоичный код знакового разряда первого числа

27. ЗрВ - двоичный код знакового разряда первого числа

28. ЗрnДМ - двоичные разряды делимого, поступающие с выходов триггеров регистра блока регистра делимого

29. Зрn - двоичная информация делимого, поступающая на входы триггеров регистра блока регистра делимого

30. ОССДm - двоичные разряды остатка, поступающие с выходов триггеров регистра блока регистра остатка

31. Зpm - двоичная информация остатка, поступающая на входы логических схем ИЛИ блока регистра остатка

32. ЗрmОССДm - двоичные разряды остатка, поступающие на входы логических схем ИЛИ принципиальной схемы дизъюнкторов

33. OCДMk - информационный сигнал, равный результату операции дизъюнкции информационных двоичных разрядов делимого и остатка

34. ЗрzДТ - двоичные разряды делителя

35. Pk - двоичный разряд переноса в старший разряд при выполнении операции суммирования

36. Zk - двоичный разряд заема в младший разряд при выполнении операции вычитания

37. PEЗk - результат суммы или разности

38. ЗрiОСДМ - двоичный разряд преобразованного остатка

39. Зpz - двоичный разряд второго числа

40. ЗРЧС - двоичный код триггера знакового разряда частного

41. ПУСК - сигнал пуска работы делителя

42. СБРОС - сигнал установки элементов памяти делителя в нулевое состояние

Работа алгоритма управления устройства

По сигналу ПУСК (блок 2 граф-схемы алгоритма) происходит запуск работы устройства по команде БВД:=СПР (блок 3).

В блоке 4 алгоритма по командам БРДМ:=ОБ, БРДТ:=ОБН, БРОСТ:=ОБ и БРЧС:=УСТН производится обнуление всех элементов памяти блоков: делимого, делителя, остатка и частного.

В блоке 5 алгоритма по командам БРДМ:=СЗДМ, БРДТ:=СЗДТ, БРОСТ:=РЗДР и БРЧС:=ЗЧ осуществляется разрешение записи из блока управления на все элементы памяти блоков: делимого, делителя, остатка и частного. Блоки регистров делимого и делителя готовы к записи делимого и делителя соответственно, а блоки регистров остатка и частного готовы к хранению результатов.

В блоке 6 алгоритма с помощью шифратора (клавиатуры) ШФ осуществляется загрузка в блоки регистров делимого и делителя чисел (делимого и делителя) со своими знаками. Загруженные числа поступают на вход блока суммы и формирования разрядов частного по командам БСФРЧ:=ДМ и БСФРЧ:=ДТ.

В блоке 7 алгоритма по команде БРЧС:=ЗРЧ производится запись в блок регистра частного знакового разряда частного. Знак частного определяется в блоке ввода данных с помощью операции “сумма по модулю 2” над знаковыми разрядами делимого и делителя. Если знаковые разряды одинаковые, то в знаковый разряд частного записывается “0”, в обратном случае - “1”.

В блоке 8 алгоритма производится запись результата вычитания делителя из делимого в блок регистра остатка по команде БРОСТ:=ОСТ. Далее операции по учету разряда остатка и сдвига будут проводиться с остатком, поэтому блок регистра делимого больше не используется.

В блоках 9-18 алгоритма производится вычисление целой части частного.

В блоке 9 происходит запуск генератора прямоугольных импульсов по команде БАПРС:=ГИ. Значение счетчика блока устанавливается в значение (n-k+1) (HЗ1), где n - разрядность делимого, k - разрядность делителя. Таким образом, через (n-k+1) число импульсов будет получена целая часть частного. Это значение вычисляется в блоке управления.

В блоке 10 алгоритма проверяется условие ГИ>НЗ1, т.е. установлен ли счетчик блока в значение HЗ1 - первое начальное значение.

В блоке 11 алгоритма по команде БАПРС:=ЧАСТ происходит передача блоку анализа переполнения разрядной сетки знакового разряда остатка. При этом происходит уменьшение счетчика на единицу и происходит анализ переполнения разрядной сетки блока регистра частного. В случае переполнения вырабатывается сигнал переполнения СП.

В блоке 12 алгоритма происходит анализ сигнала переполнения СП. Если сигнал равен “1”, то происходит остановка работы делителя, в обратном случае делитель продолжает работу.

В блоке 13 алгоритма по команде БРЧС:=РЧС происходит запись в блок регистра частного очередного разряда. Разряд определяется в блоке суммы и формирования разрядов частного. Если результат суммирования или вычитания положительный (С>0), то разряду частного присваивается “1”, иначе - “0”, где С - знаковый разряд остатка.

В блоке 14 алгоритма происходит анализ разряда частного РЧС. В зависимости от значения разряда производится следующая операция сложения или вычитания над остатком и делителем.

Если РЧС=0, то осуществляется переход на блок 15 алгоритма.

В блоке 15 алгоритма осуществляется сдвиг значения блока регистра остатка на один разряд влево по команде БРОСТ:=СДВ.

В блоке 16 алгоритма по командам БСФРЧ:=ОССД и БСФРЧ:=ДТ производится загрузка в блок суммы и формирования разрядов частного значений из блоков регистра остатка и делителя и осуществляется их суммирование.

Если РЧС=1, то осуществляется переход на блок 17 алгоритма.

В блоке 17 алгоритма осуществляется сдвиг значения блока регистра остатка на один разряд влево по команде БРОСТ:=СДВ.

В блоке 18 алгоритма по командам БСФРЧ:=ОССД и БСФРЧ:=ДТ производится загрузка в блок суммы и формирования разрядов частного значений из блоков регистра остатка и делителя и осуществляется вычитание делителя из остатка.

По выходу из блоков 16 и 18 осуществляется переход на вход блока 10 алгоритма.

По единичному выходу блока 10 алгоритма, в случае невыполнения условия ГИ>НЗ1, происходит переход на блок 19 алгоритма.

В блоках 19-28 алгоритма производится вычисление дробной части частного.

В блоке 19 происходит запуск генератора прямоугольных импульсов по команде БАПРС:=ГИ. Значение счетчика блока устанавливается в значение, равное требуемой точности вычисления дробной части частного - НЗ2. Таким образом, через НЗ2 - количество импульсов будет получена дробная часть частного.

В блоке 20 алгоритма проверяется условие ГИ>НЗ2, которое соответствует количеству разрядов дробной части частного.

В блоке 21 алгоритма по команде БАПРС:=ЧАСТ происходит передача блоку анализа переполнения разрядной сетки знакового разряда остатка. При этом происходит уменьшение счетчика на единицу и происходит анализ переполнения разрядной сетки блока регистра частного. В случае переполнения вырабатывается сигнал переполнения СП.

В блоке 22 алгоритма происходит анализ сигнала переполнения СП. Если сигнал равен “1”, то происходит остановка работы делителя, иначе делитель продолжает работу.

В блоке 23 алгоритма по команде БРЧС:=РЧС происходит запись в блок регистра частного очередного разряда. Разряд частного определяется в блоке анализа переполнения разрядной сетки. Если результат суммирования или вычитания в блоке суммы и формирования разрядов частного положительный (С>0), то разряду частного присваивается “1”, иначе - “0”, где С - знаковый разряд остатка.

В блоке 24 алгоритма происходит анализ разряда частного РЧС. В зависимости от значения разряда производится следующая операция сложения или вычитания между сдвинутым остатком и делителем.

Если РЧС=0, то осуществляется переход на блок 25 алгоритма.

В блоке 25 алгоритма осуществляется сдвиг значения блока регистра остатка на один разряд влево по команде БРОСТ:=СДВ.

В пункте 26 алгоритма по командам БСФРЧ:=ОССД и БСФРЧ:=ДТ производится загрузка в блок суммы и формирования разрядов частного значений из блоков регистра остатка и делителя и осуществляется их суммирование.

Если РЧС=1, то осуществляется переход на блок 27 алгоритма.

В блоке 27 алгоритма осуществляется сдвиг значения блока регистра остатка на один разряд влево по команде БРОСТ:=СДВ.

В блоке 28 алгоритма по командам БСФРЧ:=ОССД и БСФРЧ:=ДТ производится загрузка в блок суммы и формирования разрядов частного значений из блоков регистра остатка и делителя и осуществляется вычитание делителя из остатка.

По выходу из блока 28 осуществляется на вход блока 20 алгоритма.

По единичному выходу блока 20 алгоритма, в случае невыполнения условия ГИ>Н32, происходит переход на блок 29 алгоритма.

Пункт 29 алгоритма является конечным блоком алгоритма.

Работа делителя на нейронах заключается в следующем.

Внешние управляющие сигналы "Пуск" и "Сброс" поступают в блок 8 управления.

С выхода шифратора поступают в регистры делимого и делителя двоичные числа А2 и В2. На сумматоре по модулю два определяется знак результата.

Блок 1 ввода чисел содержит шифратор (обычная стандартная клавиатура) ШФ DD9, сумматор по модулю два DD10 (фиг.2). Этот блок позволяет вводить двоичные числа. С выхода шифратора формируется двоичный код чисел со своими знаками: А2, В2, ЗрА, ЗрВ. Знаковые разряды ЗрА, ЗрВ с выхода шифратора поступают на вход сумматора по модулю два, где определяется знаковый разряд частного ЗрЧ, равный ЗрЧ=ЗрА ⊕ ЗрВ, где ⊕ сумма по модулю два. Если знаки делимого и делителя равны, то знак частного равен нулю - число будет положительное, если знаки разные, то частное будет иметь знак, равный единице, т.е. отрицательное. Сигнал знакового разряда частного ЗрЧ формируется на выходе элемента DD10 (фиг.2).

Блок 2 регистра делимого содержит n - триггеров Трn, где n - количество разрядов входного числа, регистр построен на элементах: DD11, DD12, DD13, DD14 (фиг.3). Этот блок предназначен для хранения двоичного кода делимого. Перед началом работы делителя по приходу из блока 8 управляющего сигнала ОБ происходит обнуление всех триггеров блока. По приходу из блока 1 ввода данных информационного сигнала ВД - входные данные осуществляется загрузка двоичного кода делимого. На входы триггеров поступают двоичные разряды делимого. При поступлении управляющего сигнала СЗДМ - сигнал записи делимого на входы триггеров Тр1, Тр2, Тр3,...,Трn из блока 8, разрешающего записать информацию в триггеры, происходит загрузка поступившего кода в триггеры блока. Сигнал СЗДМ является входным управляющим сигналом для всех элементов памяти блока. По приходу управляющего сигнала сдвига СИН из блока 8 управления, поступающего на входы всех триггеров блока, осуществляется общая синхронизация процессов записи и выдачи.

Блок 3 регистра остатка содержит k - триггеров Tpk, где k - количество разрядов делимого: DD15, DD16, DD17, DD18 (фиг.4). Этот блок предназначен для хранения двоичного кода остатка. Перед началом работы делителя по приходу из блока 8 управляющего сигнала ОБЛ происходит обнуление всех триггеров блока. По приходу из блока 4 суммы и формированию разрядов частного информационного сигнала ОСТ - остаток осуществляется загрузка двоичного кода остатка в триггеры блока. На входы триггеров поступают двоичные разряды остатка. При поступлении управляющего сигнала РЗРД - разрешение записи остатка на входы триггеров Тр1, Тр2, Тр3,...,Tpk из блока 8, разрешающего записать информацию в триггеры, происходит загрузка поступившего кода в триггеры блока. Сигнал РЗРД является входным управляющим сигналом для всех элементов памяти блока. По приходу управляющего сигнала сдвига СДВ из блока 8 управления, поступающего на входы всех триггеров блока, осуществляется операция сдвига влево информации на один разряд. Двоичный код числа, записанный в триггерах, будет сдвинут на один разряд влево. На выходе первого триггера Tp1 DD15 блока будет поступать очередной разряд двоичного числа остатка по приходу сигнала сдвига СДВ. Триггеры этого блока образуют реверсивный регистр со сдвигом информации на один разряд влево.

Блок 4 суммы и формирования разряда частного (фиг.5, 6) содержит логические элементы ИЛИ1, ИЛИ2,...,ИЛИk, выполненные на элементах DD22, DD23, DD24,...,DD25 (фиг.5), k - одноразрядных сумматоров-вычитателей CУM-BЫЧk, выполненных на комбинационых схемах DD26, DD27, DD28,...,DDk. Блок предназначен для формирования информационного сигнала ОСДМ - собирательного сигнала по функции ИЛИ делимого и остатка, поступающего на входы сумматоров-вычитателей, вычисления разрядов частного и знакового разряда остатка - ЧАСТ. На первом такте работы делителя на вторые входы сумматора-вычитателя поступают двоичные разряды делимого ЗрiДМ, на первые входы этого же блока поступают двоичные разряды делителя ЗрiДТ для получения первого остатка и формирования первого разряда частного. Со второго такта и до получения частного заданной точности на второй вход сумматора-вычитателя поступает сдвинутый на один разряд остаток из блока остатка (фиг.1). Информационный сигнал ОСДМ - остаток-делимое равен по разрядной операции дизъюнкции информационных сигналов ДМ - делимое и ОССД - остатка (фиг.5).

Для формирования информационного сигнала ОСДМ применены логические функции ИЛИ, выполненные на пороговых элементах (фиг.5) [1, 2]. Это необходимо для использования одного входа в сумматоре-вычитателе, при этом следует объединить два информационных сигнала по дизъюнкции в один (фиг.5, 6). На вход каждого одноразрядного сумматора-вычитателя поступает четыре входных двоичных числа: ЗрiOСДМ - двоичный i-разряд сдвинутого остатка, ЗрiДТ - двоичный i-разряд делителя, перенос Pi из младших разрядов в старшие при выполнении операции суммирования, Zi - заем из старших разрядов в младшие при выполнении операции вычитания, управляющий сигнал ЧАСТ - суммирования-вычитания, который является выходным сигналом СУМ-ВЫЧ1, выполняющего суммирование-вычитатние знаковых разрядов остатка и делителя и переноса из младшего разряда. Выходом каждого сумматора-вычитателя является результат суммы или разности - PEЗi и перенос/заем Pi+1/Zi-1. Управляющий сигнал ЧАСТ поступает параллельно на входы всех одноразрядный сумматоров-вычитателей (фиг.6). Значение сигнала ЧАСТ равно инверсному значению знакового разряда остатка. Если сигнал суммирования-вычитания ЧАСТ равен нулю, то это означает, что в знаковом разряде остатка получено единичное значение т.е. отрицательный остаток, при этом разряд частного будет равен нулю. После записи этого разряда частного в блок регистра частного блоком управления будет сформирован сигнал сдвига СДВ информации блока остатка влево на один разряд. Сумматор-вычитатель выполнит операцию суммирования со сдвинутым остатком и делителем. Если сигнал ЧАСТ равен единице, то это означает, что получен положительный знаковый разряд остатка, т.к. DD37 логическая схема ИЛИ-НЕ. В блок регистра частного будет записана единица как очередной разряд частного. После записи и сформированного блоком управления сигнала сдвига блок суммы и формирования разряда частного будет выполнять операцию вычитания между сдвинутым остатком и делителем. Этот цикл будет повторяться до тех пор, пока не будет получена целая часть частного и дробная часть с указанной точностью. Выходная информация в виде результата ОСТ с выхода блока суммирования-вычитания поступает на вход блока остатка (фиг.1, 6).

Одноразрядный сумматор-вычитатель СУМ-ВЫЧ1 (фиг.7) суммирования-вычитания содержит сумматор по модулю два, выполненный на формальном нейроне - элемент DD30, пороговые элементы DD31, DD32, DD33, инвертор DD34, логические схемы И DD35, DD36, логическую схему ИЛИ-НЕ DD37. Этот сумматор-вычитатель вычисляет знаковый разряд остатка, затем через инвертор формируется разряд частного ЧАСТ. На пороговом элементе (ПЭ) DD32 формируется перенос при сложении или заем при вычитании. Пороговые элементы DD32 и DD33 составляют сумматор [1,2]. На входы этих пороговых элементов поступают двоичные разряды чисел Зр1OСДМ и Зр1ДТ, а также перенос Р2 из младших разрядов в старшие (фиг.7). Двоичные разряды поступают поразрядно: Зр1OСДМ - разряд остатка, Зр1ДТ - разряд делителя, Р2 - перенос, Z1 - заем, а также признак суммирования-вычитания ЧАСТ (фиг.7). Пороговые элементы DD31 и DD32 образуют схему вычитателя чисел от остатка и делителя. Логические элементы DD35 и DD36 выполняют роль электронных ключей. Управляющим сигналом для них является признак суммирования-вычитания ЧАСТ. На пороговый элемент DD35 этот сигнал поступает на прямой вход. На пороговый элемент DD36 этот сигнал поступит через инвертор DD34. Если признак операции ЧАСТ суммирования-вычитания будет равен нулю - выполнение операции суммирования, то электронный ключ DD36 будет открыт, а ПЭ DD35 будет заперт, т.к. управляющий сигнал ЧАСТ поступает через инвертор DD34 на вход логического элемента И DD36. На выходе порогового элемента DD32 сформируется перенос из старших разрядов в следующий больший по весу разряд, если на входе порогового элемента DD32 будет не менее двух единиц. Пороговый элемент DD33 вычисляет сумму одноразрядных двоичных чисел - Зр1OСДМ и Зр1ДТ, а также перенос Р2 из младших разрядов в старшие. При суммировании через открытый элемент DD36 и схему ИЛИ-НЕ DD37 разряд суммы S1 поступит на вход блока анализа переполнения разрядной сетки. Если сигнал ЧАСТ равен единице, что означает выполнение операции вычитания. Пороговые элементы DD31 и DD32 образуют схему вычитателя. С выхода элемента DD32 формируется заем из старших разрядов в младшие. С выхода элемента DD32 вычисляется разность поступивших на вход одноразрядного сумматора-вычитателя двоичных чисел - Зр1OСДМ и Зр1ДТ, а также заема Z1 из старших разрядов в младшие. Через открытый электронный ключ DD35 и пороговый элемент DD37 (схема ИЛИ-НЕ) разряды разности R1 будут поступать на вход блока анализа переполнения разрядной сетки.

Блок 5 регистра делителя содержит z - триггеров Тр1, Тр2, ..., Tpz, где z - количество разрядов делителя. Блок делителя выполнен на элементах: DD38, DD39, DD40, DD41 (фиг.8). Этот блок предназначен для хранения двоичного кода делителя. Перед началом работы делителя по приходу из блока 8 управляющего сигнала ОБН происходит обнуление всех триггеров блока. По приходу из блока 1 ввода данных информационного сигнала ВД - входные данные осуществляется загрузка двоичного кода делителя. На входы триггеров поступают двоичные разряды делителя. При поступлении управляющего сигнала СЗДТ - сигнал записи делителя на входы триггеров Тр1, Тр2, Тр3,...,Tpz из блока 8, разрешающего записать информацию в триггеры, происходит загрузка поступившего кода в триггеры блока. Сигнал СЗДТ является входным управляющим сигналом для всех элементов памяти блока. По приходу управляющего сигнала сдвига СИНХ из блока 8 управления, поступающего на входы всех триггеров блока, осуществляется операция синхронизации в блоке. По приходу этого сигнала происходит общая команда записи в триггеры и выдачи информации из триггеров блока (фиг.8). Выходом из этого блока является двоичный код делителя - ДТ.

Блок 6 БАПРС анализа переполнения разрядной сетки содержит элемент задержки Эл.Зд, выполненный на пороговом элементе DD42, логическую схему И-ИЛИ, выполненную на нейроне DD43, два двоичных счетчика Сч1 и Сч2, выполненных на элементах DD46 и DD44 соответственно, логическую схему ИЛИ-НЕ, реализованную на пороговом элементе DD45 (фиг.9). Этот блок предназначен для определения переполнения разрядной сетки целой части частного и получения количества разрядов дробной части частного заданной точности. Если установленная разрядность - количество целой части частного и количество разрядов частного после запятой будет получена, то управляющий сигнал СП - переполнения разрядной сетки, равный единице, сформирует признак окончания операции деления. Входным сигналом блока БАПРС является сигнал ЧАСТ - знаковый разряд частного, который поступает на первый прямой и третий инверсный входы схемы И-ИЛИ DD43 и на вход элемента задержки Эл.Зд DD42 (фиг.9). На второй и четвертый входы схемы И-ИЛИ DD43 из блока управления поступает управляющий сигнал ГИ - генератор прямоугольных импульсов, на суммирующий вход двоичного счетчика Сч1 DD46 поступает из блока управления управляющий сигнал ТИ - тактовые импульсы (фиг.9). Работа блока заключается в следующем: перед выполнением операции деления необходимо определить количество разрядов целой и дробной части частного. Тактовые импульсы ТИ поступают на суммирующий вход двоичного счетчика Сч1, на выходе этого счетчика будет сформирован двоичный код, соответствующий количеству тактовых импульсов, а также количеству разрядов целой и дробной части частного. Выход счетчика Сч1 DD46 поступает на входы D1, D2, D4, D8 предварительной установки двоичного счетчика Сч2 DD44. В счетчике Сч2 DD44 будет записана двоичная информация, которая соответствует количеству разрядов частного до и после запятой. Входной сигнал ЧАСТ - знаковый разряд частного поступает на вход элемента задержки DD42, на выходе которого формируются разряды частного - РЧС, это необходимо для избежания "гонок" в электронном блоке (фиг.9). Разряды частного РЧС поступают на вход регистра блока регистра частного БРЧС (фиг.1, 10). Если знаковый разряд остатка равен 0, то в разряд частного записывается 1, если знаковый разряд равен 1, то в разряд частного записывается 0. Знаковые разряды остатков и разряды частного инверсные по отношению друг другу. Сигнал ЧАСТ поступает на вход логической схемы И-ИЛИ DD43, открывая и запирая тем самым одну из схем И. Если знаковый разряд ЧАСТ равен единице, то будет открыта верхняя секция И элемента И-ИЛИ, т.к. этот сигнал поступит на прямой вход элемента И, нижняя секция будет закрыта, потому что сигнал поступит на инверсный вход схемы И. В случае равенства сигнала ЧАСТ нулю открыта будет нижняя секция схемы И, сигнал поступит на инверсный вход, верхняя секция будет при этом заперта, сигнал поступит на прямой вход схемы И (фиг.9). Через одну открытую схему И генератор прямоугольных импульсов ГИ поступает на вычитающий вход двоичного счетчика Сч2 DD44. После получения очередного знакового разряда остатка ЧАСТ из счетчика Сч2 DD44 вычитается один импульс. Операция деления будет продолжаться до тех пор, пока на выходе двоичного счетчика Сч2 DD44 не будут получены нули. Логическая схема ИЛИ-НЕ DD45 выполняет функцию дешифратора двоичной информации. Если на входе схемы ИЛИ-НЕ будет хотя бы одна единица, то на выходе будет нуль, сигнал СП при этом равен нулю, это означает, что не все разряды частного получены, деление чисел продолжается. Если на входе схемы ИЛИ-НЕ будет нулевая информация, то на выходе будет получена единица, сигнал СП будет установлен в единичное состояние (фиг.9). Сигнал СП поступит на вход блока 8 управления (фиг.1), который сгенерирует сигнал останова выполнения операции деления чисел. Целая часть должна быть получена в зависимости от разрядной сетки делимого и делителя, а дробная часть частного должна быть получена по условию с заданной точностью.

Блок 7 регистра частного содержит s -триггеров Тр2, Тр3,...,Tps, где s - количество разрядов, необходимое для получения результата как целой части частного, так и дробной части с заданной точностью. Блок состоит из элементов: DD47, DD48, DD49 (фиг.10). Он служит для хранения двоичных разрядов результата. В состав блока входит триггер Tp1 DD50, предназначенный для хранения знакового разряда частного (фиг.10). В блоке регистра частного записывается поразрядно результат-частное после выполнении операций сложения или вычитания в блоке суммы и формирования разряда частного. Перед началом работы делителя по приходу из блока 8 управляющего сигнала УСН - установки в нуль происходит обнуление всех триггеров блока. Разряд частного РЧС, поступающий из блока анализа переполнения разрядной сетки, поступает на вход крайне правого триггера Tps DD49 блока. По приходу управляющего сигнала записи ЗЧ из блока 8 управления, поступающего на входы всех триггеров блока, осуществляется операция записи информации в триггер Tps блока. На входы всех триггеров блока поступает управляющий сигнал сдвига информации влево на один разряд из блока управления - ССД. По мере получения очередного разряда частного под управлением этого сигнала информация будет сдвигаться на один разряд влево в триггерах блока. Двоичный код частного, записанный в триггерах, будет сдвинут на один разряд влево. Операция записи очередного разряда результата и сдвига будет осуществляться до тех пор, пока не будут получены частное, целая часть и дробная часть с заданной точностью. Полученный результат будет хранится в правой части триггеров, составляющих регистр для хранения частного. На вход триггера Tp1 DD50 из блока ввода данных поступит знаковый разряд частного ЗРЧ и запишется в триггер (фиг.10). Выходной сигнал РП – регистр полон из триггера Тр2 поступает на вход блока 8 управления. Этот сигнал, равный единице, означает, что старший разряд частного находится в крайне левом триггере Тр2 блока. Если последует сигнал сдвига ССД из блока управления, то в этом случае произойдет переполнение разрядной сетки регистра блока. При этом возникнет ситуация аварийного останова работы делителя.

Одноразрядный сумматор-вычитатель СУМ-ВЫЧi (фиг.11) суммирования-вычитания содержит сумматор по модулю два, выполненный на формальном нейроне - элемент DD51, пороговые элементы DD52, DD53, DD54, инвертор DD55, логические схемы И DD56, DD57, логическую схему ИЛИ DD58. На пороговом элементе (ПЭ) DD53 формируется перенос при сложении или заем при вычитании. Пороговые элементы DD53 и DD54 составляют сумматор [1, 2]. На входы этих пороговых элементов поступают двоичные разряды чисел ЗрiOСДМ и ЗрiДТ, а также перенос Pi из младших разрядов в старшие (фиг.11). Двоичные разряды поступают поразрядно: ЗрiOСДМ - разряд остатка, ЗрiДТ - разряд делителя, Pi - перенос, Zi+1 - заем, а также разряд частного - ЧАСТ (фиг.11). Пороговые элементы DD52 и DD53 образуют схему вычитателя чисел от остатка и делителя. Логические элементы DD56 и DD57 выполняют роль электронных ключей. Управляющим сигналом для них является разряд частного ЧАСТ. На пороговый элемент DD57 этот сигнал поступает через инверторы DD55. Если признак операции ЧАСТ суммирования-вычитания будет равен нулю - выполнение операции суммирования, то электронный ключ DD57 будет открыт, а ПЭ DD56 будет заперт, т.к. управляющий сигнал ЧАСТ поступает через инвертор DD55. На выходе порогового элемента DD53 сформируется перенос из старших разрядов в следующий больший по весу разряд, если на входе порогового элемента DD53 будет не менее двух единиц. Пороговый элемент DD54 вычисляет сумму одноразрядных двоичных чисел - ЗрiOСДМ и ЗрiДТ, а также перенос Pi из младших разрядов в старшие. Если сигнал ЧАСТ равен единице, что означает выполнение операции вычитания. Пороговые элементы DD52 и DD53 образуют схему вычитателя. С выхода элемента DD53 формируется заем из старших разрядов в младшие. С выхода элемента DD52 вычисляется разность поступивших на вход одноразрядного сумматора-вычитателя двоичных чисел – ЗрiOСДМ и ЗрiДТ, а также заема Zi+1 из старших разрядов в младшие. Через открытый электронный ключ DD56 и пороговый элемент DD58 (схема ИЛИ) разряды разности Ri будут поступать на вход блока регистра остатка. Выходным сигналом элемента DD58 является результат операций суммирования или вычитания - PEЗi (фиг.11).

| Логические условия: | |

| X1: "СПР" | Х4: "РЧС" |

| Х2: "ГИ>Н31" | Х5: "ГИ>Н32" |

| Х3: "СП" | |

| Операторы: | |

| У1: "БВД:=СПР" | У11: "БСФРЧ:=ДТ" |

| У2: "БРДМ:=ОБ" | У12: "БРЧС:=ЗРЧ" |

| У3: "БРДТ:=ОБН" | У13: "БРОСТ:=ОСТ" |

| У4: "БРОСТ:=ОБЛ" | У14: "БАПРС:=ГИ" |

| У5: "БРЧС:=УСТН" | У15: "БАПРС:=ЧАСТ" |

| У6: "БРДМ:=СЗДМ" | У16: "БРЧС:=РЧС" |

| У7: "БРДТ:=СЗДТ" | У17: "БРОСТ:=СДВ" |

| У8: "БРОСТ:=РЗДР" | У18: "БСФРЧ:=ОССД" |

| У9: "БРЧС:=ЗЧ" | У19: "БСФРЧ:=ДТ" |

| У10: "БСФРЧ:=ДМ" |

Источники информации

1. Мкртчян С.О. Проектирование логических устройств ЭВМ на нейронных элементах. - М.: Энергия, 1977 г.

2. Дертоузос М. Пороговая логика. - М.: Мир, 1967 г.

3. Вавилов Е.И. и др. Синтез схем на пороговых элементах. - М.: Сов. радио.1970 г.

4. Галушкин А.И. Синтез многослойных схем распознавания образов. М.: Энергия, 1974 г.

5. Позин И.В. Моделирование нейронных структур. - М.: Наука, 1970 г.

6. Патент №3888716/24. Бюл. №11, 1990 г. от 19.04.1985 г. (прототип).

7. Патент №4380519/24. Бюл. №48, 1987 г. от 12.08.1988 г. (аналог).

8. Патент №346605/18. Бюл. №39, 1983 г. от 07.07.1982 (аналог).

Делитель на нейронах, содержащий блок регистра делителя, отли÷ающийся тем, ÷то дополнительно введены: блок ввода данных, блок регистра делимого, блок суммы и формирования р