Модуль для передачи и вещания сообщений в матричном коммутаторе

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может найти применение при построении средств коммутации многопроцессорных вычислительных и управляющих систем, абонентских систем связи с децентрализованным управлением, систем сбора информации и информационно-измерительных систем. Техническим результатом является расширение области применения устройства на основе включения в его состав средств для организации вещания сообщений на произвольную группу модулей, образующую прямоугольную конфигурацию (“прямоугольник вещания”). Для этого заявленное устройство содержит три блока организации очереди сообщений, блок анализа очередей сообщений, мультиплексор, дешифратор, блок управления вещанием, буферный регистр, триггер запуска, блок синхронизации, блоки элементов И, элемент запрета, блоки организации очереди сообщений, блок выбора направления, элемент ИЛИ, элементы И. 2 з.п. ф-лы, 9 ил., 2 табл.

Реферат

Изобретение относится к области вычислительной техники и может найти применение при построении средств коммутации многопроцессорных вычислительных и управляющих систем, абонентских систем связи с децентрализованным управлением, систем сбора информации и информационно-измерительных систем.

Известен модуль матричного коммутатора, содержащий три блока организации очередей сообщений, регистр идентификатора модуля, блок анализа очереди сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, два элемента сравнения, два дешифратора, элемент И (а.с. СССР 1575167, G 06 F 7/00, 15/16; опубл. 30.06.1990, БИ №24).

Недостатком указанного модуля является отсутствие средств для организации вещательных режимов обмена сообщениями, при которых одно и то же сообщение передается всем модулям или определенной группе модулей в структуре коммутатора. Ввиду отсутствия таких средств в рассматриваемом модуле вещание может быть реализовано только путем многократной выдачи одного и того же сообщения. Это вызывает резкое увеличение потока сообщений в пределах коммутатора, ведет к росту времени межмодульной передачи сообщений и тем самым ограничивает область применения модуля.

Наиболее близким к предлагаемому модулю по технической сущности является модуль коммуникационной сети, предназначенный для передачи сообщений, обмена сообщениями и организации вещательных режимов обмена сообщениями, содержащий блоки организации очереди сообщений с первого по третий, блок анализа очередей сообщений, мультиплексор, дешифратор, блок синхронизации, регистр, триггер, регистр адреса, два элемента сравнения, блок управления передачей сообщений, коммутатор, три блока элементов И, два элемента запрета (патент РФ 2178584, G 06 F 15/163, Н 03 К 17/56; опубл. 20.01.2002, БИ №2).

Недостатком указанного модуля является отсутствие возможности вещания на произвольную “прямоугольную конфигурацию” модулей коммуникационной сети (коммутатора).

Технической задачей изобретения является расширение области применения устройства на основе включения в его состав средств для организации вещания сообщений на произвольную группу модулей, образующую прямоугольную конфигурацию (“прямоугольник вещания”).

Техническая задача решается тем, что в модуль для передачи и вещания сообщений в матричном коммутаторе, содержащий с первого по третий блоки организации очереди сообщений, блок анализа очередей сообщений, мультиплексор, дешифратор, блок управления вещанием, буферный регистр, триггер запуска, блок синхронизации, с первого по третий блоки элементов И, элемент запрета, причем информационные входы модуля с первого по третий соединены с информационными входами блоков организации очереди сообщений с первого по третий соответственно, первые выходы которых подключены к информационным входам мультиплексора с первого по третий соответственно, вторые выходы блоков организации очереди сообщений с первого по третий подключены к входам блока анализа очередей сообщений с первого по третий соответственно, первый выход которого подключен к адресному входу мультиплексора и к входу дешифратора, выходы с первого по третий которого соединены с входами выбора блоков организации очереди сообщений с первого по третий соответственно, второй выход блока анализа очередей сообщений подключен к входу установки триггера запуска, прямой выход которого подключен к входу блока синхронизации, первый выход которого соединен с входами синхронизации блоков организации очереди сообщений с первого по третий, второй выход блока синхронизации соединен с прямым входом элемента запрета, выход которого подключен ко входу сброса триггера запуска, второй выход блока анализа очередей сообщений подключен к инверсному входу элемента запрета, выход мультиплексора подключен к первому информационному входу буферного регистра, первый выход блока синхронизации соединен с первым входом синхронизации буферного регистра, первый выход буферного регистра соединен с информационными входами первого, второго и третьего блоков элементов И, второй выход блока синхронизации подключен к информационным входам блоков элементов И с первого по третий, выходы которых являются информационными выходами модуля с первого по третий соответственно, введены четвертый и пятый блоки организации очереди сообщений, блок выбора направления, с четвертого по шестой блоки элементов И, элемент ИЛИ, с первого по третий элементы И, причем четвертый информационный вход модуля соединен с информационным входом четвертого блока организации очереди сообщений, пятый информационный вход модуля соединен с информационным входом пятого блока организации очереди сообщений, первые выходы четвертого и пятого блоков организации очереди сообщений соединены с четвертым и пятым информационными входами мультиплексора соответственно, выход которого соединен со второго по пятый информационными входами буферного регистра, вторые выходы четвертого и пятого блоков организации очереди сообщений соединены с четвертым и пятым входами блока анализа очередей сообщений соответственно, четвертый и пятый выходы дешифратора соединены с входами выбора четвертого и пятого блоков организации очереди сообщений соответственно, первый выход блока синхронизации соединен с входами синхронизации четвертого и пятого блоков организации очереди сообщений и со второго по пятый входами синхронизации буферного регистра, третий выход блока синхронизации соединен с первыми входами первого и второго элементов И, выходы которых соединены с первым и вторым входами декремента буферного регистра соответственно, четвертый выход блока синхронизации соединен с первым входом третьего элемента И, выход которого соединен со входом сброса буферного регистра, первый выход буферного регистра соединен с информационными входами четвертого и пятого блоков элементов И, второй выход буферного регистра соединен с первым входом блока выбора направления, с информационными входами с первого по четвертый блоков элементов И, третий выход буферного регистра соединен с вторым входом блока выбора направления, с информационными входами с первого по четвертый блоков элементов И, четвертый и пятый выходы буферного регистра соединены с первым и вторым входами блока управления вещанием соответственно, первый выход блока управления вещанием соединен с управляющим входом пятого блока элементов И, шестой и седьмой выходы буферного регистра соединены с третьим и четвертым входами блока выбора направления соответственно, второй выход блока управления вещанием соединен с первыми управляющими входами с первого по четвертый блоков элементов И, с третьего по шестой выходы блока управления вещанием соединены с пятого по восьмой входами блока выбора направления соответственно, четвертый выход блока управления вещанием соединен с первым входом элемента ИЛИ, пятый выход блока управления вещанием соединен с вторым входом второго элемента И, шестой выход блока управления вещанием соединен с управляющим входом шестого блока элементов И и вторым входом элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, седьмой выход блока управления вещанием соединен с вторыми управляющими входами блоков элементов И с первого по четвертый, первый выход блока выбора направления соединен с третьим входом блока управления вещанием и вторым входом третьего элемента И, со второго по пятый выходы блока выбора направления соединены с третьими управляющими входами блоков элементов И с первого по четвертый соответственно, выход четвертого блока элементов И является четвертым информационным выходом модуля, выход пятого блока элементов И является пятым информационным выходом модуля, второй и третий выходы буферного регистра подключены к четвертому и пятому входам блока управления вещанием соответственно, четвертый выход буферного регистра подключен к информационному входу шестого блока элементов И, выход которого соединен с информационными входами второго и четвертого блоков элементов И, четвертый выход буферного регистра подключен к информационным входам первого и третьего блоков элементов И, пятый выход буферного регистра подключен к информационным входам блоков элементов И с первого по четвертый.

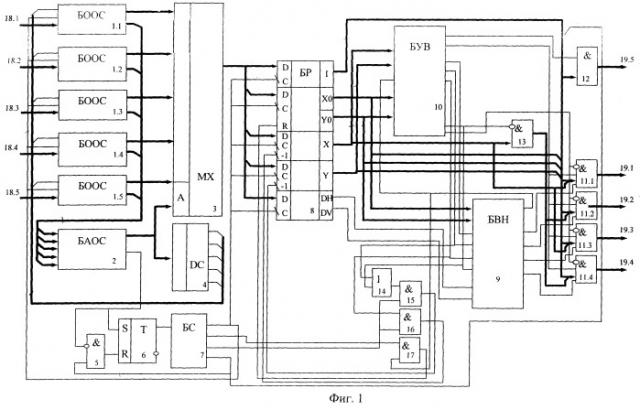

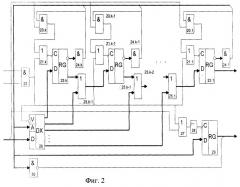

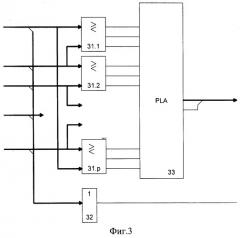

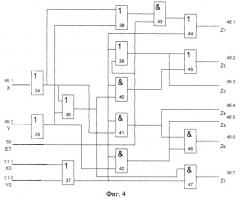

Сущность изобретения поясняется чертежами, где на фиг.1 представлена функциональная схема модуля для передачи и вещания сообщений в матричном коммутаторе; на фиг.2 изображена функциональная схема блока организации очереди сообщений; на фиг.3 показана функциональная схема блока анализа очередей сообщений; на фиг.4 приведена функциональная схема блока управления вещанием; на фиг.5 приведена функциональная схема блока выбора направления; на фиг.6 даны форматы сообщения для различных режимов работы модуля; на фиг.7 представлена граф-схема алгоритма обработки сообщения; на фиг.8 приведена структура коммутатора, а также дана иллюстрация к понятию прямоугольника вещания; фиг.9 иллюстрирует принципы организации вещания сообщений на различные конфигурации модулей.

Общие особенности изобретения состоят в следующем.

Предлагаемый модуль включается в структуру матричного коммутатора, который состоит из множества однотипных модулей, осуществляющих передачу и вещание сообщений. Коммутатор имеет вид матрицы с незамкнутыми границами (каждый модуль имеет связи со своими четырьмя соседями, а крайние модули в строках и столбцах матрицы не имеют непосредственного соединения друг с другом, фиг.8). Обмен сообщениями выполняется в параллельном коде через транзитные модули.

Каждый модуль имеет свой адрес, который определяется его координатами относительно других модулей. Адрес модуля задается парой координат А.В, где А - номер столбца модуля в матрице, а В - номер строки модуля. Нумерация идет с единицы. Левый нижний “угол” матрицы имеет координаты 1.1 (фиг.8).

Модуль реализует попарный (стандартный) режим обмена сообщениями, при котором сообщение имеет единственный приемник, а также режим вещания сообщений. При вещании у сообщения имеется несколько модулей-приемников, образующих в коммутаторе конфигурацию прямоугольной формы (прямоугольник вещания).

Размеры прямоугольника вещания (в числе элементарных шагов передачи сообщения) имеют значения Х и Y. Первое - “ширина” прямоугольника вещания, а второе - его “высота”. Значения Х=0 и Y=0 соответствуют попарному обмену. Если Х≠0 или Y≠0, то осуществляется вещание.

В режиме попарного обмена, или пока сообщение не дошло до прямоугольника вещания, сообщение перемещается по стандартному алгоритму маршрутизации: сначала оно идет вдоль строки до нужного столбца, а потом вдоль этого столбца до нужной строки (этот алгоритм используется в прототипе и поэтому подробно не рассматривается).

При вещании сообщение движется в зависимости от значений Х и Y. При Х=0 и Y≠0 сообщение движется только вдоль столбца (прямоугольник вещания имеет нулевую ширину). При Х≠0 и Y=0 сообщение идет только вдоль строки (у прямоугольника вещания нулевая высота). Если же Х≠0 и Y≠0, то сообщение перемещается по строке, при этом в каждом транзитном модуле оно “дублируется” и одновременно в столбец передается для вещания его копия. У копии устанавливается значение Х=0 (чтобы она передвигалась только вдоль столбца). Чтобы определить, достигло ли сообщение границы прямоугольника вещания, значения Х или Y с каждым новым шагом уменьшаются на 1. Как только оба они станут нулевыми, вещание сообщения прекращается (сообщение уничтожается).

Для определения того, достигло ли сообщение прямоугольника вещания (или приемника, если он единственный), оно включает адрес углового модуля прямоугольника вещания (X0.Y0). В случае попарного обмена угловым модулем является сам приемник (прямоугольник вещания условно имеет нулевой “размер”). Для задания направления вещания (вправо, потом вверх, вправо, потом вниз, влево, потом вверх или влево, потом вниз) используются два одноразрядных признака (биты DH и DV). Структура и возможные форматы сообщения (Ф1-Ф5) представлены на фиг.6. Для того чтобы отличать режим передачи сообщения до прямоугольника вещания и режим вещания в прямоугольнике, принято следующее предположение: после входа в прямоугольник значения координаты X0.Y0 устанавливаются в нуль.

Иллюстрация описанных принципов дана на фиг.9, где показаны четыре типовых варианта вещания. Черными кружками отображены модули, связи между ними для упрощения не показаны (их можно легко восстановить на основе фиг.8). Под каждым вариантом вещания даются два формата сообщения (фиг.6). Первый (тот, что расположен выше) соответствует моменту выдачи сообщения источником, а второй - моменту обработки сообщения угловым модулем прямоугольника вещания. Фиг.9 г иллюстрирует, как реализуется попарный обмен.

Модуль для передачи и вещания сообщений в матричном коммутаторе (фиг.1) содержит блоки 1.1-1.5 организации очереди сообщений, блок 2 анализа очередей сообщений, мультиплексор 3, дешифратор 4, элемент 5 запрета, триггер 6 запуска, блок 7 синхронизации, буферный регистр 8, блок 9 выбора направления, блок 10 управления вещанием, первый 11.1, второй 11.2, третий 11.3, четвертый 11.4, пятый 12 и шестой 13 блоки элементов И, элемент ИЛИ 14, с первого по третий элементы И 15-17, причем с первого по третий информационные входы 18.1-18.3 модуля соединены с информационными входами блоков 1.1-1.3 организации очереди сообщений соответственно, первые выходы которых подключены к информационным входам мультиплексора 3 с первого по третий соответственно, вторые выходы блоков 1.1-1.3 организации очереди сообщений подключены к входам блока 2 анализа очередей сообщений с первого по третий соответственно, первый выход которого подключен к адресному входу мультиплексора 3 и к входу дешифратора 4, выходы с первого по третий которого соединены с входами выбора блоков 1.1-1.3 организации очереди сообщений соответственно, второй выход блока 2 анализа очередей сообщений подключен к входу установки триггера 6 запуска, прямой выход которого подключен к входу блока 7 синхронизации, первый выход которого соединен с входами синхронизации блоков 1.1-1.3 организации очереди сообщений, второй выход блока 7 синхронизации соединен с прямым входом элемента 5 запрета, выход которого подключен ко входу сброса триггера 6 запуска, второй выход блока 2 анализа очередей сообщений подключен к инверсному входу элемента 5 запрета, выход мультиплексора 3 подключен к первому информационному входу буферного регистра 8, первый выход блока 7 синхронизации соединен с первым входом синхронизации буферного регистра 8, первый выход буферного регистра 8 соединен с информационными входами блоков элементов И 11.1-11.3, второй выход блока 7 синхронизации подключен к информационным входам блоков элементов И 11.1-11.3, выходы которых являются с первого по третий информационными выходами 19.1-19.3 модуля соответственно, четвертый информационный вход 18.4 модуля соединен с информационным входом блока 1.4 организации очереди сообщений, пятый информационный вход 18.5 модуля соединен с информационным входом блока 1.5 организации очереди сообщений, первые выходы блоков 1.4, 1.5 организации очереди сообщений соединены с четвертым и пятым информационными входами мультиплексора 3 соответственно, выход которого соединен со второго по пятый информационными входами буферного регистра 8, вторые выходы блоков 1.4, 1.5 организации очереди сообщений соединены с четвертым и пятым входами блока 2 анализа очередей сообщений соответственно, четвертый и пятый выходы дешифратора 4 соединены с входами выбора блоков 1.4, 1.5 организации очереди сообщений соответственно, первый выход блока 7 синхронизации соединен с входами синхронизации блоков 1.4, 1.5 организации очереди сообщений и со второго по пятый входами синхронизации буферного регистра 8, третий выход блока 7 синхронизации соединен с первыми входами элементов И 15, 16, выходы которых соединены с первым и вторым входами декремента буферного регистра 8 соответственно, четвертый выход блока 7 синхронизации соединен с первым входом элемента И 17, выход которого соединен со входом сброса буферного регистра 8, первый выход буферного регистра 8 соединен с информационными входами блоков элементов И 11.4, 12, второй выход буферного регистра 8 соединен с первым входом блока 9 выбора направления, с информационными входами блоков элементов И 11.1-11.4, третий выход буферного регистра 8 соединен с вторым входом блока 9 выбора направления, с информационными входами блоков элементов И 11.1-11.4, четвертый и пятый выходы буферного регистра 8 соединены с первым и вторым входами блока 10 управления вещанием соответственно, первый выход блока 10 управления вещанием соединен с управляющим входом блока элементов И 12, шестой и седьмой выходы буферного регистра 8 соединены с третьим и четвертым входами блока 9 выбора направления соответственно, второй выход блока 10 управления вещанием соединен с первыми управляющими входами блоков элементов И 11.1-11.4, с третьего по шестой выходы блока 10 управления вещанием соединены с пятого по восьмой входами блока 9 выбора направления соответственно, четвертый выход блока 10 управления вещанием соединен с первым входом элемента ИЛИ 14, пятый выход блока 10 управления вещанием соединен с вторым входом элемента И 16, шестой выход блока 10 управления вещанием соединен с управляющим входом блока элементов И 13 и вторым входом элемента ИЛИ 14, выход которого соединен с вторым входом элемента И 15, седьмой выход блока 10 управления вещанием соединен с вторыми управляющими входами блоков элементов И 11.1-11.4, первый выход блока 9 выбора направления соединен с третьим входом блока 10 управления вещанием и вторым входом элемента И 17, со второго по пятый выходы блока 9 выбора направления соединены с третьими управляющими входами блоков элементов И 11.1-11.4 соответственно, выход блока элементов И 11.4 является четвертым информационным выходом 19.4 модуля, выход блока элементов И 12 является пятым информационным выходом 19.5 модуля, второй и третий выходы буферного регистра 8 подключены к четвертому и пятому входам блока 10 управления вещанием соответственно, четвертый выход буферного регистра 8 подключен к информационному входу блока элементов И 13, выход которого соединен с информационными входами блоков элементов И 11.2, 11.4, четвертый выход буферного регистра 8 подключен к информационным входам блоков элементов И 11.1, 11.3, пятый выход буферного регистра 8 подключен к информационным входам блоков элементов И 11.1-11.4, второй выход блока 7 синхронизации подключен к информационным кодам блоков элементов И 11.4 и 12.

Блок организации очереди сообщений 1.i, i=1,..., 5, (фиг.2) включает группу элементов И 20.1-20.k, где k - максимальная длина очереди сообщений, группу элементов ИЛИ 21.1-21.k, элемент И 22, регистры 23.1-23.k, группу элементов И 24.1-24.k, группу блоков элементов ИЛИ 25.1-25.k-1, демультиплексор 26, элемент ИЛИ 27, элемент задержки 28, регистр 29 длины очереди, элемент НЕ 30, причем вход выбора блока соединен с первым входом элемента И 22, выход которого соединен с первыми входами элементов ИЛИ 21.1-21.k, с управляющим входом демультиплексора 26 и с первым входом элемента ИЛИ 27, вход синхронизации блока соединен со вторым входом элемента И 22, информационный вход блока соединен с информационным входом демультиплексора 26, с первыми входами элементов И 20.1-20.k и вторым входом элемента ИЛИ 27, выходы элементов И 20.1-20.k соединены со вторыми входами элементов ИЛИ 21.1-21.k соответственно, выходы элементов ИЛИ 21.1-21.k соединены с входами синхронизации регистров 23.1-23.k соответственно, прямые выходы регистров 23.2-23.k соединены с первыми входами блоков элементов ИЛИ 25.1-25.k-l соответственно, инверсные выходы регистров 23.1-23.k соединены с входами элементов И 24.1-24.k соответственно, прямой выход регистра 23.1 является первым выходом блока, выходы элементов И 24.1-24.k соединены с первыми входами элементов И 20.1-20.k соответственно, с адресным входом демультиплексора 26, с входом элемента НЕ 30 и с информационным входом регистра 29 длины очереди, первый выход демультиплексора 26 соединен с информационным входом регистра 23.k, выходы с k-го по второй демультиплексора 26 соединены со вторыми входами блоков элементов ИЛИ со вторыми входами блоков элементов ИЛИ 25.1-25.k-1 соответственно, выходы блоков элементов ИЛИ 25.1-25.k-1 соединены с информационными входами регистров 23.1-23.k-1 соответственно, выход элемента НЕ 30 соединен со вторым выходом блока, выход элемента ИЛИ 27 соединен с входом элемента задержки 28, выход которого соединен с входом синхронизации регистра 29 длины очереди, выход которого соединен со вторым выходом блока.

Блок 2 анализа очередей сообщений (фиг.3) включает элементы сравнения 31.1-31.р, элемент ИЛИ 32, узел 33 постоянной памяти, причем входы блока соединены соответствующим образом с входами элементов 31.1-31.р сравнения и с входами элемента ИЛИ 32, выходы элементов 31.1-31.р сравнения соединены с входами узла 33 постоянной памяти, выход которого является первым выходом блока, выход элемента ИЛИ 32 является вторым выходом блока.

Блок 10 управления вещанием (фиг.4) включает первый 34, второй 35, третий 38, четвертый 44, пятый 39, шестой 45, седьмой 37, восьмой 36 элементы ИЛИ, а также первый 43, второй 40, третий 41, четвертый 42, пятый 47, шестой 46 элемента И, причем первый (49.1) и второй (49.2) входы блока подключены к входам элементов ИЛИ 34 и 35 соответственно, выходы которых соединены с первым и вторым входами элемента ИЛИ 38 соответственно, выход которого подключен к первому входу элемента И 43, выход которого соединен с первым входом элемента ИЛИ 44, выход которого является первым (48.1) выходом блока, третий (50) вход которого соединен со вторым входом элемента И 43 и с первым входом элемента ИЛИ 39, выход которого подключен к первому входу элемента ИЛИ 45, выход которого является вторым (48.2) выходом блока, четвертый (51.1) и пятый (51.2) входы которого соединены с первым и вторым входами элемента ИЛИ 37 соответственно, выход которого подключен ко второму входу элемента ИЛИ 44, к первым входам элементов И 40, 41, 42, 47 и ко второму входу элемента ИЛИ 39, выход которого соединен с третьим (48.3) выходом блока, выходы элементов ИЛИ 34 и 35 соединены со вторыми входами элементов И 41 и 42 соответственно, выходы которых подключены к четвертому (48.4) и пятому (48.5) выходам блока соответственно и к первому и второму входам элемента И 46 соответственно, выход которого является шестым (48.6) выходом блока, выходы элементов ИЛИ 34 и 35 соединены с первым и вторым входами элемента ИЛИ 36 соответственно, выход которого подключен ко второму входу элемента И 40, выход которого соединен со вторым входом элемента ИЛИ 45, выход элемента ИЛИ 36 подключен ко второму входу элемента И 47, выход которого является седьмым (48.7) выходом блока.

Блок 9 выбора направления (фиг.5) включает первый 52.1 и второй 52.2 элементы сравнения, первый 53.1 и второй 53.2 шифраторы, регистр 54, первый элемент И 55, с первого по четвертый элементы ИЛИ 56.1-56.4, со второго по пятый элементы И 57.1-57.4, с первого по четвертый элементы запрета 58.1-58.4, причем первый и второй входы блока соединены с первыми входами элементов 52.1, 52.2 сравнения соответственно, вторые входы которых подключены к первому и второму выходам регистра 54 соответственно, с первого по третий выходы элемента 52.1 сравнения соединены входами шифратора 53.1 с первого по третий соответственно, с первого по третий выходы элемента 52.2 сравнения соединены входами шифратора 53.1 с четвертого по шестой соответственно, вторые выходы элементов 52.1 и 52.2 сравнения подключены к первому и второму входам элемента И 55 соответственно, выход которого является первым выходом блока, пятый вход которого соединен с первыми входами элементов И 57.1-57.4 и с инверсными входами элементов запрета 58.1-58.4, выходы которых соединены с первыми входами элементов ИЛИ 56.1-56.4 соответственно, выходы которых являются со второго по пятый выходами блока соответственно, выходы шифратора 53.1 с первого по четвертый подключены ко вторым входам элементов И 57.1-57.4 соответственно, выходы которых соединены со вторыми входами элементов ИЛИ 56.1-56.4 соответственно, шестой, седьмой, восьмой, третий и четвертый входы блока подключены к входам шифратора 53.2 с первого по пятый соответственно, выходы с первого по четвертый которого соединены с прямыми входами элементов запрета 58.1-58.4 соответственно.

Назначение элементов модуля для передачи и вещания сообщений в матричном коммутаторе (фиг.1) состоит в следующем.

Блоки 1.1-1.5 организации очереди сообщений (БООС) предназначены для организации очередей сообщений, поступающих от четырех аналогичных модулей (фиг.8) и собственного операционного устройства (ОУ) текущего модуля.

Блок 2 анализа очередей сообщений (БАОС) служит для анализа загруженности блоков организации очереди сообщений 1.1-1.5 и организации их опроса в зависимости от длины очередей поступивших сообщений.

Мультиплексор 3 предназначен для передачи сообщения из выбранного БООС в буферный регистр 8.

Дешифратор 4 предназначен для выбора блока организации очереди сообщений, из которого осуществляется считывание сообщения.

Элемент 5 запрета служит для блокировки передачи сигнала на вход сброса триггера 6 запуска.

Триггер 6 запуска служит для управления включением и выключением блока 7 синхронизации.

Блок 7 синхронизации (БС) обеспечивает синхронизацию работы элементов модуля.

Буферный регистр 8 (БР) служит для временного хранения и модификации обрабатываемых сообщений. БР имеет секционированную организацию и включает пять независимых секций (подрегистров). Первая служит для хранения информационной части I сообщения. Вторая хранит значения Х0, Y0 (фиг.1, 6). Третья и четвертая хранят значения Х и Y соответственно. Наконец, пятая содержит значения признаков DH, DV. Вторая секция имеет вход сброса (R), подача единичного сигнала на который обнуляет разряды данной секции (для остальных секций такой вход не предусмотрен). Третья и четвертая секции имеют входы декремента (-1), подача отрицательного фронта сигнала на которые уменьшает значения этих секций, т.е. фактически являются вычитающими счетчиками. Такая организация регистра 8 позволяет наиболее просто и эффективно реализовать алгоритм обработки сообщения на фиг.7.

Блоки элементов И 11.1-11.4 служат для блокировки выдачи сообщений на выходы 19.1-19.4 модуля соответственно.

Блок элементов И 12 обеспечивает блокирование выдачи информационной части I сообщения на выход 19.5 модуля и далее в ОУ.

Блок элементов И 13 служит для модификации адресной части сообщения при необходимости генерации его копии в режиме вещания.

Элементы И 15-17 вместе с элементом ИЛИ 14 предназначены для формирования сигналов управления буферным регистром 8.

Ниже подробно рассматривается логика работы блоков 9 и 10.

Функция блока 9 выбора направления (БВН) (фиг.5) - формирование кодов направления выдачи сообщений для управления блоками элементов И 11.1-11.4. Код направления содержит 5 бит: ЕТ, L, U, R, D. Бит ЕТ (конец передачи) определяет достижение сообщением приемника в режиме попарного обмена или угла прямоугольника вещания в режиме вещания. Биты L, U, R, D кодируют направление выдачи сообщения: L - влево по строке; U - вверх по столбцу; R - вправо по строке; D - вниз по столбцу. Направление передачи сообщения при попарном обмене зависит от соотношения значений X0.Y0 и X1.Y1. В режиме вещания направление определяется признаками DH, DV, а также сигналами z4-z6, поступающими от БУВ 10.

Правило формирования битов L, U, R, D, ЕТ при попарном обмене является стандартным для матричных коммутаторов рассматриваемого вида. Таблица 1 содержит его краткую запись.

Правило формирования битов L, U, R, D при вещании описано в таблице 2 (поведение бита ЕТ в режиме вещания не имеет значения).

Таблица 1 (она реализуется шифратором 53.1) используется только в режиме попарного обмена и при доставке сообщения в прямоугольник вещания, а таблица 2 (она реализуется шифратором 53.2), наоборот, работает исключительно при вещании. Выбором таблиц управляет сигнал z3, поступающий от БУВ 10.

Блок 10 управления вещанием (БУВ) (фиг.4) - это комбинационная схема, которая в зависимости от состояния адресной части сообщения формирует 7-битовый код управления вещанием z1z2z3z4z5z6z7. Разряды этого кода формируются согласно следующим выражениям:

z1=(Х0=Х1∧Y0=Y1) ∧ (X.Y=0.0)v(X0.Y0≠0.0),

z2=(X.Y≠0.0∧X0.Y0=0.0) v (X0.Y0≠0.0∧X1.Y1≠X0.Y0),

z3=(X0.Y0≠0.0∧X1.Y1≠X0.Y0),

Z4=(X0.Y0=0.0)∧(X≠0),

Z5=(X0.Y0=0.0)∧(Y≠0),

z6=(X0.Y0=0.0)∧(X.Y≠0.0),

z7=(X0.Y0=0.0∧X=0∧Y=0).

Разряд z1 принимает единичное значение в том случае, когда текущий модуль должен принимать информационную часть I сообщения на обработку. Это возможно при попарном обмене, когда сообщение дошло до приемника, а также в режиме вещания, когда часть I должна принимать каждый модуль прямоугольника вещания.

Разряд z2 становится равным единице тогда, когда сообщение не дошло до приемника в режиме попарного обмена или до угла прямоугольника вещания в режиме вещания, а также в режиме вещания, когда требуется продолжение вещания.

Разряд Z3 имеет единичное значение, только если сообщение не достигло приемника или угла прямоугольника вещания.

Разряды z4 и z5 становятся единичными, если нужно продолжить вещание по строке и по столбцу соответственно.

Единичное значение z6 соответствует случаю, когда требуется создать копию текущего вещаемого сообщения.

Разряд z7 становится единичным, если текущее сообщение завершает вещание и должно быть уничтожено.

Для упрощения записи выражений для z1-z7 далее используются следующие дополнительные обозначения:

ЕТ:X0=X1∧Y0=Y1

В:X0.Y0=0.0

ВХ:Х≠0

BY: Y≠0

После их применения формулы для z1-z7 принимают вид:

z4=B∧BX

z5=B∧BY

z6=B∧BX∧BY

Рассмотрим работу предлагаемого модуля более детально.

Этот процесс включает несколько этапов: 1) установка исходного состояния; 2) запуск модуля; 3) обработка потоков сообщений; 4) завершение работы.

В исходном состоянии все элементы памяти модуля находятся в нулевом состоянии, поэтому на всех входах и выходах модуля находятся нулевые сигналы. Приведение модуля в это состояние происходит подачей внешнего сигнала (на фиг.1 цепи его подачи условно не показаны).

Модуль продолжает находиться в исходном состоянии до тех пор, пока на один из БООС 1.1-1.5 не поступит сообщение. В БООС 1.1 сообщение поступает с входа 18.1 от ОУ, которое обслуживается данным модулем, а в остальные БООС - от соседей текущего модуля в коммутаторе (фиг.8). После поступления сообщения в блок 1.i, оно появляется на его первом выходе. При этом на втором выходе этого блока формируется ненулевой код длины очереди сообщений. Коды длин очередей из всех БООС проходят в БАОС 2 и формируют сигналы на его выходах. На первом входе получается код того БООС, который содержит максимум сообщений, а на втором - единица, сообщающая о наличии сообщений в модуле. Эта единица устанавливает триггер 6 в единичное состояние. В результате блок 7 синхронизации начинает вырабатывать четыре сдвинутые друг относительно друга последовательности импульсов синхронизации τ1-τ4. Модуль приступает к обработке сообщений.

Обработка сообщений происходит так. Код выбора БООС из БАОС 2 поступает на адресный вход мультиплексора 3 и коммутирует сообщение из выбранного БООС в буферный регистр 8. По импульсу τ1 с блока 7 оно фиксируется в буферном регистре 8. Одновременно по импульсу τ1 происходит сдвиг очереди сообщений в выбранном БООС (этот процесс проходит так же, как в прототипе, и поэтому подробно не рассматривается). После записи сообщения в буферный регистр 8 начинается анализ его адресной части (фиг.6) согласно алгоритму (фиг.7) и определяется способ его передачи на выходы модуля. Для этого поля сообщения поступают в БУВ 10 (фиг.4) и БВН 9 (фиг.5), где происходит формирование признаков z1-z7 и ЕТ, R, U, L, D соответственно по описанным ранее формулам и таблицам 1, 2. Более подробно различные варианты обработки сообщения рассмотрены ниже.

Модуль заканчивает работу тогда, когда ни в одном из БООС не остается сообщений. В этом случае на вторых выходах всех пяти БООС (фиг.1) формируются нулевые коды. На втором выходе БАОС 2 появляется нулевой сигнал - признак отсутствия сообщений. Этот сигнал поступает на инверсный вход элемента запрета 5 и разрешает прохождение через этот элемент импульса τ4 с блока 7. Импульс τ4 поступает на вход сброса триггера 6 и сбрасывает его в нулевое состояние. В результате происходит выключение блока 7 и модуль прекращает обработку сообщений. Работа модуля возобновляется, как только в один из БООС снова поступает сообщение.

Теперь рассмотрим способы обработки сообщения, зафиксированного в буферном регистре 8.

Если сообщение имеет формат Ф1 (фиг.6), то Х=0 и Y=0 и выполняется попарный обмен. Значения Х0 и Y0 поступают в БВН 9 и сравниваются элементами 52.1, 52.2 сравнения (фиг.5) с координатами XI, Y1 текущего модуля (последние хранятся в регистре 54). Если они не совпадают, то формируется сигнал ЕТ=0, а шифратор 53.1 согласно таблице 1 формирует код направления выдачи сообщения из признаков L, U, R, D. Если они совпадают, то ЕТ=1 (сообщение пришло в приемник), а состояние шифратора 53.1 не играет роли. Одновременно значения Х0, Y0 подаются в БУВ 10 (фиг.4). БУВ 10 формирует сигнал z3=1 (этот сигнал означает, что код направления L, U, R, D будет генерировать шифратор 53.1) и сигналы z1,z2. Значение z1=1 (оно означает, что будет выдача информационной части сообщения в ОУ), если ЕТ=1. При этом z2=0. Если ЕТ=0, то, наоборот, z1=0, a z2=1 (будет выдача сообщения в соседний модуль, а не в ОУ). Сигнал z3,=1 поступает в БВН 9 и разрешает передачу кода направления L, U, R, D с шифратора 53.1 через элементы 57.1-57.4 и 56.1-56.4 на соответствующие выходы БВН 9.

Точно так же БУВ и БВН работают в режиме доставки сообщения до прямоугольника вещания (при этом есть только одно отличие в формате сообщения (фиг.6):Х≠0 или Y≠0).

После формирования сигналов z1-z7 и ЕТ, R, U, L, D при ЕТ=1 происходит модификация сообщения в БР 8. Способ модификации определяется первоначальным форматом сообщения. Сигнал ЕТ открывает элемент И 17 и обеспечивает прохождение импульса τ2 с блока 7 на вход сброса БР 8. В результате код X0.Y0 во второй секции БР 8 обнуляется, что означает переход к этапу вещания или завершение передачи сообщения. Анализ сообщения при этом продолжается с учетом новых значений Х0=0, Y0=0.

Если сообщение имеет формат Ф2, Ф3, Ф4 или Ф5 (либо формат Ф1 при Х0=0, Y0=0), то модуль реализует режим вещания (для формата Ф1 вещание будет фиктивным и сразу же завершится, поскольку сообщение уже доставлено в единственный приемник (иллюстрация дана на фиг.9 г)). Обработка сообщения в форматах Ф2-Ф5 происходит практически одинаково, поэтому можно рассмотреть только один из этих форматов. Пусть сообщение имеет формат Ф2 (фиг.6). Значения Х и Y, определяющие “размеры” прямоугольника вещания, поступают в БУВ 10 (фиг.4). В результате на его выходах 48.1-48.7 формируются сигналы z1-z7. Если Х≠0 или Y≠0, то z1=(ОУ будет принимать информационную часть I сообщения). При этом также z2=1 и z7=0, так как сообщению нужно продолжить вещание в соседний модуль. Если же Х=0, Y=0, то z7=1 (вещание заканчивается).

В режиме вещания z3=0, a z-z6 определяются значениями X.Y согласно приведенным ранее формулам. Сигнал z3=0 поступает в БВН 9 (фиг.5) и запрещает выдачу информации с выходов шифратора 53.1. Одновременно он разрешает выдачу информации с шифратора 53.2. Шифратор 53.2 в зависимости от сигналов z4-z6, а также признаков DH, DV (они приходят на третий и четвертый входы БВН соответственно) по таблице 2 вычисляет значения L, U, R, D. Они определяют способ выдачи сообщения при вещании. Одновременно сигналы z4-z6 управляют модификацией адресной части обрабатываемого сообщения. Если сигнал z4=1 (идет вещание вдоль строки матрицы) или сигнал z7=1 (идет вещание вдоль строки с генераци