Цифровой синтезатор сигналов

Иллюстрации

Показать всеИзобретение относится к радиотехнике и может быть использовано для синтеза сетки частот и формирования сигналов передачи дискретной информации. Достигаемый технический результат - повышение выходной частоты при сохранении точности формирования сигналов. Цифровой синтезатор сигналов содержит первый и второй элемент задержки, фильтр нижних частот и три параллельных канала, каждый из которых содержит счетчик импульсов, блок запоминания, цифроаналоговый преобразователь, аналоговый ключ, аналоговый сумматор и элемент задержки. 2 ил.

Реферат

Изобретение относится к радиотехнике и может быть использовано в радиопередающих, радиоприемных и радиоизмерительных устройствах для синтеза сетки частот и формирования сигналов передачи дискретной информации.

Известно устройство, описанное в книге Гнатек Ю.Р. Справочник по цифроаналоговым и аналого-цифровым преобразователям. М.: Радио и связь, 1982, с.259-260, содержащее последовательно соединенные счетчик, блок запоминания, цифроаналоговый преобразователь (ЦАП). Недостатками устройства являются пониженные выходная частота и точность формирования выходных сигналов.

Известно также устройство по авторскому свидетельству (АС) №1501245, Н 03 В 19/00, SU, содержащее сумматор кодов, ЦАП и М каналов, подключенных к соответствующим входам сумматора и к основному входу, содержащих последовательно соединенные элементы задержки, счетчики и блоки запоминания. Недостатками этого устройства являются пониженные выходная частота и точность формирования сигналов, которые определятся быстродействием оконечных устройств: сумматора кодов и ЦАП. Т.е. повышение тактовой частоты, достигнутое за счет суммирования сдвинутых во времени каналов, ограничивается быстродействием оконечных устройств. Эти оконечные устройства имеют быстродействие (тактовые частоты и время включения-выключения) сравнимое или даже меньше, чем у устройств в каждом канале.

Наиболее близким аналогом является устройство по АС №1501245, Н 03 В 19/00, SU.

Для увеличения выходной частоты при сохранении точности формирования сигналов, предложен цифровой синтезатор сигналов, содержащий: первый канал формирования, состоящий из последовательно соединенных счетчика, блока запоминания, цифро-аналогового преобразователя, а также два последовательно соединенных элемента задержки и два канала формирования, подключенных параллельно первому, каждый из которых состоит из последовательно соединенных счетчика и блока запоминания, причем вход первого элемента задержки подключен к входу счетчика первого канала, а прямые выходы первого и второго элементов задержки подключены к входам счетчиков второго и третьего параллельных каналов соответственно, отличающийся тем, что в него введены фильтр нижних частот, в первый канал формирования первый аналоговый ключ, вход которого подключен к выходу цифроаналогового преобразователя, последовательно соединенные первый аналоговый сумматор и третий элемент задержки, выход которого соединен с входом управления первого аналогового ключа, причем на первый вход аналогового сумматора подан проинвертированный входной сигнал, а второй вход соединен с инверсным выходом первого элемента задержки, во второй и третий каналы формирования последовательно соединенные цифроаналоговый преобразователь и аналоговый ключ, причем входы цифроаналоговых преобразователей соединены с выходами блоков запоминания соответствующих каналов, и последовательно соединенные второй и третий аналоговые сумматоры и четвертый и пятый элементы задержки, выходы которых соединены с входом управления аналогового ключа соответствующего канала, причем первый вход второго аналогового сумматора подключен к инверсному выходу первого элемента задержки, а второй вход к прямому выходу второго элемента задержки, первый вход третьего аналогового сумматора подключен к инверсному выходу второго элемента задержки, а второй вход к прямому входу цифрового синтезатора сигналов, а выходы аналоговых ключей всех каналов объединены и подключены к входу фильтра нижних частот, выход которого является выходом устройства.

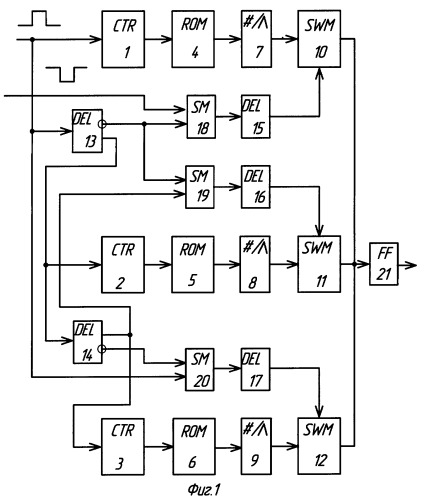

На фиг.1 приведена схема устройства. На фиг.2 временные диаграммы его работы.

На фиг.1 изображены:

1, 2, 3 - первый, второй и третий счетчики импульсов соответственно,

4, 5, 6 - первый, второй и третий блоки запоминания (запоминающие устройства) соответственно,

7, 8, 9 - первый, второй и третий ЦАП соответственно,

10, 11, 12 - первый, второй и третий аналоговые ключи соответственно,

13, 14, 15, 16, 17 - первый, второй, третий, четвертый и пятый элементы задержки соответственно,

18, 19, 20 - первый, второй и третий аналоговые сумматоры соответственно,

21 - фильтр нижних частот (ФНЧ).

Цифровой синтезатор сигналов содержит: три счетчика импульсов 1, 2, 3, три блока запоминания 4, 5, 6, три ЦАП 7, 8, 9, три аналоговых ключа 10, 11, 12, пять элементов задержки 13, 14, 15, 16, 17, причем два из них (13 и 14) с прямым и инверсным выходами, три аналоговых сумматора 18, 19, 20 и ФНЧ 21.

Синтезатор сигналов работает следующим образом.

Для простоты будем считать, что все цифровые устройства имеют одинаковое быстродействие (время включения и выключения) и используются на максимальной тактовой частоте. Поэтому, на входы (прямой и инверсный) синтезатора сигналов поступают сигналы, длительность импульса которых равна времени паузы, т.е. в виде меандра (диаграммы а, б на фиг.2). Элементы задержки 13 и 14 задерживают входные сигналы примерно на треть периода (диаграммы в, г, и д, е на фиг.2), а на выходе аналоговых сумматоров 18, 19, 20 образуются укороченные импульсы, длительность которых меньше, чем позволяет быстродействие цифровых устройств. Они через элементы задержки 15, 16, 17 поступают на аналоговые ключи 10, 11, 12, быстродействие которых значительно выше быстродействия цифровых устройств и с их помощью формируется ступенчатая функция выходного сигнала. Счетчики 1, 2, 3 вырабатывают код адреса, под воздействием которого осуществляется считывание кода амплитуды формируемого сигнала из блоков запоминания 4, 5, 6. ЦАП 7, 8, 9 осуществляют переход от кода к аналоговому значению сигнала, а аналоговые ключи 10, 11, 12 нарезают из сигналов ЦАП 7, 8, 9 импульсы с амплитудой, соответствующей выходному сигналу в заданных точках. Поскольку, импульсы с выходов аналоговых ключей разделены во времени, на входе ФНЧ 21 образуется ступенчатая функция, соответствующая форме выходного сигнала, а на выходе ФНЧ 21 - очищенный от помех сигнал. Элементы задержки 15, 16, 17 служат для компенсации задержек, которые накапливаются в последовательно соединенных счетчиках, запоминающих устройствах и ЦАП, каждого из каналов.

Приведенный на фиг.1 синтезатор позволяет получить в три раза больше точек в периоде формируемого сигнала, либо в три раза повысить выходную частоту при сохранении точности формируемого сигнала.

Таким образом, при одном и том же быстродействии цифровых устройств заявленное устройство позволяет трехкратно повысить выходную частоту по сравнению с аналогом.

Все элементы устройства могут быть выполнены на стандартной элементной базе, и не имеют каких-либо особенностей.

Цифровой синтезатор сигналов, содержащий первый канал формирования, состоящий из последовательно соединенных первого счетчика импульсов, первого блока запоминания, первого цифроаналогового преобразователя, а также последовательно соединенные первый и второй элементы задержки и второй и третий каналы формирования, подключенные параллельно первому, каждый из которых состоит из последовательно соединенных второго счетчика импульсов и второго блока запоминания, третьего счетчика импульсов и третьего блока запоминания соответственно, причем вход первого элемента задержки подключен к входу первого счетчика импульсов, а прямые выходы первого и второго элементов задержки подключены к входам второго и третьего счетчиков импульсов соответственно,отличающийся тем, что в него введены фильтр нижних частот, а в первый канал формирования - первый аналоговый ключ, вход которого подключен к выходу первого цифроаналогового преобразователя, а также последовательно соединенные первый аналоговый сумматор и третий элемент задержки, выход которого соединен со входом управления первого аналогового ключа, причем на первый вход первого аналогового сумматора подан проинвертированный входной сигнал, а второй вход соединен с инверсным выходом первого элемента задержки, во второй и третий каналы формирования введены последовательно соединенные второй цифроаналоговый преобразователь и второй аналоговый ключ, третий цифроаналоговый преобразователь и третий аналоговый ключ соответственно, причем входы цифроаналоговых преобразователей соединены с выходами блоков запоминания соответствующих каналов, и последовательно соединенные второй аналоговый сумматор и четвертый элемент задержки, последовательно соединенные третий аналоговый сумматор, пятый элемент задержки, причем выходы элементов задержки соединены со входами управления аналоговых ключей соответствующего канала, первый вход второго аналогового сумматора подключен к инверсному выходу первого элемента задержки, а второй вход к прямому выходу второго элемента задержки, первый вход третьего аналогового сумматора подключен к инверсному выходу второго элемента задержки, а второй вход к прямому входу цифрового синтезатора сигналов, а выходы аналоговых ключей всех каналов объединены и подключены к входу фильтра нижних частот, выход которого является выходом устройства.