Блок приемника сигналов спутниковых радионавигационных систем с внешней синхронизацией

Иллюстрации

Показать всеИзобретение относится к радиотехнике и может быть использовано при конструировании блоков приемников сигналов спутниковых радионавигационных систем с внешней синхронизацией. Достигаемым техническим результатом является получение блока, обладающего расширенными возможностями по использованию, в частности, в условиях удаленного расположения внешнего опорного генератора и внешнего источника питания, при этом одновременно обеспечивается электромагнитная совместимость входящих в блок функциональных улов. Для этого в состав блока, содержащего плату приемника-процессора, введены три буферных узла, обеспечивающих получение из внешнего синхронизирующего опорного сигнала необходимого синхронизирующего опорного сигнала для платы приемника-процессора и дублирующего его опорного сигнала, и источник внутриблочного питания, обеспечивающий формирование из внешнего напряжения питания двух раздельных внутриблочных напряжений питания для буферных узлов и платы приемника процессора. Плата приемника-процессора, источник внутриблочного питания и буферные узлы размещены на общей несущей печатной плате, причем буферные узлы размещены в экранируемых зонах. Экранировка зон размещения буферных узлов осуществлена по периметру с помощью экранирующих проводников, а по плоскости - с помощью земляных участков. Экранирующие проводники и земляные участки соединены двумя отдельными земляными проводниками с контактом "Земля питания буферных узлов", а расположенные внутри экранируемых зон контакты питания буферных узлов соединены тремя отдельными проводниками питания с контактом "Питание буферных узлов". 3 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к радиотехнике и может быть использовано при конструировании блоков приемников сигналов спутниковых радионавигационных систем (СРНС) типа ГЛОНАСС, GPS и т.п., в которых для синхронизации процессов обработки сигналов СРНС при получении навигационной и/или временной информации используются внешние синхронизирующие опорные сигналы (сигналы внешней синхронизации).

Типичная функциональная схема блока приемника сигналов СРНС, осуществляющего прием и обработку сигналов СРНС с выделением навигационной и/или временной информации, содержит преобразователь частоты, выполненный по супергетеродинной схеме с преобразованием частоты вниз, аналого-цифровой преобразователь, цифровой коррелятор, вычислитель и преобразователь интерфейса, см., например, [1], [2], [3], [4]. Как правило, указанные функциональные узлы размещаются на одной печатной плате - плате приемника-процессора, например, как описано в [5], [6], [7], [8]. Работа функциональных узлов платы приемника-процессора осуществляется под воздействием тактового и гетеродинных сигналов, формируемых из синхронизирующего опорного сигнала. Для работы функциональных узлов требуется соответствующее электропитание.

Обеспечение блока приемника сигналов СРНС синхронизирующим опорным сигналом может осуществляться двумя путями, а именно, с помощью внутриблочного опорного генератора, реализованного на кварцевом генераторе, как это описано, например, в [3], [4], [5], либо с помощью внешнего опорного генератора, например стандарта частоты, как в [9]. Применение в качестве внешнего опорного генератора стандарта частоты позволяет, по сравнению с кварцевым генератором, уменьшить временную нестабильность формируемых навигационных сигналов и сигналов времени, обусловленную временной нестабильностью синхронизирующего опорного сигнала. Применение внешней синхронизации требует, по меньшей мере, оснащения платы приемника-процессора дополнительными соединительными средствами, обеспечивающими возможность подвода сигналов внешней синхронизации, например, как это реализовано в [8].

Обеспечение блока приемника сигналов СРНС электропитанием может осуществляться либо напрямую от внешнего источника питания, как это реализовано, например, в [5], [6], [7], [8], либо через дополнительный источник внутриблочного питания (обычно импульсный преобразователь-стабилизатор постоянного напряжения в постоянное), формирующий стабилизированное внутриблочное напряжение питания нужного уровня из внешнего напряжения питания, поступающего от внешнего источника питания, как это реализовано, например, в [10]. Во втором случае обеспечивается определенная независимость работы блока приемника сигналов СРНС от значений внешнего напряжения питания, а также, в определенной мере, снимаются ограничения на расстояние, на которое могут быть разнесены между собой приемник сигналов СРНС и внешний источник питания.

Настоящее изобретение относится к случаю блока приемника сигналов СРНС с внешней синхронизацией, в котором синхронизирующий опорный сигнал для платы приемника-процессора, а также дублирующий его сигнал формируются с помощью буферных узлов из внешнего синхронизирующего опорного сигнала, поступающего от внешнего опорного генератора, а внутриблочное напряжение питания формируется с помощью источника внутриблочного питания из внешнего напряжения питания, поступающего от внешнего источника питания. При этом решается конструкторская задача обеспечения электромагнитной совместимости платы приемника-процессора, источника внутриблочного питания и буферных узлов.

В качестве прототипа выбран известный из [8] блок приемника сигналов СРНС, конструкция которого предусматривает возможность работы с сигналом внешней синхронизации. Блок-прототип содержит плату приемника-процессора, предназначенную для частотного преобразования и корреляционной обработки сигналов СРНС. Плата приемника-процессора выполнена в виде многослойной печатной платы, в которой на наружных проводящих слоях размещены низкочастотный соединитель, первый и второй высокочастотные соединители, а также сгруппированные по функциональным зонам в соответствии с характерными этапами обработки сигналов СРНС проводники и электрорадиоэлементы, а во внутренних проводящих слоях в соответствии с расположением функциональных зон размещены проводники, плоскости питания и земляные плоскости, причем земляные плоскости функциональных зон образуют в своей совокупности внутриплатный плоскостной экран, служащий для защиты функциональных узлов платы приемника-процессора от паразитных наводок и наведенных помех, передаваемых, в основном, по цепям питания. Характерными этапами обработки сигналов СРНС, в соответствии с которыми произведена группировка электрорадиоэлементов по функциональным зонам, являются радиочастотное преобразование с понижением частоты сигналов, аналого-цифровое преобразование, обработка в многоканальном цифровом корреляторе, обработка в цифровом вычислителе и обработка в преобразователе интерфейса. Первый высокочастотный соединитель предназначен для присоединения коаксиального кабеля, по которому на плату приемника-процессора поступают сигналы СРНС от антенного устройства. Второй высокочастотный соединитель предназначен для присоединения коаксиального кабеля, по которому на плату приемника-процессора поступает синхронизирующий опорный сигнал от внешнего опорного генератора. Низкочастотный соединитель предназначен для присоединения проводного жгута, по которому на плату приемника-процессора поступают управляющие сигналы от внешнего управляющего устройства и напряжение питания от внешнего источника питания и снимаются обработанные сигналы и данные.

Работа блока-прототипа осуществляется следующим образом. Через низкочастотный соединитель на плату приемника-процессора поступает напряжение питания от внешнего источника питания. Через первый высокочастотный соединитель от антенного устройства на плату приемника-процессора поступают сигналы СРНС, например сигналы ГЛОНАСС и GPS в диапазоне частот от 1200 до 1700 МГц. Через второй высокочастотный соединитель от внешнего опорного генератора на плату приемника-процессора поступает синхронизирующий опорный сигнал. На плате приемника-процессора напряжение питания фильтруется и поступает к активным элементам функциональных зон, где осуществляется поэтапная обработка сигналов СРНС, а из синхронизирующего опорного сигнала формируются необходимые для этой обработки тактовый и гетеродинные сигналы. В первой функциональной зоне сигналы СРНС усиливаются, фильтруются от помех и преобразуются по частоте по схеме супергетеродинного преобразования с понижением частоты до десятков мегагерц. Далее сигналы преобразуются в цифровой вид в функциональной зоне аналого-цифрового преобразователя, затем подвергаются цифровой корреляционной обработке в функциональной зоне многоканального цифрового коррелятора. После этого сигналы обрабатываются в функциональной зоне цифрового вычислителя, далее - в функциональной зоне преобразователя интерфейса, после чего поступают на выход платы приемника-процессора через низкочастотный соединитель. Преобразование сигналов по частоте осуществляется под действием гетеродинных сигналов, а аналого-цифровое преобразование и цифровая обработка - под действием тактового сигнала.

В результате в блоке-прототипе осуществляется частотное преобразование сигналов СРНС, их цифровая обработка и формирование выходных сигналов, несущих данные, используемые потребителем при определении местоположения, при определении точного времени, при осуществлении временной “привязки” по сигналам СРНС. При этом применение внешней синхронизации, например стандарта частоты в качестве внешнего опорного генератора, позволяет уменьшить временную нестабильность формируемых выходных сигналов по сравнению со случаем использования внутриблочного кварцевого генератора.

Блок-прототип не содержит средств для согласования входных характеристик платы приемника-процессора с выходными характеристиками тракта, по которому на плату приемника-процессора поступает внешний синхронизирующий опорный сигнал от внешнего опорного генератора, а также средств для формирования необходимого внутриблочного питания из внешнего напряжения питания. Это ограничивает возможности по использованию блока-прототипа, в частности, затрудняет использование в условиях удаленного расположения внешнего опорного генератора и внешнего источника питания.

Задачей, на решение которой направлено заявляемое изобретение, является разработка конструкции блока приемника сигналов СРНС с внешней синхронизацией, обладающего расширенными возможностями по использованию, в частности, возможностями по использованию в условиях удаленного расположения внешнего опорного генератора и внешнего источника питания. Задача решается за счет введения в состав блока приемника сигналов СРНС с внешней синхронизацией дополнительных буферных узлов, обеспечивающих согласование входных характеристик платы приемника-процессора с выходными характеристиками тракта, по которому осуществляется поступление внешнего синхронизирующего опорного сигнала от внешнего опорного генератора, и получение из внешнего синхронизирующего опорного сигнала необходимого синхронизирующего опорного сигнала для платы приемника-процессора и дублирующего его опорного сигнала, а также введения в состав блока дополнительного источника внутриблочного питания, формирующего необходимые напряжения питания для буферных узлов и платы приемника-процессора из внешнего напряжения питания.

При этом решается возникающая в таком блоке проблема обеспечения электромагнитной совместимости платы приемника-процессора, источника внутриблочного питания и буферных узлов. Проблема обусловлена тем, что указанные технические средства работают с разными по уровню, форме и частоте сигналами и их простое объединение в рамках одного конструктивного блока может сопровождаться возникновением паразитных наводок и наведенных помех. В заявляемом изобретении эта проблема решена путем размещения буферных узлов в трех граничащих друг с другом и экранируемых определенным образом (с помощью экранирующих проводников и земляных участков) зонах с одновременным осуществлением раздельного питания каждого из буферных узлов и платы приемника-процессора с помощью определенным образом расположенных и связанных с источником внутриблочного питания проводников.

Сущность заявляемого изобретения заключается в том, что в блоке приемника сигналов СРНС с внешней синхронизацией, содержащем плату приемника-процессора, предназначенную для частотного преобразования и корреляционной обработки сигналов СРНС, снабженную первым высокочастотным соединителем, предназначенным для подвода к плате приемника-процессора сигналов СРНС, вторым высокочастотным соединителем, предназначенным для подвода к плате приемника-процессора синхронизирующего опорного сигнала, и низкочастотным соединителем, предназначенным для подвода к плате приемника-процессора напряжения питания и управляющих сигналов и отвода от нее обработанных сигналов и данных, в отличие от прототипа, плата приемника-процессора размещена на несущей печатной плате и соединена к ней посредством указанного низкочастотного соединителя, соединенного с размещенным на несущей печатной плате внутриблочным соединителем, при этом на несущей печатной плате на ее лицевой стороне размещены электрорадиоэлементы, образующие первый, второй и третий буферные узлы, из которых первый служит для получения из внешнего синхронизирующего опорного сигнала промежуточного опорного сигнала, второй - для получения из промежуточного опорного сигнала синхронизирующего опорного сигнала для платы приемника-процессора, а третий - для получения из промежуточного опорного сигнала дублирующего опорного сигнала. На лицевой стороне несущей печатной платы также размещены электрорадиоэлементы, образующие источник внутриблочного питания, служащий для формирования из внешнего напряжения питания внутриблочных напряжений питания для буферных узлов и платы приемника процессора соответственно на парах контактов “Питание буферных узлов” - “Земля питания буферных узлов” и “Питание платы приемника-процессора” - “Земля питания платы приемника-процессора”, причем с контактами “Питание платы приемника-процессора” и “Земля питания платы приемника-процессора” соединены соответствующие проводники цепи питания платы приемника-процессора, связывающие эти контакты с соответствующими выводами внутриблочного соединителя, а с контактами “Питание буферных узлов” и “Земля питания буферных узлов” соединены проводники цепи питания буферных узлов, служащие для раздельного подвода напряжения питания к первому, второму и третьему буферным узлам, при этом с контактом “Питание буферных узлов” соединены первые концы расположенных на лицевой стороне несущей печатной платы первого, второго и третьего проводников питания цепи питания буферных узлов, а с контактом “Земля питания буферных узлов” соединен первый конец расположенного на тыльной стороне несущей печатной платы общего земляного проводника цепи питания буферных узлов. Несущая печатная плата снабжена также соединительными средствами для внешних подключений, служащими для подвода к несущей печатной плате внешнего напряжения питания для источника внутриблочного питания и управляющих сигналов для платы приемника-процессора и отвода от несущей печатной платы обработанных в плате приемника-процессора сигналов и данных, причем эти соединительные средства связаны на несущей печатной плате с источником внутриблочного питания и внутриблочным соединителем. Электрорадиоэлементы, образующие первый, второй и третий буферные узлы, сгруппированы в трех граничащих друг с другом экранируемых зонах, окруженных по своим периметрам экранирующими проводниками, которые выполнены на лицевой и тыльной сторонах несущей печатной платы друг под другом, имеют разрывы для прохождения проводников, пересекающих границы экранируемых зон, соединены между собой металлизированными соединительными отверстиями, а также соединены посредством отдельного земляного проводника, расположенного на тыльной стороне несущей печатной платы, с контактом “Земля питания буферных узлов”. Внутри первой экранируемой зоны - зоны первого буферного узла - на лицевой стороне несущей печатной платы размещены выходной сигнальный контакт первого буферного узла, его входные сигнальный и земляной контакты, служащие для присоединения к ним центральной жилы и экранирующей оплетки коаксиального кабеля, предназначенного для подвода к первому буферному узлу внешнего синхронизирующего опорного сигнала от внешнего опорного генератора, а также его контакт питания, к которому присоединен второй конец первого проводника питания цепи питания буферных узлов. Внутри второй экранируемой зоны - зоны второго буферного узла - на лицевой стороне несущей печатной платы размещены входной сигнальный контакт второго буферного узла, его выходные сигнальный и земляной контакты, к которым присоединены центральная жила и экранирующая оплетка коаксиального кабеля, связывающего плату приемника-процессора через ее второй высокочастотный соединитель с вторым буферным узлом, а также его контакт питания, к которому присоединен второй конец второго проводника питания цепи питания буферных узлов. Внутри третьей экранируемой зоны - зоны третьего буферного узла - на лицевой стороне несущей печатной платы размещены входной сигнальный контакт третьего буферного узла, его выходные сигнальный и земляной контакты, служащие для присоединения к ним центральной жилы и экранирующей оплетки коаксиального кабеля, предназначенного для отвода дублирующего опорного сигнала от третьего буферного узла, а также его контакт питания, к которому присоединен второй конец третьего проводника питания цепи питания буферных узлов. При этом выходной сигнальный контакт первого буферного узла соединен с входными сигнальными контактами второго и третьего буферных узлов посредством выполненных на лицевой стороне несущей печатной платы первого и второго проводников связи буферных узлов. На тыльной стороне несущей печатной платы внутри каждой из экранируемых зон расположены земляные участки соответствующих буферных узлов, причем к земляному участку, относящемуся к первому буферному узлу, присоединен второй конец общего земляного проводника цепи питания буферных узлов, а кроме этого этот земляной участок соединен с земляными участками, относящимися к второму и третьему буферным узлам, посредством первой и второй земляных перемычек, расположенных в соответствии с расположением на лицевой стороне несущей печатной платы первого и второго проводников связи буферных узлов.

В варианте реализации, имеющем практическое значение, плата приемника-процессора размещена на лицевой стороне несущей печатной платы между источником внутриблочного питания и буферными узлами, источник внутриблочного питания выполнен в виде последовательно соединенных входного фильтра питания и первого и второго преобразователей-стабилизаторов напряжения, причем выходные контакты первого преобразователя-стабилизатора напряжения, соединенные с входными контактами второго преобразователя-стабилизатора напряжения, образуют пару контактов “Питание буферных узлов” - “Земля питания буферных узлов”, а выходные контакты второго преобразователя-стабилизатора напряжения образуют пару контактов “Питание платы приемника-процессора” - “Земля питания платы приемника-процессора”, а входной фильтр питания выполнен в виде четырехполюсника, в продольных плечах которого включены индуктивные компоненты, имеющие общую индуктивную связь, а в поперечных плечах - соединенные с ними емкостные компоненты, причем один из двух выходных выводов четырехполюсника является потенциальным выводом входного фильтра питания, а другой - его земляным выводом.

Сущность изобретения, его реализуемость и возможность промышленного применения поясняются представленными на фиг.1-4 чертежами, где:

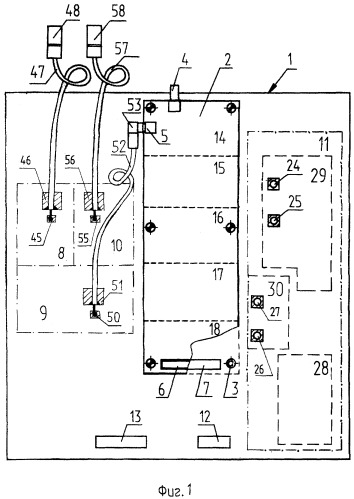

на фиг.1 представлен схематический чертеж заявляемого блока приемника сигналов СРНС с внешней синхронизацией в рассматриваемом примере выполнения, поясняющий взаимное расположение на несущей печатной плате источника внутриблочного питания, платы приемника-процессора и буферных узлов, а также присоединение к буферным узлам коаксиальных кабелей (несущая печатная плата и плата приемника-процессора показаны условно без электрорадиоэлементов, границы расположения буферных узлов и источника внутриблочного питания показаны условно штрихпунктирными линиями);

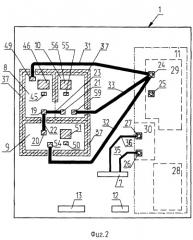

на фиг.2 - схематический чертеж, поясняющий выполнение на лицевой стороне несущей печатной платы экранирующих проводников, проводников связи и проводников питания буферных узлов, а также проводников питания платы приемника-процессора (границы расположения буферных узлов и источника внутриблочного питания показаны условно штрихпунктирными линиями);

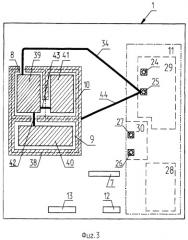

на фиг.3 - схематический чертеж, поясняющий выполнение на тыльной стороне несущей печатной платы экранирующих проводников и земляных участков буферных узлов, а также земляных проводников, соединяющих их с контактом “Земля питания буферных узлов” (вид “на просвет”, несущая печатная плата условно прозрачная, границы расположения буферных узлов и источника внутриблочного питания показаны условно штрихпунктирными линиями);

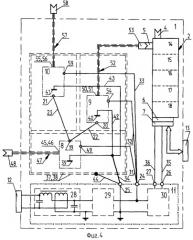

на фиг.4 - функциональная схема, иллюстрирующая электрические связи между источником внутриблочного питания, платой приемника процессора и буферными узлами.

Заявляемый блок приемника сигналов СРНС с внешней синхронизацией в рассматриваемом примере выполнения (фиг.1-4) содержит несущую печатную плату 1, на лицевой стороне которой размещена плата приемника-процессора 2, предназначенная для частотного преобразования и корреляционной обработки сигналов СРНС, например сигналов ГЛОНАСС и GPS. Плата приемника-процессора 2 закреплена на несущей печатной плате 1 в горизонтальном положении на крепежных стойках 3 (фиг.1).

Плата приемника-процессора 2 снабжена первым высокочастотным соединителем 4, предназначенным для подвода к плате приемника-процессора 2 сигналов СРНС, вторым высокочастотным соединителем 5, предназначенным для подвода к плате приемника-процессора 2 синхронизирующего опорного сигнала, и низкочастотным соединителем 6, предназначенным для подвода к плате приемника-процессора 2 напряжения питания и управляющих сигналов и отвода от нее обработанных сигналов и данных.

Плата приемника-процессора 2 электрически соединена с несущей печатной платой 1 посредством своего низкочастотного соединителя 6, соединенного с размещенным на несущей печатной плате 1 внутриблочным соединителем 7.

На лицевой стороне несущей печатной платы 1 помимо платы приемника-процессора 2 размещены электрорадиоэлементы, образующие первый 8, второй 9 и третий 10 буферные узлы, а также электрорадиоэлементы, образующие источник внутриблочного питания 11, при этом плата приемника-процессора 2 размещена между источником внутриблочного питания 11 и буферными узлами 8, 9, 10 (фиг.1, 2). На тыльной стороне несущей печатной платы 1 электрорадиоэлементов нет (фиг.3).

Несущая печатная плата 1 снабжена соединительными средствами для внешних подключений - в рассматриваемом примере это низкочастотный соединитель 12, служащий для подвода к несущей печатной плате 1 внешнего напряжения питания для источника внутриблочного питания 11, и низкочастотный соединитель 13, служащий для подвода к несущей печатной плате 1 управляющих сигналов для платы приемника-процессора 2 и отвода от несущей печатной платы 1 обработанных в плате приемника-процессора 2 сигналов и данных. Низкочастотные соединители 12 и 13 связаны на несущей печатной плате 1 с источником внутриблочного питания 11 и внутриблочным соединителем 7 соответствующими электрическими цепями (фиг.4).

Плата приемника-процессора 2 выполнена, например, в виде многослойной печатной платы, в которой на наружных проводящих слоях размещены соединители 4, 5 и 6, а также печатные проводники и сгруппированные по функциональным зонам в соответствии с характерными этапами обработки сигналов СРНС электрорадиоэлементы, образующие электрическую схему приемника-процессора. Во внутренних проводящих слоях платы приемника-процессора 2 в соответствии с расположением функциональных зон размещены проводники, плоскости питания и земляные плоскости, причем земляные плоскости функциональных зон образуют в своей совокупности внутриплатный плоскостной экран, служащий для защиты функциональных узлов платы приемника-процессора 2 от паразитных наводок и наведенных помех, передаваемых на плате приемника-процессора 2 по цепям питания.

Пример расположения функциональных зон в плате приемника-процессора 2 показан (условно) на фиг.1, где первая функциональная зона 14 представляет собой функциональную зону радиочастотного преобразователя, вторая функциональная зона 15 представляет собой функциональную зону аналого-цифрового преобразователя, третья функциональная зона 16 представляет собой функциональную зону многоканального цифрового коррелятора, четвертая функциональная зона 17 представляет собой функциональную зону вычислителя, а пятая функциональная зона 18 - функциональную зону преобразователя интерфейса.

Конкретное послойное выполнение проводников, земляных плоскостей и плоскостей питания в плате приемника-процессора 2 в рамках настоящей заявки не рассматривается как не относящееся к сущности заявляемого изобретения. В частном случае в качестве платы приемника-процессора 2 может использоваться плата приемника-процессора, описанная в [8].

Буферные узлы 8, 9 и 10 обеспечивают согласование входных характеристик платы приемника-процессора 2 с выходными характеристиками тракта, по которому осуществляется поступление внешнего синхронизирующего опорного сигнала от внешнего опорного генератора, и получение из внешнего синхронизирующего опорного сигнала взаимно развязанных друг от друга синхронизирующего опорного сигнала для платы приемника-процессора 2 и дублирующего его опорного сигнала. При этом первый буферный узел 8 служит для получения из внешнего синхронизирующего опорного сигнала промежуточного опорного сигнала, второй буферный узел 9 служит для получения из промежуточного опорного сигнала синхронизирующего опорного сигнала для платы приемника-процессора 2, а третий буферный узел 10 служит для получения из промежуточного опорного сигнала дублирующего опорного сигнала.

Буферные узлы 8, 9, 10 связаны между собой по Y-образной схеме с соединением выходного сигнального контакта 19 первого буферного узла 8 с входными сигнальными контактами 20 и 21 второго 9 и третьего 10 буферных узлов посредством выполненных на лицевой стороне несущей печатной платы 1 первого 22 и второго 23 проводников связи буферных узлов (фиг.2, 4).

Буферные узлы 8, 9, 10 могут быть реализованы, например, в виде усилителей с отрицательной обратной связью, коэффициенты усиления которых, а также характеристики входных и выходных сопротивлений выбраны таким образом, что обеспечивается согласование входных характеристик платы приемника-процессора 2 с выходными характеристиками тракта, по которому осуществляется поступление внешнего синхронизирующего опорного сигнала от внешнего опорного генератора (например, синусоидального сигнала фиксированной частоты, лежащей в диапазоне частот от 5 до 10 МГц), и получение из внешнего синхронизирующего опорного сигнала необходимого синхронизирующего опорного сигнала для платы приемника-процессора 2 и дублирующего его опорного сигнала.

Источник внутриблочного питания 11 служит для формирования из внешнего напряжения питания, поступающего на несущую печатную плату 1 через низкочастотный соединитель 12, внутриблочных напряжений питания для буферных узлов 8, 9, 10 и платы приемника-процессора 2. Внутриблочное напряжение питания для буферных узлов 8, 9, 10 формируется на паре контактов 24 и 25 “Питание буферных узлов” - “Земля питания буферных узлов”, а напряжение питания для платы приемника-процессора 2 - на паре контактов 26 и 27 “Питание платы приемника-процессора” - “Земля питания платы приемника-процессора”.

В рассматриваемом примере источник внутриблочного питания 11 выполнен в виде последовательно соединенных входного фильтра питания 28, первого 29 и второго 30 преобразователей-стабилизаторов напряжения (фиг.4). При этом выходные контакты первого преобразователя-стабилизатора напряжения 29, соединенные с входными контактами второго преобразователя-стабилизатора напряжения 30, образуют пару контактов 24 и 25 “Питание буферных узлов” - “Земля питания буферных узлов”, а выходные контакты второго преобразователя-стабилизатора напряжения 30 образуют пару контактов 26 и 27 “Питание платы приемника-процессора” - “Земля питания платы приемника-процессора”.

Входной фильтр питания 28 служит для фильтрации поступающего на несущую печатную плату 1 внешнего напряжения питания от высокочастотных пульсаций. В рассматриваемом примере он выполнен в виде четырехполюсника, в продольных плечах которого включены индуктивные компоненты, имеющие общую индуктивную связь, а в поперечных - соединенные с ними емкостные компоненты, причем один из двух выходных выводов четырехполюсника является потенциальным выводом входного фильтра питания 28, а другой - его земляным выводом (фиг.4).

Первый преобразователь-стабилизатор напряжения 29 служит для формирования из отфильтрованного внешнего напряжения питания, например 27 В, внутриблочного напряжения питания первого уровня, например 5 В, для питания буферных устройств 8, 9 и 10. Это напряжение формируется на паре контактов 24 и 25 “Питание буферных узлов” - “Земля питания буферных узлов”. В качестве преобразователя-стабилизатора 29 может использоваться, например, малогабаритный преобразователь-стабилизатор напряжения типа МПН6-5 БЕЖК. 43 6431.007-01 ТУ.

Второй преобразователь-стабилизатор напряжения 30 служит для формирования из внутриблочного напряжения питания первого уровня (5 В) внутриблочного напряжения питания второго уровня, например 3,3 В, для питания платы приемника-процессора 2. Это напряжение формируется на паре контактов 26 и 27 “Питание платы приемника-процессора” - “Земля питания платы приемника-процессора”. Преобразователь-стабилизатор напряжения 30 может быть реализован, например, на микросхеме “DC-DC Converters” типа MAX604ESA фирмы “MAXIM” [11].

С контактами 24 “Питание буферных узлов” и 25 “Земля питания буферных узлов” соединены проводники цепи питания буферных узлов, служащие для раздельного подвода к буферным узлам 8, 9, 10 напряжения питания первого уровня (5 В). Так, с контактом 24 “Питание буферных узлов” соединены первые концы расположенных на лицевой стороне несущей печатной платы 1 первого 31, второго 32 и третьего 33 проводников питания цепи питания буферных узлов 8, 9, 10 (фиг.2), а с контактом 25 “Земля питания буферных узлов” соединен первый конец расположенного на тыльной стороне несущей печатной платы 1 общего земляного проводника 34 цепи питания буферных узлов 8, 9, 10 (фиг.3).

С контактами 26 “Питание платы приемника-процессора” и 27 “Земля питания платы приемника-процессора” соединены соответственно проводник питания 35 и земляной проводник 36 цепи питания платы приемника-процессора 2, связывающие контакты 26 и 27 с соответствующими выводами внутриблочного соединителя 7. В рассматриваемом примере проводники 35 и 36 оба выполнены на лицевой стороне несущей печатной платы 1 (фиг.2). Проводники 35 и 36 обеспечивают подвод к соответствующим выводам внутриблочного соединителя 7 внутриблочного напряжения питания второго уровня (3,3 В) от источника внутриблочного питания 11, которое затем через низкочастотный соединитель 6 поступает на плату приемника-процессора 2.

Электрорадиоэлементы, образующие первый 8, второй 9 и третий 10 буферные узлы, сгруппированы в трех граничащих друг с другом экранируемых зонах, окруженных по своим периметрам экранирующими проводниками - на лицевой стороне несущей печатной платы 1 экранирующими проводниками 37 (фиг.2), а на ее тыльной стороне экранирующими проводниками 38 (фиг.3). Экранирующие проводники 37 и 38 выполнены друг под другом, соединены между собой с помощью металлизированных соединительных отверстий (на фиг.1-4 не показаны) и имеют разрывы для прохождения проводников, пересекающих границы экранируемых зон. Экранирующие проводники 37 и 38 выполняют функцию плоскостных экранирующих барьеров, обеспечивающих внутриблочную защиту от паразитных наводок и наведенных помех.

В дополнение к экранирующим проводникам 37 и 38 на тыльной стороне несущей печатной платы 1 внутри экранируемых зон выполнены земляные участки 39, 40 и 41, относящиеся соответственно к буферным узлам 8, 9 и 10 (фиг.3). Земляные участки 39, 40, 41 обеспечивают подвод напряжения питания потенциала “Земля” к буферным узлам 8, 9, 10 и одновременно выполняют функцию плоскостных экранов, обеспечивающих дополнительную внутриблочную защиту от паразитных наводок и наведенных помех.

К земляному участку 39, относящемуся к первому буферному узлу 8, присоединен второй конец общего земляного проводника 34 цепи питания буферных узлов 8, 9, 10 (фиг.3). Кроме этого, земляной участок 39 соединен с земляными участками 40 и 41, относящимися к второму 9 и третьему 10 буферным узлам, посредством первой 42 и второй 43 земляных перемычек, расположенных в соответствии с расположением на лицевой стороне несущей печатной платы 1 первого 22 и второго 23 проводников связи буферных узлов 8, 9, 10 (фиг.2, 3). Земляной проводник 34 и земляные перемычки 42 и 43 пересекают границы экранируемых зон через соответствующие разрывы в экранирующих проводниках 38 (фиг.3).

Экранирующие проводники 37 и 38, помимо соединения между собой металлизированными соединительными отверстиями, соединены также с контактом 25 “Земля питания буферных узлов”. Это соединение осуществлено посредством отдельного земляного проводника 44, расположенного на тыльной стороне несущей печатной платы 1 (фиг.3).

Внутри первой экранируемой зоны - зоны первого буферного узла 8 - на лицевой стороне несущей печатной платы 1 помимо рассмотренного выше выходного сигнального контакта 19 первого буферного узла 8 размещены также его входные сигнальный 45 и земляной 46 контакты (фиг.1, 2). Контакты 45 и 46 служат для присоединения к ним соответственно центральной жилы и экранирующей оплетки коаксиального кабеля 47 (фиг.1), предназначенного для подвода к первому буферному узлу 8 внешнего синхронизирующего опорного сигнала от внешнего опорного генератора (на фиг.1-4 не показан). В рассматриваемом примере коаксиальный кабель 47 оснащен соединителем 48, обеспечивающим возможность присоединения к нему внешнего опорного генератора. Внутри первой экранируемой зоны на лицевой стороне несущей печатной платы 1 также размещен контакт питания 49 первого буферного узла 8, к которому присоединен второй конец первого проводника питания 31 цепи питания буферных узлов 8, 9, 10 (фиг.2, 4).

Внутри второй экранируемой зоны - зоны второго буферного узла 9 - на лицевой стороне несущей печатной платы 1 помимо рассмотренного выше входного сигнального контакта 20 второго буферного узла 9 размещены также его выходные сигнальный 50 и земляной 51 контакты (фиг.1, 2). К контактам 50 и 51 присоединены соответственно центральная жила и экранирующая оплетка коаксиального кабеля 52 (фиг.1), связывающего плату приемника-процессора 2 с вторым буферным узлом 9. Эта связь осуществлена через второй высокочастотный соединитель 5 платы приемника-процессора 2 и соединенный с ним кабельный соединитель 53, смонтированный на коаксиальном кабеле 52. Внутри второй экранируемой зоны на лицевой стороне несущей печатной платы 1 также размещен контакт питания 54 второго буферного узла 9, к которому присоединен второй конец второго проводника питания 32 цепи питания буферных узлов 8, 9, 10 (фиг.2, 4).

Внутри третьей экранируемой зоны - зоны третьего буферного узла 10 - на лицевой стороне несущей печатной платы 1 помимо рассмотренного выше входного сигнального контакта 21 третьего буферного узла 10 размещены также его выходные сигнальный 55 и земляной 56 контакты (фиг.1, 2). Контакты 55 и 56 служат для присоединения к ним соответственно центральной жилы и экранирующей оплетки коаксиального кабеля 57 (фиг.1), предназначенного для отвода дублирующего опорного сигнала от третьего буферного узла 10. В рассматриваемом примере коаксиальный кабель 57 оснащен соединителем 58, обеспечивающим возможность присоединения к нему соответствующих внешних устройств, использующих дублирующий опорный сигнал. Внутри третьей экранируемой зоны на лицевой стороне несущей печатной платы 1 также размещен контакт питания 59 третьего буферного узла 10, к которому присоединен второй конец третьего проводника питания 33 цепи питания буферных узлов 8, 9, 10 (фиг.2, 4).

Проводники питания 31, 32, 33, а также рассмотренные выше проводники связи 22, 23 буферных узлов 8, 9, 10 пересекают границы экранирующих зон через соответствующие разрывы в экранирующих проводниках 37 (фиг.2).

Рассмотренный комплекс конструктивных мер, включающий размещение буферных узлов 8, 9, 10 в трех граничащих друг с другом экранируемых зонах, экранировку этих зон с помощью экранирующих проводников 37, 38 и земляных участков 39, 40, 41 с раздельным подсоединением их с помощью проводников 44 и 34 к контакту 25 “Земля питания буферных узлов”, а также применение раздельного питания для каждого из буферных узлов 8, 9, 10 и платы приемника-процессора 2 с помощью системы проводников 31-34 и 35-36 обеспечивает решение технической проблемы электромагнитной совместимости платы приемника-процессора 2, источника внутриблочного питания 11 и буферных узлов 8, 9, 10 (устранение паразитных наводок и наведенных помех) в условиях их компактного размещения на общей несущей печатной плате 1.

Работа с заявляемым блоком начинается с подключения к нему необходи