Устройство для ввода изображения в эвм

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано в системах технического зрения для ввода информации в ЭВМ. Техническим результатом является повышение скорости ввода изображения в ЭВМ. Этот результат достигается за счет того, что устройство для ввода изображения в ЭВМ содержит АЦП, блок управления, регистр приема, блок буферной памяти, счетчик адреса, первый и второй блоки канальных передатчиков, блок связи с ЭВМ, усилитель, генератор импульсов, формирователь управляющих сигналов, второй регистр приема, второй блок буферной памяти, первый, второй и третий буферные регистры, регистр приема-передачи, счетчик строк, сумматор, счетчик первой строки и цифровой компаратор. 1 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано в системах технического зрения для ввода информации в ЭВМ.

Известно устройство для ввода изображения в ЭВМ (А.С. № 1432494 СССР, кл. G 06 F 3/00, 1988 г., Бюл. № 39), содержащее регистр сдвига, блок управления, счетчик бит, регистр приема, счетчик адреса, формирователь импульсов, блок буферной памяти, блок канальных приемопередатчиков, блок связи с ЭВМ.

Недостатком этого устройства является невысокое быстродействие, т.к. для ввода изображения в ЭВМ необходимо передавать устройству адрес каждого вводимого элемента изображения.

Наиболее близким к предлагаемому является устройство для ввода изображения в ЭВМ (Пат. № 2166790 РФ, кл. 7 G 06 F 3/00, 2000 г., Бюл. № 13), содержащее блок управления, регистр приема, блок буферной памяти, счетчик адреса, блок связи с ЭВМ, АЦП, первый и второй блоки канальных передатчиков.

Недостатком этого устройства является невысокое быстродействие.

Технической задачей устройства является повышение скорости ввода изображения в ЭВМ.

Техническая задача решается тем, что в устройство для ввода изображения в ЭВМ, содержащее АЦП, блок управления, регистр приема, блок буферной памяти, счетчик адреса, первый и второй блоки канальных передатчиков, блок связи с ЭВМ, введены усилитель, генератор импульсов, формирователь управляющих сигналов (ФУС), второй регистр приема, второй блок буферной памяти, первый, второй и третий буферные регистры, регистр приема-передачи, счетчик строк, сумматор, счетчик первой строки и цифровой компаратор, причем информационный выход телекамеры подключен ко входу усилителя, выход которого соединен со входом АЦП и с входом формирователя управляющих сигналов (ФУС), первая группа выходов которого соединена с первой группой входов блока управления, первый выход ФУС подключен к третьему входу регистра приема-передачи и к первому входу блока управления (БУ), а второй выход ФУС соединен со вторым входом счетчика первой строки, выход АЦП соединен с первым входом регистра приема-передачи, второй вход которого соединен с выходом генератора импульсов (ГИ) и с седьмым входом блока управления (БУ), восьмиразрядный выход регистра приема-передачи подключен ко входам данных первого и второго регистров приема, первый управляющий вход первого регистра приема соединен с первым управляющим входом первого блока буферной памяти и первым выходом третьей группы выходов БУ, второй управляющий вход первого регистра приема соединен с первым управляющим входом второго регистра приема и вторым выходом третьей группы выходов БУ, второй управляющий вход второго регистра приема соединен с первым управляющим входом второго блока буферной памяти и третьим выходом третьей группы выходов БУ, информационные выходы первого регистра приема подключены к информационным входам-выходам первого блока буферной памяти и информационным входам первого блока канальных передатчиков, информационные выходы которого вместе с информационными выходами второго блока канальных передатчиков являются группой выходов устройства для подключения к информационной шине ЭВМ, информационные выходы второго регистра приема подключены к информационным входам-выходам второго блока буферной памяти и информационным входам второго блока канальных передатчиков, управляющий вход первого и второго блоков канальных передатчиков подключен к первому выходу первой группы выходов БУ, вторые управляющие входы первого и второго блоков буферной памяти соединены со вторым выходом первой группы выходов БУ, третий выход первой группы выходов БУ соединен со входом разрешения выдачи информации третьего буферного регистра, информационные выходы которого объединены с информационными выходами первого буферного регистра и подключены к информационным входам-выходам первого и второго блоков буферной памяти, информационные входы третьего буферного регистра соединены с информационными выходами счетчика строк, первый вход которого подключен к шестому выходу второй группы выходов БУ, а второй вход счетчика строк подключен к пятому выходу второй группы выходов БУ, первый выход второй группы выходов БУ соединен со вторым входом счетчика длины строки, первый вход которого связан со вторым выходом второй группы выходов БУ, а информационные выходы счетчика длины строки подключены ко второй группе входов цифрового компаратора, выход которого связан с восьмым входом БУ, третий выход второй группы выходов БУ соединен со входом разрешения выдачи информации первого буферного регистра, четвертый выход второй группы выходов БУ соединен с первым входом счетчика первой строки, выходы которого подсоединены к первой группе входов сумматора, к информационным входам первого буферного регистра и к первой группе входов цифрового компаратора, кроме того, первый, второй и третий выходы четвертой группы выходов БУ соединены соответственно с первым, вторым и третьим входами счетчика адреса, выходы которого подключены к адресным входам первого и второго блоков буферной памяти и ко второй группе входов сумматора, выходы которого соединены с информационными входами второго буферного регистра, управляющий вход которого связан с четвертым выходом четвертой группы выходов БУ, информационные выходы второго буферного регистра подключены к информационным входам счетчика адреса, адресные линии шины ISA соединены с первой группой входов блока связи с ЭВМ, первый, второй и третий выходы которого связаны соответственно с первым, вторым и третьим входами второй группы входов БУ, управляющие линии шины ISA, а именно RESET, AEN, Т/С, IOR и DACK, подключены соответственно к шестому, пятому, четвертому, третьему и второму входам БУ, шестой вход БУ соединен также с третьим входом счетчика первой строки, а пятый вход БУ также связан с первым входом блока связи с ЭВМ, первый выход БУ соединен с управляющей линией DRQ шины ISA.

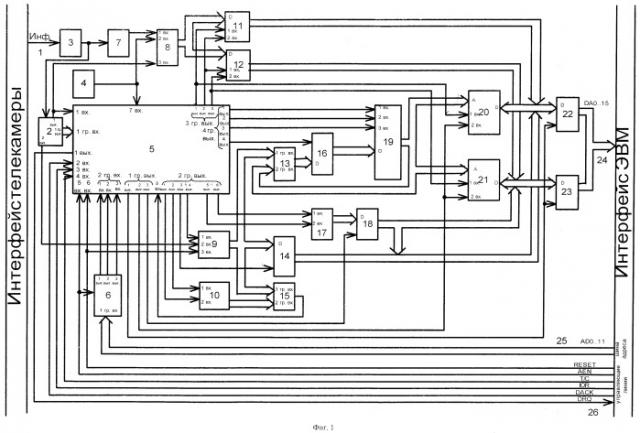

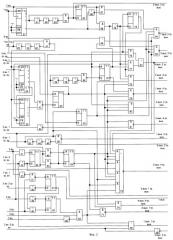

Сущность изобретения поясняется чертежами, где на фиг.1 представлена структурная схема устройства для ввода изображения в ЭВМ, а на фиг. 2 представлена схема блока управления.

Устройство для ввода изображения в ЭВМ содержит информационный вход 1, формирователь управляющих сигналов 2, усилитель 3, генератор импульсов 4, блок управления 5, блок связи с ЭВМ 6, АЦП 7, регистр приема-передачи 8, счетчик первой строки 9, счетчик длины строки 10, первый и второй регистры приема 11 и 12, сумматор 13, первый, второй и третий буферные регистры 14, 16 и 18, цифровой компаратор 15, счетчик строк 17, счетчик адреса 19, первый и второй блоки буферной памяти 20 и 21, первый и второй блоки канальных передатчиков 22 и 23, шину данных 24, адресную шину 25, шину управляющих сигналов 26, причем информационный выход телекамеры 1 подключен ко входу усилителя 3, выход которого соединен со входом АЦП 7 и с входом формирователя управляющих сигналов (ФУС) 2, первая группа выходов которого соединена с первой группой входов блока управления 5, первый выход ФУС 2 подключен к третьему входу регистра приема-передачи 8 и к первому входу блока управления (БУ) 5, а второй выход ФУС 2 соединен со вторым входом счетчика первой строки 9, выход АЦП 7 соединен с первым входом регистра приема-передачи 8, второй вход которого соединен с выходом генератора импульсов (ГИ) 4 и с седьмым входом блока управления (БУ) 5, восьмиразрядный выход регистра приема-передачи 8 подключен ко входам данных первого и второго регистров приема 11 и 12, первый управляющий вход первого регистра приема 11 соединен с первым управляющим входом первого блока буферной памяти 20 и первым выходом третьей группы выходов БУ 5, второй управляющий вход первого регистра приема 11 соединен с первым управляющим входом второго регистра приема 12 и вторым выходом третьей группы выходов БУ 5, второй управляющий вход второго регистра приема 12 соединен с первым управляющим входом второго блока буферной памяти 21 и третьим выходом третьей группы выходов БУ 5, информационные выходы первого регистра приема 11 подключены к информационным входам-выходам первого блока буферной памяти 20 и информационным входам первого блока канальных передатчиков 22, информационные выходы которого вместе с информационными выходами второго блока канальных передатчиков 23 являются группой выходов устройства для подключения к информационной шине ЭВМ 24, информационные выходы второго регистра приема 12 подключены к информационным входам-выходам второго блока буферной памяти 21 и информационным входам второго блока канальных передатчиков 23, управляющий вход первого и второго блоков канальных передатчиков 22 и 23 подключен к первому выходу первой группы выходов БУ 5, вторые управляющие входы первого и второго блоков буферной памяти 20 и 21 соединены со вторым выходом первой группы выходов БУ 5, третий выход первой группы выходов БУ 5 соединен со входом разрешения выдачи информации третьего буферного регистра 18, информационные выходы которого объединены с информационными выходами первого буферного регистра 14 и подключены к информационным входам-выходам первого и второго блоков буферной памяти 20 и 21, информационные входы третьего буферного регистра 18 соединены с информационными выходами счетчика строк 17, первый вход которого подключен к шестому выходу второй группы выходов БУ 5, а второй вход счетчика строк 17 подключен к пятому выходу второй группы выходов БУ 5, первый выход второй группы выходов БУ 5 соединен со вторым входом счетчика длины строки 10, первый вход которого связан со вторым выходом второй группы выходов БУ 5, а информационные выходы счетчика длины строки 10 подключены ко второй группе входов цифрового компаратора 15, выход которого связан с восьмым входом БУ 5, третий выход второй группы выходов БУ 5 соединен со входом разрешения выдачи информации первого буферного регистра 14, четвертый выход второй группы выходов БУ 5 соединен с первым входом счетчика первой строки 9, выходы которого подсоединены к первой группе входов сумматора 13, к информационным входам первого буферного регистра 14 и к первой группе входов цифрового компаратора 15, первый, второй и третий выходы четвертой группы выходов БУ 5 соединены соответственно с первым, вторым и третьим входами счетчика адреса 19, выходы которого подключены к адресным входам первого и второго блоков буферной памяти 20 и 21 и ко второй группе входов сумматора 13, выходы которого соединены с информационными входами второго буферного регистра 16, управляющий вход которого связан с четвертым выходом четвертой группы выходов БУ 5, информационные выходы второго буферного регистра 16 подключены к информационным входам счетчика адреса 19, адресные линии шины ISA 25 соединены с первой группой входов блока связи с ЭВМ 6, первый, второй и третий выходы которого связаны соответственно с первым, вторым и третьим входами второй группы входов БУ 5, управляющие линии шины ISA 26, а именно RESET, AEN, Т/С, IOR и DACK, подключены соответственно к шестому, пятому, четвертому, третьему и второму входам БУ 5, шестой вход БУ 5 соединен также с третьим входом счетчика первой строки 9, а пятый вход БУ 5 также связан с первым входом блока связи с ЭВМ 6, первый выход БУ 5 соединен с управляющей линией DRQ шины ISA 26.

Формирователь управляющих сигналов 2 предназначен для формирования управляющих сигналов. Из сигнала, поступающего от видеокамеры, ФУС выделяет кадровый, строчный импульсы, их инверсию, полукадровый импульс и его инверсию, импульс начала нечетного кадра, импульс середины кадра и второй строчный импульс, но меньшей длительности. Все эти импульсы подаются на БУ 5.

Усилитель 3 обеспечивает амплитуду видеосигнала, необходимую для нормальной работы АЦП 7 и ФУС 2.

Генератор импульсов 4 формирует последовательность импульсов с частотой 7 МГц.

Блок управления 5 предназначен для управления приемом или передачей одного кадра телевизионного изображения в ЭВМ. Блок управления содержит первый 27, второй 29 и третий 30 счетчики, первый 28, второй 32, третий 33, четвертый 34, пятый 35, шестой 38, седьмой 39, восьмой 41, девятый 42, десятый 44, одиннадцатый 45, двенадцатый 46, тринадцатый 48, четырнадцатый 53, пятнадцатый 54, шестнадцатый 58, семнадцатый 60, восемнадцатый 61, девятнадцатый 66, двадцатый 72 и двадцать первый 86 элементы НЕ, первый 31, второй 40, третий 69, четвертый 82 и пятый 83 элементы ИЛИ, первый 36, второй 51, третий 52, четвертый 55, пятый 59, шестой 62, седьмой 63, восьмой 70 и девятый 75 триггеры, первый 37, второй 43, третий 47, четвертый 49, пятый 50, шестой 56, седьмой 57, восьмой 65, девятый 71, десятый 79, одиннадцатый 81, двенадцатый 84 и тринадцатый 85 элементы И-НЕ, первый 64, второй 67, третий 68, четвертый 74, пятый 76, шестой 77, седьмой 78 и восьмой 80 элементы И, элемент И-ИЛИ-НЕ 73, ПРИЧЕМ вход С первого счетчика 27 объединен со входом сброса шестого триггера 62 и является седьмым входом БУ, а вход SR первого счетчика 27 объединен со входом установки седьмого триггера 63, на входы СЕР, РЕ, СЕТ первого и второго счетчиков 27 и 29, входы РЕ и СЕТ третьего счетчика 30 подана логическая единица, выход 2 первого счетчика 27 объединен со входом восьмого элемента НЕ 41 и подключен к первому входу седьмого элемента И-НЕ 57, выход восьмого элемента НЕ 41 подключен ко входу двенадцатого элемента НЕ 46, выход которого подключен ко входу четырнадцатого элемента НЕ 53, чей выход подключен ко второму входу седьмого элемента И-НЕ 57, выход которого является вторым выходом третьей группы выходов БУ 5 и подключен ко входу установки шестого триггера 62, чей прямой выход соединен с первыми входами второго 67 и третьего 68 элементов И, второй вход второго элемента И 67 соединен с выходом девятнадцатого элемента НЕ 66, вход которого, объединенный со вторым входом третьего элемента И 68, подключен к выходу 3 первого счетчика 27, выход второго элемента И 67 соединен с первым входом двенадцатого элемента И-НЕ 84, выход третьего элемента И 68 подключен к первому входу тринадцатого элемента И-НЕ 85 и ко входу двадцатого элемента НЕ 72, выход которого соединен со входом установки девятого триггера 75, вторым входом шестого элемента И 77 и вторым входом седьмого элемента И 78, прямой выход девятого триггера 75 подключен к четвертому входу шестого элемента И 77 и первому входу седьмого элемента И 78, вход первого элемента НЕ 28 объединен с первым входом третьего элемента И-НЕ 47 и является первым входом первой группы входов БУ, выход первого элемента НЕ 28 соединен со входом четвертого элемента НЕ 34, выход которого соединен со входом девятого элемента НЕ 42, чей выход соединен со вторым входом третьего элемента И-НЕ 47, выход которого объединен со входами сброса SR второго 29 и третьего 30 счетчиков и подключен ко входу десятого элемента НЕ 44, выход которого соединен со вторым входом одиннадцатого элемента И-НЕ 81, выход СТ второго счетчика 29 подключен ко входу СЕР третьего счетчика 30, выход 0 которого вместе с выходом 3 второго счетчика 29 являются соответственно вторым и первым входами второго элемента И-НЕ 43, чей выход подключен ко входу установки четвертого триггера 55, прямой выход которого является входом пятнадцатого элемента НЕ 54, первым входом восьмого элемента И-НЕ 65, четвертым входом седьмого элемента И 78, вторым входом десятого элемента И-НЕ 79, вторым входом восьмого элемента И 80, четвертым входом первого элемента И элемента И-ИЛИ-НЕ 73, вторым входом в третьем элементе И элемента И-ИЛИ-НЕ 73, выход пятнадцатого элемента НЕ 54 является входом шестнадцатого элемента НЕ 58, выход которого подключен ко входу восемнадцатого элемента НЕ 61, чей выход соединен со вторым входом восьмого элемента И-НЕ 65, выход которого подключен ко входу установки восьмого триггера 70, вход сброса которого объединен со входом сброса девятого триггера 75 и входами синхронизации второго 29 и третьего 30 счетчиков, первыми входами пятого 76 и восьмого 80 элементов И и является четвертым входом первой группы входов БУ 5, прямой выход восьмого триггера 70 подключен к третьему входу шестого элемента И 77 и ко второму входу третьего элемента ИЛИ 69, выход которого соединен с четвертым входом двенадцатого элемента И-НЕ 84, с четвертым входом тринадцатого элемента И-НЕ 85 и вторым входом первого элемента И элемента И-ИЛИ-НЕ 73, инверсный выход восьмого триггера 70 подключен к первому входу десятого элемента И-НЕ 79, вход пятого элемента НЕ 35 является шестым входом первой группы входов БУ 5 и объединен с первым входом шестого элемента И-НЕ 56, третьим входом третьего элемента И элемента И-ИЛИ-НЕ 73, первым входом четвертого элемента И 74 и со входом сброса седьмого триггера 63, прямой выход которого подключен к третьему входу седьмого элемента И 78, к третьему входу двенадцатого элемента И-НЕ 84 и третьему входу тринадцатого элемента И-НЕ 85, выход пятого элемента НЕ 35 соединен со входом одиннадцатого элемента НЕ 45, выход которого является входом тринадцатого элемента НЕ 48, чей выход является вторым входом шестого элемента И-НЕ 56, выход которого является первым выходом второй группы выходов БУ 5, первый вход первого элемента ИЛИ 31 объединен со входом третьего элемента НЕ 33 и является шестым входом БУ 5, второй вход первого элемента ИЛИ 31 объединен со входом седьмого элемента НЕ 39 и является четвертым входом БУ 5, выход первого элемента ИЛИ 31 подключен ко входу сброса первого триггера 36, установочный вход которого соединен с выходом второго элемента НЕ 32 и является третьим выходом первой группы выходов БУ 5, прямой выход первого триггера 36 подключен к первому входу четвертого элемента И-НЕ 49, второй вход которого объединен с первым входом пятого элемента И-НЕ 50, со вторым входом пятого элемента И 76 и является пятым входом первой группы входов БУ 5, выход четвертого элемента И-НЕ 49 является входом сброса пятого триггера 59, инверсный выход первого триггера 36 подключен ко второму входу пятого элемента И-НЕ 50, выход которого является пятым выходом второй группы выходов БУ 5, а также входом установки пятого триггера 59, прямой выход которого подключен к третьему входу девятого элемента И-НЕ 79, ко второму входу двенадцатого элемента И-HE 84, ко второму входу тринадцатого элемента И-НЕ 85, к третьему входу восьмого элемента И 80, к первому входу одиннадцатого элемента И-НЕ 81, третьему входу первого элемента И элемента И-ИЛИ-НЕ 73, первому входу второго элемента И элемента И-ИЛИ-НЕ 73, первому входу третьего элемента И элемента И-ИЛИ-НЕ 73, кроме того, инверсный выход пятого триггера 59 соединен с первым входом четвертого элемента И элемента И-ИЛИ-НЕ 73 и с первым входом девятого элемента И-НЕ 71, выход третьего элемента НЕ 33 соединен с первым входом первого элемента И-НЕ 37, второй вход которого является вторым входом БУ 5 и объединен со вторым входом второго элемента ИЛИ 40, а выход является входом сброса второго триггера 51, вход установки которого соединен с выходом шестого элемента НЕ 38, инверсный выход второго триггера 51 подключен к первому входу второго элемента ИЛИ 40, выход которого является входом установки третьего триггера 52, входом сброса которого является выход седьмого элемента НЕ 39, прямой выход третьего триггера 52 соединен с первым входом первого элемента И 64, третий вход которого соединен с выходом семнадцатого элемента НЕ 60, выход первого элемента И 64 подключен ко второму входу четвертого элемента И элемента И-ИЛИ-НЕ 73, ко второму входу девятого элемента И-НЕ 71 и к первому входу четвертого элемента ИЛИ 82, второй вход которого объединен со входом второго элемента НЕ 32 и является первым входом второй группы входов БУ 5, третий вход четвертого элемента ИЛИ 82 объединен со входом двадцать первого элемента НЕ 86 и является вторым входом второй группы входов БУ 5, выходы пятого 76 и шестого 77 элементов И являются соответственно первым и вторым входами пятого элемента ИЛИ 83, выход которого подключен к первому входу первого элемента И элемента И-ИЛИ-НЕ 73 и является четвертым выходом второй группы выходов БУ 5, кроме того, вход семнадцатого элемента НЕ 60 является третьим входом БУ 5, второй вход первого элемента И 64 является пятым входом БУ 5, первый вход третьего элемента ИЛИ 69 является восьмым входом БУ 5, вход сброса четвертого триггера 55 является вторым входом первой группы входов БУ 5, первый вход шестого элемента И 77 является третьим входом первой группы входов БУ 5, второй вход второго элемента И элемента И-ИЛИ-НЕ 73 является седьмым входом первой группы входов БУ 5, вход шестого элемента НЕ 38 является третьим входом второй группы входов БУ 5, прямой выход второго триггера 51 является первым выходом БУ 5, выход четвертого элемента ИЛИ 82 и выход девятого элемента И-НЕ 71 являются соответственно первым и вторым выходами первой группы выходов БУ 5, выход седьмого элемента И 78, выход двадцать первого элемента НЕ 86 и выход восьмого элемента И 80 являются соответственно вторым, третьим и шестым выходами второй группы выходов БУ 5, выход двенадцатого элемента И-НЕ 84 и выход тринадцатого элемента И-НЕ 85 являются соответственно первым и третьим выходами третьей группы выходов БУ 5, выход десятого элемента И-НЕ 79, выход одиннадцатого элемента И-НЕ 81, выход элемента И-ИЛИ-НЕ 73 и выход четвертого элемента И 74 являются соответственно первым, вторым, третьим и четвертым выходами четвертой группы выходов БУ 5.

Блок связи с ЭВМ 6 предназначен для организации обмена информации устройства для ввода изображения в ЭВМ с ЭВМ, его функцией является дешифрация адреса.

АЦП 7 представляет собой одноразрядный аналого-цифровой преобразователь и предназначен для преобразования аналогового видеосигнала, поступающего с усилителя 3, в цифровой двоичный код.

Регистр приема-передачи 8 предназначен для формирования параллельного восьмиразрядного кода из последовательности сигналов, получаемой с АЦП 7.

Счетчик первой строки 9 считает количество байт первой строки нечетного полукадра.

Счетчик длины строки 10 предназначен для подсчета количества байт в каждой строке, кроме первой строки нечетного полукадра.

Регистры приема 11 и 12 предназначены для приема поступающего восьмиразрядного кода и последующей передачи его в первый 20 и второй 21 блоки буферной памяти.

Сумматор 13, буферный регистр 16, счетчик адреса 19 предназначены для формирования адресов ОЗУ (блоки буферной памяти 20 и 21), при котором данные нечетных полукадров записываются в нечетные строки ОЗУ, а четных - в четные.

Буферные регистры 14, 18 предназначены для формирования задержек данных и адресов.

Цифровой компаратор 15 предназначен для сравнения длины первой строки изображения с длиной последующих строк.

Счетчик строк 17 предназначен для подсчета количества записанных в блоки буферной памяти 20 и 21 строк кадра изображения. Первый вход счетчика строк 17 является счетным входом, а второй вход счетчика строк 17 является входом сброса.

Блоки буферной памяти 20 и 21 (ОЗУ) предназначены для запоминания и хранения введенного кадра телевизионного изображения. Блоки являются статическими запоминающими элементами.

Блоки канальных передатчиков 22 и 23 предназначены для передачи информации в канал ЭВМ и состоят из двух восьмиразрядных передатчиков каждый.

Устройство работает следующим образом. Устройство для ввода изображения в ЭВМ работает в двух режимах: ввод информации от телекамеры в блоки буферной памяти 20 и 21 и передача информации в ЭВМ.

Режим ввода информации от телекамеры в блоки буферной памяти 20 и 21.

В этом режиме видеоинформация, принимаемая от телекамеры, поступает в устройство и запоминается в блоках буферной памяти 20 и 21 (ОЗУ). Порядок выполнения операций следующий. После включения питания ЭВМ вырабатывает сигнал RESET, длительность которого по стандарту ISA не менее 1 мс. При появлении сигнала RESET счетчик первой строки 9 сбрасывается в 0 и подготавливает БУ 5 к работе.

Запись данных, полученных с телекамеры, в блоки буферной памяти 20 и 21 начинается с 24-й строки каждого полукадра.

Информационный сигнал от телекамеры усиливается усилителем 3 и поступает на АЦП 7, который преобразовывает этот сигнал в двоичный код и передает в регистр приема-передачи 8. Сигнал, полученный с усилителя 3, поступает также на вход ФУС 2, который выделяет кадровый, строчный импульсы, их инверсию, полукадровый импульс и его инверсию, импульс начала нечетного кадра, импульс середины кадра и второй строчный импульс, но меньшей длительности. Эти сигналы образуют первую группу входов БУ 5. Генератор импульсов 4 генерирует прямоугольные импульсы с частотой 7 МГц, поступающие на второй вход регистра приема-передачи 8 и счетчика 27, на входы СЕР, РЕ, СЕТ которого подана логическая единица. При поступлении этих импульсов содержимое регистра приема-передачи 8 поступает на его выходы. Один импульс соответствует одному биту информации. В начале каждой строки регистр приема-передачи 8 обнуляется. С помощью счетчика 27 происходит подсчет количества импульсов. Каждые восемь импульсов происходит запись содержимого регистра приема-передачи 8 в регистры приема 11 или 12. Происходит запись восьми бит в регистр приема 11, следующих восьми бит - в регистр приема 12 и т.д.

Для записи в блоки буферной памяти строк одной длины в устройстве предусмотрен счетчик первой строки 9, который осуществляет подсчет количества элементов в первой строке. Счетчик длины строки 10 считает количество элементов во всех остальных строках, а цифровой компаратор 15 осуществляет сравнение количества элементов 1-й строки с количеством записанных в блоки буферной памяти 20 и 21 элементов каждой из последующих строк. При равенстве количества элементов 1-й строки и текущей запись прекращается и к текущему значению адреса прибавляется число, хранящееся в счетчике 1-й строки. Таким образом, запись в блоки буферной памяти 20 и 21 элементов следующей строки начинается с адреса, отстоящего от текущего на 1 строку. Запись элементов в следующем полукадре кадра начнется с адреса, следующего за адресом последнего элемента 1-й строки. Таким образом, осуществляется чересстрочная запись полученной информации в блоки буферной памяти 20 и 21.

Счетчик 17 осуществляет подсчет строк, записанных в блоки буферной памяти 20 и 21. При необходимости по шине ISA можно считать содержимое счетчика первой строки 9 по адресу 0361 и содержимое счетчика строк 17 по адресу 0360. При появлении соответствующих адресов блок связи с ЭВМ 6 вырабатывает сигнал, поступающий на второй или первый вход третьей группы входов БУ 5, и БУ 5 подает сигнал, разрешающий выдачу информации буферными регистрами 14 или 18 соответственно.

Режим передачи информации в ЭВМ.

В этом режиме информация, записанная в блоки буферной памяти 20 и 21, считывается ЭВМ при выполнении операции “Ввод”. В адресном пространстве ЭВМ устройство занимает три адреса.

При осуществлении чтения контроллер ПДП ЭВМ формирует адрес ячейки памяти, куда будут считаны данные, и после этого на пятом входе БУ 5 и первом входе блока связи с ЭВМ 6 выставляет сигнал AEN, разрешающий производить обмен. После этого на третьем входе БУ 5 выставляется строб чтения IOR (от ПДП), по которому осуществляется чтение данных из блоков канальных передатчиков 22 и 23 (буферов ОЗУ 22 и 23). Эти данные поступают на ШД ISA.

Для считывания количества элементов в первой строке (во всех остальных строках столько же элементов) ЭВМ выставляет на шину адреса AD0..11 адрес 0361. При появлении этого адреса блок связи с ЭВМ 6 формирует на своем втором выходе сигнал, который поступает на элемент НЕ 86 и элемент ИЛИ 82, тем самым разрешая выдачу данных буферным регистром 14, где содержится количество элементов первой строки, и выдачу данных блоками канальных передатчиков 22 и 23 на ISA шину.

При появлении адреса 0360 блок связи с ЭВМ 6 формирует на своем первом выходе сигнал, который поступает на элемент НЕ 32 и элемент ИЛИ 82. Сигнал после элемента ИЛИ 82 разрешает выдачу данных блоками канальных передатчиков на ISA шину. Сигнал после элемента НЕ 32 разрешает выдачу данных буферным регистром 14, где содержится количество строк, записанных в блоки буферной памяти 20 и 21. Таким образом, на шину ISA выдается информация о количестве строк, содержащихся в блоках буферной памяти 20 и 21. При появлении импульса начала кадра, свидетельствующего о том, что началась оцифровка следующего кадра, на выходе элемента И-НЕ 49 формируется логический 0, который сбрасывает триггер 59. Логическая 1 на инверсном выходе триггера 59 и логическая единица на выходе элемента И 64 формируют на выходе элемента И-НЕ 71 логический 0, который поступает на инверсный вход разрешения чтения блоков буферной памяти 20 и 21.

Если ЭВМ выставляет адрес 0362, то блок связи с ЭВМ 6 формирует на своем 3-м выходе сигнал, который, инвертируясь на элементе НЕ 38, переключает триггер 51 в единичное состояние, тем самым формируя запрос на ПДП на линии DRQ, являющейся первым выходом БУ 5. После освобождения шины ISA (шина может быть занята обменом с другим устройством) текущим задатчиком становится контроллер ПДП ЭВМ. Контроллер ПДП ЭВМ формирует сигнал DACK на втором входе БУ 5, который вместе с логическим 0 на инверсном выходе триггера 51 формирует логический 0 на выходе элемента ИЛИ 40, что позволяет установить триггер 52 в единичное состояние. При ПДП ЭВМ формирует сигнал AEN, отрицательный сигнал IOR, которые поступают на 3-й и 5-й входы БУ 5 соответственно. Таким образом, на входы элемента И 64 поступают логические 1 с выхода триггера 52 и с выхода элемента НЕ 60, а также сигнал AEN. На выходе элемента И 64 при этом формируется логическая 1, которая, поступая на вход элемента И-НЕ 71, формирует логический 0 на его выходе, который поступает на инверсный вход разрешения чтения блоков буферной памяти 20 и 21. Логическая 1 с выхода элемента И 64, проходя через элемент ИЛИ 82, поступает на вход разрешения выдачи данных блоков канальных передатчиков 22 и 23.

По окончании считывания ЭВМ формирует сигнал Т/С, свидетельствующий об окончании передачи и подготавливающий устройство к новому циклу работы.

Таким образом, с введением в устройство усилителя, генератора импульсов, формирователя управляющих сигналов (ФУС), второго регистра приема, второго блока буферной памяти, первого, второго и третьего буферных регистров, регистра приема-передачи, счетчика строк, сумматора, счетчика первой строки и цифрового компаратора повышается скорость ввода изображения в ЭВМ.

1. Устройство для ввода изображения в ЭВМ, содержащее АЦП, блок управления, регистр приема, блок буферной памяти, счетчик адреса, первый и второй блоки канальных передатчиков, блок связи с ЭВМ, отличающееся тем, что в устройство введены усилитель, генератор импульсов, формирователь управляющих сигналов (ФУС), второй регистр приема, второй блок буферной памяти, первый, второй и третий буферные регистры, регистр приема-передачи, счетчик строк, сумматор, счетчик первой строки и цифровой компаратор, причем информационный выход телекамеры подключен ко входу усилителя, выход которого соединен со входом АЦП и с входом формирователя управляющих сигналов (ФУС), первая группа выходов которого соединена с первой группой входов блока управления, первый выход ФУС подключен к третьему входу регистра приема-передачи и к первому входу блока управления (БУ), а второй выход ФУС соединен со вторым входом счетчика первой строки, выход АЦП соединен с первым входом регистра приема-передачи, второй вход которого соединен с выходом генератора импульсов (ГИ) и с седьмым входом блока управления (БУ), восьмиразрядный выход регистра приема-передачи подключен ко входам данных первого и второго регистров приема, первый управляющий вход первого регистра приема соединен с первым управляющим входом первого блока буферной памяти и первым выходом третьей группы выходов БУ, второй управляющий вход первого регистра приема соединен с первым управляющим входом второго регистра приема и вторым выходом третьей группы выходов БУ, второй управляющий вход второго регистра приема соединен с первым управляющим входом второго блока буферной памяти и третьим выходом третьей группы выходов БУ, информационные выходы первого регистра приема подключены к информационным входам-выходам первого блока буферной памяти и информационным входам первого блока канальных передатчиков, информационные выходы которого вместе с информационными выходами второго блока канальных передатчиков являются группой выходов устройства для подключения к информационной шине ЭВМ, информационные выходы второго регистра приема подключены к информационным входам-выходам второго блока буферной памяти и информационным входам второго блока канальных передатчиков, управляющий вход первого и второго блоков канальных передатчиков подключен к первому выходу первой группы выходов БУ, вторые управляющие входы первого и второго блоков буферной памяти соединены со вторым выходом первой группы выходов БУ, третий выход первой группы выходов БУ соединен со входом разрешения выдачи информации третьего буферного регистра, информационные выходы которого объединены с информационными выходами первого буферного регистра и подключены к информационным входам-выходам первого и второго блоков буферной памяти, информационные входы третьего буферного регистра соединены с информационными выходами счетчика строк, первый вход которого подключен к шестому выходу второй группы выходов БУ, а второй вход счетчика строк подключен к пятому выходу второй группы выходов БУ, первый выход второй группы выходов БУ соединен со вторым входом счетчика длины строки, первый вход которого связан со вторым выходом второй группы выходов БУ, а информационные выходы счетчика длины строки подключены ко второй группе входов цифрового компаратора, выход которого связан с восьмым входом БУ, третий выход второй группы выходов БУ соединен со входом разрешения выдачи информации первого буферного регистра, четвертый выход второй группы выходов БУ соединен с первым входом счетчика первой строки, выходы которого подсоединены к первой группе входов сумматора, к информационным входам первого буферного регистра и к первой группе входов цифрового компаратора, первый, второй и третий выходы четвертой группы выходов БУ соединены соответственно с первым, вторым и третьим входами счетчика адреса, выходы которого подключены к адресным входам первого и второго блоков буферной памяти и ко второй группе входов сумматора, выходы которого соединены с информационными входами второго буферного регистра, управляющий вход которого связан с четвертым выходом четвертой группы выходов БУ, информационные выходы второго буферного регистра подключены к информационным входам счетчика адреса, адресные линии шины ISA соединены с первой группой входов блока связи с ЭВМ, первый, второй и третий выходы которого связаны соответственно с первым, вторым и третьим входами второй группы входов БУ, управляющие линии шины ISA, а именно RESET, AEN, Т/С, IOR и DACK подключены соответственно к шестому, пятому, четвертому, третьему и второму входам БУ, шестой вход БУ соединен также с третьим входом счетчика первой строки, а пятый вход БУ также связан с первым входом блока связи с ЭВМ, первый выход БУ соединен с управляющей линией DRQ шины ISA.

2. Устройство по п.1, отличающееся тем, что блок управления содержит первый, второй и третий счетчики, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый, восемнадцатый, девятнадцатый, двадцатый и двадцать первый элементы НЕ, первый, второй, третий, четвертый и пятый элементы ИЛИ, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый триггеры, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый и тринадцатый элементы И-НЕ, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, элемент И-ИЛИ-НЕ, причем вход С первого счетчика объединен со входом сброса шестого триггера и является седьмым входом БУ, а вход SR первого счетчика объединен со входом установки седьмого триггера, на входы СЕР, РЕ, СЕТ первого и второго счетчиков, входы РЕ и СЕТ третьего счетчика подана логическая единица, выход 2 первого счетчика объединен со входом восьмого элемента НЕ и подключен к первому входу седьмого элемента И-НЕ, выход восьмого элемента НЕ подключен ко входу двенадцатого элемента НЕ, выход которого подключен ко входу четырнадцатого элемента НЕ, чей выход подключен ко второму входу седьмого элемента И-НЕ, выход которого является вторым выходом третьей группы выходов БУ и подключен ко входу установки ше