Ячейка однородной отказоустойчивой среды процессорных элементов

Иллюстрации

Показать всеИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих и вычислительных систем высокой производительности, АСУТП, а также других систем, к которым предъявляются жесткие требования по надежности. Техническим результатом является расширение области применения за счет введения технических средств, позволяющих рационально расположить резервные процессорные элементы и соответственно уменьшить число перенастраиваемых процессорных элементов и время реконфигурации. Для этого в ячейку однородной отказоустойчивой среды процессорных элементов дополнительно введены первый и второй блоки адресной селекции минимальной континуальной величины, блок разрешения приема программопереноса, первый и второй блоки демультиплексора, блок определения фатального отказа, блок формирования опорных напряжений, первый, второй, третий и четвертый блоки ранговой селекции, блок выделения сигналов живучести, блок определения минимальной континуальной величины и блок формирования сигналов живучести. 18 ил., 1 табл.

Реферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих и вычислительных систем высокой производительности, АСУТП, а также других систем, к которым предъявляются жесткие требования по надежности.

Известно устройство для перестройки матричной процессорной структуры, содержащее три элемента ИЛИ, два элемента И и один элемент запрета (Сами М., Стефанелли Р. “Перестраиваемые архитектуры матричных процессорных СБИС”// ТИИЭР. - 1986. - 5. - с.107-118).

Недостатком известного устройства является низкое быстродействие и высокий процент ситуаций фатального отказа, для которых перестройка невозможна.

Наиболее близкой к предлагаемому устройству по технической сущности является ячейка однородной отказоустойчивой среды процессорных элементов, содержащая десять элементов ИЛИ, шестнадцать элементов И и пять элементов запрета (патент 2103724 РФ G 06 F 7/00, опубл. 27.01.98, БИ 3).

Недостатком известного устройства является узкая область применения, обусловленная низким быстродействием однородной отказоустойчивой среды из-за фиксированного расположения резервных процессорных элементов в крайнем столбце и соответственно большого числа перенастраиваемых процессорных элементов.

Технической задачей изобретения является расширение области применения за счет введения технических средств, позволяющих рационально расположить резервные процессорные элементы и соответственно уменьшить число перенастраиваемых процессорных элементов и время реконфигурации.

Техническая задача решается тем, что в ячейку однородной отказоустойчивой среды процессорных элементов дополнительно введены первый и второй блоки адресной селекции минимальной континуальной величины, блок разрешения приема программопереноса, первый и второй блоки демультиплексора, блок определения фатального отказа, блок формирования опорных напряжений, первый, второй, третий и четвертый блоки ранговой селекции, блок выделения сигналов живучести, блок определения минимальной континуальной величины и блок формирования сигналов живучести, причем первый вход ячейки соединен с первым входом первого блока адресной селекции минимальной континуальной величины, с пятым входом блока определения минимальной континуальной величины и с первым входом блока формирования сигналов живучести; второй вход ячейки соединен со вторым входом первого блока адресной селекции минимальной континуальной величины, с шестым входом блока определения минимальной континуальной величины и со вторым входом блока формирования сигналов живучести; третий вход ячейки соединен с третьим входом первого блока адресной селекции минимальной континуальной величины, с седьмым входом блока определения минимальной континуальной величины и с третьим входом блока формирования сигналов живучести; четвертый вход ячейки соединен с четвертым входом первого блока адресной селекции минимальной континуальной величины, с восьмым входом блока определения минимальной континуальной величины и с четвертым входом блока формирования сигналов живучести; пятый вход ячейки соединен с четвертым входом блока разрешения приема программопереноса, с первым входом первого блока ранговой селекции и с первым входом блока выделения сигналов живучести; шестой вход ячейки соединен с третьим входом блока разрешения приема программопереноса, с первым входом второго блока ранговой селекции и со вторым входом блока выделения сигналов живучести; седьмой вход ячейки соединен со вторым входом блока разрешения приема программопереноса, с первым входом третьего блока ранговой селекции и с третьим входом блока выделения сигналов живучести; восьмой вход ячейки соединен с первым входом блока разрешения приема программопереноса, с первым входом четвертого блока ранговой селекции и с четвертым входом блока выделения сигналов живучести; девятый вход ячейки соединен с пятым входом блока выделения сигналов живучести; десятый вход ячейки соединен с шестым входом блока выделения сигналов живучести; одиннадцатый вход ячейки соединен с седьмым входом блока выделения сигналов живучести; двенадцатый вход ячейки соединен с восьмым входом блока выделения сигналов живучести; тринадцатый вход ячейки соединен с шестым входом первого блока демультиплексора, с третьим входом блока определения фатального отказа, с третьим входом первого блока ранговой селекции, с третьим входом второго блока ранговой селекции, с третьим входом третьего блока ранговой селекции и с третьим входом четвертого блока ранговой селекции; четырнадцатый вход ячейки соединен с седьмым входом первого блока демультиплексора, с шестым входом второго блока демультиплексора и с четвертым входом блока определения фатального отказа; первый выход первого блока адресной селекции минимальной континуальной величины соединен с первым входом первого блока демультиплексора и с первым входом блока определения минимальной континуальной величины; второй выход первого блока адресной селекции минимальной континуальной величины соединен со вторым входом первого блока демультиплексора и со вторым входом блока определения минимальной континуальной величины; третий выход первого блока адресной селекции минимальной континуальной величины соединен с третьим входом первого блока демультиплексора и с третьим входом блока определения минимальной континуальной величины; четвертый выход первого блока адресной селекции минимальной континуальной величины соединен с четвертым входом первого блока демультиплексора и с четвертым входом блока определения минимальной континуальной величины; первый выход блока формирования опорных напряжений соединен с пятым входом первого блока адресной селекции минимальной континуальной величины, с седьмым входом второго блока демультиплексора, с четвертым входом первого блока ранговой селекции, с четвертым входом второго блока ранговой селекции, с четвертым входом третьего блока ранговой селекции, с четвертым входом четвертого блока ранговой селекции, с пятым входом блока формирования сигналов живучести и с пятым входом второго блока адресной селекции минимальной континуальной величины; первый выход блока разрешения приема программопереноса соединен с пятым входом первого блока демультиплексора, со вторым входом блока определения фатального отказа и с семнадцатым выходом ячейки; первый выход первого блока демультиплексора соединен с первым выходом ячейки; второй выход первого блока демультиплексора соединен со вторым выходом ячейки; третий выход первого блока демультиплексора соединен с третьим выходом ячейки; четвертый выход первого блока демультиплексора соединен с четвертым выходом ячейки; первый выход второго блока демультиплексора соединен с девятым выходом ячейки; второй выход второго блока демультиплексора соединен с десятым выходом ячейки; третий выход второго блока демультиплексора соединен с одиннадцатым выходом ячейки; четвертый выход второго блока демультиплексора соединен с двенадцатым выходом ячейки; первый выход первого блока ранговой селекции соединен с первым входом второго блока демультиплексора; первый выход второго блока ранговой селекции соединен со вторым входом второго блока демультиплексора; первый выход третьего блока ранговой селекции соединен с третьим входом второго блока демультиплексора; первый выход четвертого блока ранговой селекции соединен с четвертым входом второго блока демультиплексора; первый выход блока определения минимальной континуальной величины соединен с пятым входом второго блока демультиплексора и с первым входом блока определения фатального отказа; второй выход блока формирования опорных напряжений соединен с восьмым входом второго блока демультиплексора, с пятым входом блока определения фатального отказа, с девятым входом блока выделения сигналов живучести и с шестым входом блока формирования сигналов живучести; первый выход блока определения фатального отказа соединен с восемнадцатым выходом ячейки; первый выход второго блока адресной селекции минимальной континуальной величины соединен со вторым входом первого блока ранговой селекции и с тринадцатым выходом ячейки; второй выход второго блока адресной селекции минимальной континуальной величины соединен со вторым входом второго блока ранговой селекции и с четырнадцатым выходом ячейки; третий выход второго блока адресной селекции минимальной континуальной величины соединен со вторым входом третьего блока ранговой селекции и с пятнадцатым выходом ячейки; четвертый выход второго блока адресной селекции минимальной континуальной величины соединен со вторым входом четвертого блока ранговой селекции и с шестнадцатым выходом ячейки; первый выход блока выделения сигналов живучести соединен с первым входом второго блока адресной селекции минимальной континуальной величины; второй выход блока выделения сигналов живучести соединен со вторым входом второго блока адресной селекции минимальной континуальной величины; третий выход блока выделения сигналов живучести соединен с третьим входом второго блока адресной селекции минимальной континуальной величины; четвертый выход блока выделения сигналов живучести соединен с четвертым входом второго блока адресной селекции минимальной континуальной величины; первый выход блока формирования сигналов живучести соединен с пятым выходом ячейки, с шестым выходом ячейки, с седьмым выходом ячейки и с восьмым выходом ячейки.

Сущность изобретения заключается в следующем. Множество ячеек однородной отказоустойчивой среды является элементами настройки матрицы из n×m процессорных элементов (ПЭ). Местоположение ПЭ и соответствующей ему ячейки однородной отказоустойчивой среды определяется ее физическим адресом (ФА) - (i,j) (где - номер строки, - номер столбца матрицы).

Каждая ячейка однородной отказоустойчивой среды (i,j) настраивает соответствующий ПЭ (i,j) на один из алгоритмов функционирования: собственный (i,j)-й, верхний (i+1,j)-й, нижний (i-1,j)-й, правый (i,j+1)-й, левый (i,j-1)-й в зависимости от отказов или изменения алгоритмов функционирования верхнего (i+1,j)-го, нижнего (i-1,j)-го, правого (i,j+1)-го и левого (i,j-1)-го ПЭ.

Номер алгоритма функционирования (i’,j’), на который настроен (i,j)-й ПЭ, будем называть виртуальным адресом (ВА) (i,j)-го ПЭ.

Первоначально (при отсутствии отказов) все ПЭ, за исключением резервных, имеют ВА, равный ФА. Резервные элементы назначаются произвольно и первоначально имеют ВА=(0,0), т.е. не выполняют никакого алгоритма функционирования.

При возникновении отказов ПЭ множество взаимодействующих ячеек однородной отказоустойчивой среды перенастраивает работоспособные ПЭ (в том числе и резервные) на новые ВА. Взаимодействие ячеек однородной отказоустойчивой среды осуществляется сигналами достижимости, программопереноса и живучести, поступающих от (i,j)-й ячейки однородной отказоустойчивой среды в (i+1,j)-ю, (i-l,j)-ю, (i,j+l)-ю и (i,j-l)-ю ячейки однородной отказоустойчивой среды и имеет своей целью построение непересекающихся маршрутов программопереноса от отказавших ПЭ к резервным.

Сигналы достижимости от (i,j)-й ячейки однородной отказоустойчивой среды информируют соседние ячейки о длине l маршрута достижимости от (i,j)-го ПЭ до ближайшего к нему резервного ПЭ:

где d - минимальное ненулевое значение сигнала, соответствующее расстоянию между соседними ячейками однородной отказоустойчивой среды, D - максимальное значение сигнала, соответствующее наибольшей возможной длине маршрута программопереноса:

Сигнал программопереноса от (i,j)-й ячейки информирует одну из соседних ячеек о перенастройке соответствующего ей ПЭ на (i,j)-й алгоритм. Сигналы программопереноса принимают либо нулевое, либо ненулевое значение. Нулевое значение сигнала означает отсутствие программопереноса в соответствующую ячейку.

Сигналы живучести от (i,j)-й ячейки однородной отказоустойчивой среды информируют соседние ячейки о количестве незаблокированных направлений программопереноса, доступных для (i,j)-й ячейки. Сигналы живучести принимают значения от 0 до 4d.

При отсутствии отказов резервных процессорных элементов сигналы достижимости вырабатываются ячейками однородной отказоустойчивой среды, соответствующими резервным элементам, во всех направлениях и имеют значение равное d. Остальные ячейки однородной отказоустойчивой среды вырабатывают сигналы достижимости во всех направлениях при поступлении хотя бы с одного направления сигнала достижимости со значением меньше величины D. При этом выходные сигналы достижимости принимают значение минимального входного сигнала из множества поступающих сигналов достижимости, увеличенное на величину d. Если сигналы достижимости со всех направлений имеют значение D, то ячейкой по всем направлениям вырабатываются сигналы достижимости со значением D. Каждая ячейка однородной отказоустойчивой среды также вырабатывает сигналы живучести, кратные d и принимающие значения от 0 до 4d, в зависимости от количества соседних ячеек, вырабатывающих сигналы достижимости, не равные D.

При возникновении отказов значение всех выходных сигналов достижимости ячеек однородной отказоустойчивой среды, соответствующих отказавшим ПЭ, устанавливается равным D. Каждая ячейка однородной отказоустойчивой среды, соответствующая отказавшему ПЭ, вырабатывает сигнал программопереноса с ненулевым значением, в направлении одной из соседних ячеек, при условии наличия сигнала достижимости с этого направления со значением, меньшим D, и равным минимальному среди значений сигналов достижимости со всех направлений. При наличии двух и более сигналов со значением, равным минимальному, направление программопереноса выбирается в соответствии с приоритетами направления: вправо, вверх, вниз, влево. На остальные направления подаются сигналы программопереноса с нулевым значением.

Ячейки однородной отказоустойчивой среды, соответствующие работоспособным ПЭ, вырабатывают ненулевой сигнал программопереноса только при поступлении такого сигнала от соседей. Ячейки однородной отказоустойчивой среды, соответствующие резервным элементам, не вырабатывают сигналы программопереноса.

При поступлении в одну ячейку однородной отказоустойчивой среды двух и более сигналов программопереноса возникает конфликтная ситуация, т.к. каждый ПЭ может переключиться по сигналу программопереноса только на один из алгоритмов соседних ПЭ. Конфликтная ситуация разрешается путем выдачи блокирующих сигналов достижимости по направлениям прихода сигналов живучести со значением, не равным минимальному. Сигналы достижимости на заблокированных направлениях принимают значение D. При этом соседние ячейки однородной отказоустойчивой среды отменяют сигналы программопереноса в заблокированных направлениях и вырабатывают их в других направлениях в соответствии с новыми минимальными значениями входных сигналов достижимости.

Фатальный отказ возникает только в случае прихода со всех направлений в ячейку сигналов достижимости со значением D и одновременно отказа ПЭ, связанного с этой ячейкой однородной отказоустойчивой среды, или поступления в нее ненулевого сигнала программопереноса. Если отказавший ПЭ является также резервным, то такая ситуация фатальным отказом не является.

Введение первого блока адресной селекции минимальной континуальной величины необходимо для определения направления передачи сигналов программопереноса.

Введение второго блока адресной селекции минимальной континуальной величины необходимо для управления переключением соответствующего ячейке ПЭ на исполнение алгоритма соседнего ПЭ.

Введение блоков ранговой селекции необходимо для разрешения конфликтных ситуаций при поступлении сигналов программопереноса с нескольких направлений.

Введение блока определения минимальной величины необходимо для определения минимального значения входных сигналов достижимости.

Введение блока разрешения приема программопереноса необходимо для определения ситуаций, в которых необходимо переключение соответствующего ячейке ПЭ на исполнение алгоритма соседнего ПЭ.

Введение блока формирования сигналов живучести необходимо для определения количества доступных ячейке направлений программопереноса.

Введение блока выделения сигналов живучести необходимо для выделения сигналов живучести, поступающих с конфликтных направлений.

Введение первого блока демультиплексора необходимо для обеспечения выдачи сигналов программопереноса в заданных направлениях.

Введение второго блока демультиплексора необходимо для обеспечения выдачи сигналов достижимости в заданных направлениях.

Введение блока определения фатального отказа необходимо для выявления ситуаций фатального отказа.

Введение блока-формирователя опорных напряжений необходимо для задания величин напряжений сигналов d и D.

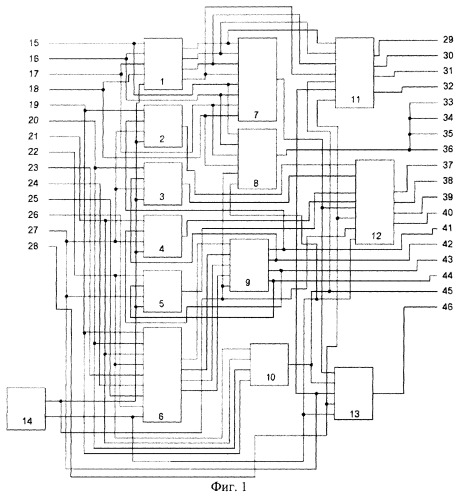

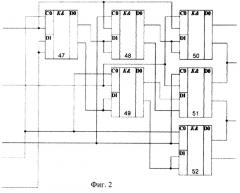

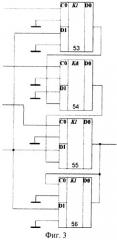

Сущность изобретения поясняется чертежами, где на фиг.1 показана функциональная схема ячейки однородной отказоустойчивой среды процессорных элементов; на фиг.2 - функциональная схема блока адресной селекции минимальной континуальной величины; на фиг.3 - функциональная схема блока ранговой селекции; на фиг.4 - функциональная схема блока выделения сигналов живучести; на фиг.5 - функциональная схема блока определения минимальной величины; на фиг.6 - функциональная схема блока формирования сигналов живучести; на фиг.7 - функциональная схема блока разрешения приема программопереноса; на фиг.8 - функциональная схема первого блока демультиплексора; на фиг.9 - функциональная схема второго блока демультиплексора; на фиг.10 - функциональная схема блока определения фатального отказа; на фиг.11а - элемент континуальной конъюнкции с двумя выходами; на фиг.11б - элемент континуальной конъюнкции с одним выходом; на фиг.12а - элемент континуальной дизъюнкции с двумя выходами; на фиг.12б - элемент континуальной дизъюнкции с одним выходом; на фиг.13 - схема распространения сигналов при отсутствии отказов; на фиг.14 - схема распространения сигналов при одном отказе; на фиг.15 - схема распространения сигналов при трех отказах; на фиг.16 - схема распространения сигналов при фатальном отказе; на фиг.17 - схема распространения сигналов при пяти отказах, на фиг.18 - процесс реконфигурации однородной отказоустойчивой среды процессорных элементов при двух отказах.

Ячейка однородной отказоустойчивой среды процессорных элементов (фиг.1) содержит первый 1 и второй 9 блоки адресной селекции минимальной континуальной величины, блок 10 разрешения приема программопереноса, первый 11 и второй 12 блоки демультиплексора, блок 13 определения фатального отказа, блок 14 формирования опорных напряжений, первый 2, второй 3, третий 4 и четвертый 5 блоки ранговой селекции, блок 6 выделения сигналов живучести, блок 7 определения минимальной континуальной величины и блок 8 формирования сигналов живучести, причем первый 15 вход ячейки соединен с первым входом первого 1 блока адресной селекции минимальной континуальной величины, с пятым входом блока 7 определения минимальной континуальной величины и с первым входом блока 8 формирования сигналов живучести; второй 16 вход ячейки соединен со вторым входом первого 1 блока адресной селекции минимальной континуальной величины, с шестым входом блока 7 определения минимальной континуальной величины и со вторым входом блока 8 формирования сигналов живучести; третий 17 вход ячейки соединен с третьим входом первого 1 блока адресной селекции минимальной континуальной величины, с седьмым входом блока 7 определения минимальной континуальной величины и с третьим входом блока 8 формирования сигналов живучести; четвертый 18 вход ячейки соединен с четвертым входом первого 1 блока адресной селекции минимальной континуальной величины, с восьмым входом блока 7 определения минимальной континуальной величины и с четвертым входом блока 8 формирования сигналов живучести; пятый 19 вход ячейки соединен с четвертым входом блока 10 разрешения приема программопереноса, с первым входом первого 2 блока ранговой селекции и с первым входом блока 6 выделения сигналов живучести; шестой 20 вход ячейки соединен с третьим входом блока 10 разрешения приема программопереноса, с первым входом второго 3 блока ранговой селекции и со вторым входом блока 6 выделения сигналов живучести; седьмой 21 вход ячейки соединен со вторым входом блока 10 разрешения приема программопереноса, с первым входом третьего 4 блока ранговой селекции и с третьим входом блока 6 выделения сигналов живучести; восьмой 22 вход ячейки соединен с первым входом блока 10 разрешения приема программопереноса, с первым входом четвертого 5 блока ранговой селекции и с четвертым входом блока 6 выделения сигналов живучести; девятый 23 вход ячейки соединен с пятым входом блока 6 выделения сигналов живучести; десятый 24 вход ячейки соединен с шестым входом блока 6 выделения сигналов живучести; одиннадцатый 25 вход ячейки соединен с седьмым входом блока 6 выделения сигналов живучести; двенадцатый 26 вход ячейки соединен с восьмым входом блока 6 выделения сигналов живучести; тринадцатый 27 вход ячейки соединен с шестым входом первого 11 блока демультиплексора, с третьим входом блока 13 определения фатального отказа, с третьим входом первого 2 блока ранговой селекции, с третьим входом второго 3 блока ранговой селекции, с третьим входом третьего 4 блока ранговой селекции и с третьим входом четвертого 5 блока ранговой селекции; четырнадцатый 28 вход ячейки соединен с седьмым входом первого 11 блока демультиплексора, с шестым входом второго 12 блока демультиплексора и с четвертым входом блока 13 определения фатального отказа; первый выход первого 1 блока адресной селекции минимальной континуальной величины соединен с первым входом первого 11 блока демультиплексора и с первым входом блока 7 определения минимальной континуальной величины; второй выход первого 1 блока адресной селекции минимальной континуальной величины соединен со вторым входом первого 11 блока демультиплексора и со вторым входом блока 7 определения минимальной континуальной величины; третий выход первого 1 блока адресной селекции минимальной континуальной величины соединен с третьим входом первого 11 блока демультиплексора и с третьим входом блока 7 определения минимальной континуальной величины; четвертый выход первого 1 блока адресной селекции минимальной континуальной величины соединен с четвертым входом первого 11 блока демультиплексора и с четвертым входом блока 7 определения минимальной континуальной величины; первый выход блока 14 формирования опорных напряжений соединен с пятым входом первого 1 блока адресной селекции минимальной континуальной величины, с седьмым входом второго 12 блока демультиплексора, с четвертым входом первого 2 блока ранговой селекции, с четвертым входом второго 3 блока ранговой селекции, с четвертым входом третьего 4 блока ранговой селекции, с четвертым входом четвертого 5 блока ранговой селекции, с пятым входом блока 8 формирования сигналов живучести и с пятым входом второго 9 блока адресной селекции минимальной континуальной величины; первый выход блока 10 разрешения приема программопереноса соединен с пятым входом первого 11 блока демультиплексора, со вторым входом блока 13 определения фатального отказа и с семнадцатым 45 выходом ячейки; первый выход первого 11 блока демультиплексора соединен с первым 29 выходом ячейки; второй выход первого 11 блока демультиплексора соединен со вторым 30 выходом ячейки; третий выход первого 11 блока демультиплексора соединен с третьим 31 выходом ячейки; четвертый выход первого 11 блока демультиплексора соединен с четвертым 32 выходом ячейки; первый выход второго 12 блока демультиплексора соединен с девятым 37 выходом ячейки; второй выход второго 12 блока демультиплексора соединен с десятым 38 выходом ячейки; третий выход второго 12 блока демультиплексора соединен с одиннадцатым 39 выходом ячейки; четвертый выход второго 12 блока демультиплексора соединен с двенадцатым 40 выходом ячейки; первый выход первого 2 блока ранговой селекции соединен с первым входом второго 12 блока демультиплексора; первый выход второго 3 блока ранговой селекции соединен со вторым входом второго 12 блока демультиплексора; первый выход третьего 4 блока ранговой селекции соединен с третьим входом второго 12 блока демультиплексора; первый выход четвертого 5 блока ранговой селекции соединен с четвертым входом второго 12 блока демультиплексора; первый выход блока 7 определения минимальной континуальной величины соединен с пятым входом второго 12 блока демультиплексора и с первым входом блока 13 определения фатального отказа; второй выход блока 14 формирования опорных напряжений соединен с восьмым входом второго 12 блока демультиплексора, с пятым входом блока 13 определения фатального отказа, с девятым входом блока 6 выделения сигналов живучести и с шестым входом блока 8 формирования сигналов живучести; первый выход блока 13 определения фатального отказа соединен с восемнадцатым 46 выходом ячейки; первый выход второго 9 блока адресной селекции минимальной континуальной величины соединен со вторым входом первого 2 блока ранговой селекции и с тринадцатым 41 выходом ячейки; второй выход второго 9 блока адресной селекции минимальной континуальной величины соединен со вторым входом второго 3 блока ранговой селекции и с четырнадцатым 42 выходом ячейки; третий выход второго 9 блока адресной селекции минимальной континуальной величины соединен со вторым входом третьего 4 блока ранговой селекции и с пятнадцатым 43 выходом ячейки; четвертый выход второго 9 блока адресной селекции минимальной континуальной величины соединен со вторым входом четвертого 5 блока ранговой селекции и с шестнадцатым 44 выходом ячейки; первый выход блока 6 выделения сигналов живучести соединен с первым входом второго 9 блока адресной селекции минимальной континуальной величины; второй выход блока 6 выделения сигналов живучести соединен со вторым входом второго 9 блока адресной селекции минимальной континуальной величины; третий выход блока 6 выделения сигналов живучести соединен с третьим входом второго 9 блока адресной селекции минимальной континуальной величины; четвертый выход блока 6 выделения сигналов живучести соединен с четвертым входом второго 9 блока адресной селекции минимальной континуальной величины; первый выход блока 8 формирования сигналов живучести соединен с пятым 33 выходом ячейки, с шестым 34 выходом ячейки, с седьмым 35 выходом ячейки и с восьмым 36 выходом ячейки.

Первый 1 и второй 9 блоки адресной селекции минимальной континуальной величины (фиг.2) содержат первый 47, второй 48, третий 49, четвертый 50, пятый 51 и шестой 52 элементы континуальной конъюнкции, причем первый вход блока соединен со вторым входом первого 47 элемента континуальной конъюнкции, со вторым входом второго 48 элемента континуальной конъюнкции и со вторым входом четвертого 50 элемента континуальной конъюнкции; второй вход блока соединен со вторым входом третьего 49 элемента континуальной конъюнкции, с первым входом четвертого 50 элемента континуальной конъюнкции и со вторым входом пятого 51 элемента континуальной конъюнкции; третий вход блока соединен с первым входом второго 48 элемента континуальной конъюнкции, с первым входом пятого 51 элемента континуальной конъюнкции и со вторым входом шестого 52 элемента континуальной конъюнкции; четвертый вход блока соединен с первым входом первого 47 элемента континуальной конъюнкции, с первым входом третьего 49 элемента континуальной конъюнкции и с первым входом шестого 52 элемента континуальной конъюнкции; пятый вход блока соединен с третьим входом первого 47 элемента континуальной конъюнкции и с четвертым входом первого 47 элемента континуальной конъюнкции; первый выход первого 47 элемента континуальной конъюнкции соединен с третьим входом второго 48 элемента континуальной конъюнкции и с четвертым входом второго 48 элемента континуальной конъюнкции; второй выход первого 47 элемента континуальной конъюнкции соединен с третьим входом третьего 49 элемента континуальной конъюнкции и с четвертым входом третьего 49 элемента континуальной конъюнкции; первый выход второго 48 элемента континуальной конъюнкции соединен с третьим входом четвертого 50 элемента континуальной конъюнкции и с четвертым входом четвертого 50 элемента континуальной конъюнкции; второй выход второго 48 элемента континуальной конъюнкции соединен с четвертым входом пятого 51 элемента континуальной конъюнкции; первый выход третьего 49 элемента континуальной конъюнкции соединен с третьим входом пятого 51 элемента континуальной конъюнкции; второй выход третьего 49 элемента континуальной конъюнкции соединен с третьим входом шестого 52 элемента континуальной конъюнкции и с четвертым входом шестого 52 элемента континуальной конъюнкции; первый выход четвертого 50 элемента континуальной конъюнкции соединен с первым выходом блока; второй выход четвертого 50 элемента континуальной конъюнкции соединен с первым выходом пятого 51 элемента континуальной конъюнкции и со вторым выходом блока; второй выход пятого 51 элемента континуальной конъюнкции соединен с первым выходом шестого 52 элемента континуальной конъюнкции и с третьим выходом блока; второй выход шестого 52 элемента континуальной конъюнкции соединен с четвертым выходом блока.

Первый 2, второй 3, третий 4 и четвертый 5 блоки ранговой селекции (фиг.3) содержат первый 53, второй 55 и третий 56 элементы континуальной дизъюнкции и элемент 54 континуальной конъюнкции, причем первый вход блока соединен с первым входом первого 53 элемента континуальной дизъюнкции; второй вход блока соединен с первым входом элемента 54 континуальной конъюнкции; третий вход блока соединен с первым входом второго 55 элемента континуальной дизъюнкции; четвертый вход блока соединен с третьим входом первого 53 элемента континуальной дизъюнкции, с третьим входом второго 55 элемента континуальной дизъюнкции и с третьим входом третьего 56 элемента континуальной дизъюнкции; первый выход первого 53 элемента континуальной дизъюнкции соединен с четвертым входом элемента 54 континуальной конъюнкции; второй вход первого 53 элемента континуальной дизъюнкции, четвертый вход первого 53 элемента континуальной дизъюнкции, второй вход элемента 54 континуальной конъюнкции, третий вход элемента 54 континуальной конъюнкции, второй вход второго 55 элемента континуальной дизъюнкции, второй вход третьего 56 элемента континуальной дизъюнкции и четвертый вход третьего 56 элемента континуальной дизъюнкции заземлены; первый выход элемента 54 континуальной конъюнкции соединен с четвертым входом второго 55 элемента континуальной дизъюнкции; первый выход второго 55 элемента континуальной дизъюнкции соединен с первым выходом третьего 56 элемента континуальной дизъюнкции, с первым входом третьего 56 элемента континуальной дизъюнкции и с первым выходом блока.

Блок 6 выделения сигналов живучести (фиг.4) содержит первый 57, второй 58, третий 59 и четвертый 60 элементы континуальной конъюнкции, причем первый вход блока соединен с первым входом первого 57 элемента континуальной конъюнкции; второй вход блока соединен с первым входом второго 58 элемента континуальной конъюнкции; третий вход блока соединен с первым входом третьего 59 элемента континуальной конъюнкции; четвертый вход блока соединен с первым входом четвертого 60 элемента континуальной конъюнкции; пятый вход блока соединен с третьим входом первого 57 элемента континуальной конъюнкции; шестой вход блока соединен с третьим входом второго 58 элемента континуальной конъюнкции; седьмой вход блока соединен с третьим входом третьего 59 элемента континуальной конъюнкции; восьмой вход блока соединен с третьим входом четвертого 60 элемента континуальной конъюнкции; девятый вход блока соединен с четвертым входом первого 57 элемента континуальной конъюнкции, с четвертым входом второго 58 элемента континуальной конъюнкции, с четвертым входом третьего 59 элемента континуальной конъюнкции и с четвертым входом четвертого 60 элемента континуальной конъюнкции; первый выход первого 57 элемента континуальной конъюнкции соединен с первым выходом блока; второй вход первого 57 элемента континуальной конъюнкции, второй вход второго 58 элемента континуальной конъюнкции, второй вход третьего 59 элемента континуальной конъюнкции и второй вход четвертого 60 элемента континуальной конъюнкции заземлены; первый выход второго 58 элемента континуальной конъюнкции соединен со вторым выходом блока; первый выход третьего 59 элемента континуальной конъюнкции соединен с третьим выходом блока; первый выход четвертого 60 элемента континуальной конъюнкции соединен с четвертым выходом блока.

Блок 7 определения минимальной величины (фиг.5) содержит первый 61 и второй 62 элементы континуальной дизъюнкции и элемент 63 континуальной конъюнкции, причем первый вход блока соединен с первым входом первого 61 элемента континуальной дизъюнкции; второй вход блока соединен со вторым входом первого 61 элемента континуальной дизъюнкции; третий вход блока соединен с первым входом второго 62 элемента континуальной дизъюнкции; четвертый вход блока соединен со вторым входом второго 62 элемента континуальной дизъюнкции; пятый вход блока соединен с третьим входом первого 61 элемента континуальной дизъюнкции; шестой вход блока соединен с четвертым входом первого 61 элемента континуальной дизъюнкции; седьмой вход блока соединен с третьим входом второго 62 элемента континуальной дизъюнкции; восьмой вход блока соединен с четвертым входом второго 62 элемента континуальной дизъюнкции; первый выход первого 61 элемента континуальной дизъюнкции соединен со вторым выходом первого 61 элемента континуальной дизъюнкции, со вторым входом элемента 63 континуальной конъюнкции и с третьим входом элемента 63 континуальной конъюнкции; первый выход второго 62 элемента континуальной дизъюнкции соединен со вторым выходом второго 62 элемента континуальной дизъюнкции, с первым входом элемента 63 континуальной конъюнкции и с четвертым входом элемента 63 континуальной конъюнкции; первый выход элемента 63 континуальной конъюнкции соединен со вторым выходом элемента 63 континуальной конъюнкции и с первым выходом блока.

Блок 8 формирования сигналов живучести (фиг.6) содержит первый 64, второй 65, третий 66 и четвертый 67 элементы континуальной дизъюнкции, первый 68, второй 69 и третий 70 элементы суммирования аналоговых сигналов, причем первый вход блока соединен со вторым входом первого 64 элемента континуальной дизъюнкции; второй вход блока соединен со вторым входом второго 65 элемента континуальной дизъюнкции; третий вход блока соединен со вторым входом третьего 66 элемента континуальной дизъюнкции; четвертый вход блока соединен со вторым входом четвертого 67 элемента континуальной дизъюнкции; пятый вход блока соединен с третьим входом первого 64 элемента континуальной дизъюнкции, с третьим входом второго 65 элемента континуальной дизъюнкции, с третьим входом третьего 66 элемента континуальной дизъюнкции и с третьим входом четвертого 67 элемента континуальной дизъюнкции; шестой вход блока соединен с первым входом первого 64 элемента континуальной дизъюнкции, с первым входом второго 65 элемента континуальной дизъюнкции, с первым входом третьего 66 элемента континуальной дизъюнкции и с первым входом четвертого 67 элемента континуальной дизъюнкции; первый выход первого 64 элемента континуальной дизъюнкции соединен с первым входом первого 68 элемента суммирования аналоговых сигналов; четвертый вход первого 64 элемента континуальной дизъюнкции, четвертый вход второго 65 элемента континуальной дизъюнкции, четвертый вход третьего 66 элемента континуальной дизъюнкции и четвертый вход четвертого 67 элемента континуальной дизъюнкции заземлены; первый выход второго 65 элемента континуальной дизъюнкции соединен со вторым входом первого 68 элемента суммирования аналоговых с