Устройство фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска

Иллюстрации

Показать всеИзобретение относится к устройствам импульсной техники и может быть использовано в прецизионных генераторах импульсов. Технический результат заключается в повышении точности формируемых задержек при привязке их к импульсу внешнего запуска при любой заданной длительности задержки, а также обеспечение возможности формирования любого необходимого числа временных задержек без соответствующего дублирования оборудования. Устройство содержит первое логическое устройство, предназначенное для пропускания тактовых импульсов, начиная с первого импульса, следующего за импульсом внешнего запуска, схему задержки импульса внешнего запуска, селектор первого импульса, задающий и воспроизводящий генераторы линейно изменяющихся напряжений, компаратор, второе логическое устройство, предназначенное для пропускания тактовых импульсов с первого логического устройства без первого импульса, счетчик импульсов, устройство сравнения кодов, запоминающее устройство, логический автомат, предназначенный для отпирания аналогового ключа и последовательной выборки кодов задержек из запоминающего устройства, формирователь выходных синхроимпульсов, аналого-цифровой преобразователь, цифроаналоговый преобразователь и аналоговый ключ. 4 ил.

Реферат

Изобретение относится к устройствам импульсной техники и может быть использовано в прецизионных генераторах импульсов.

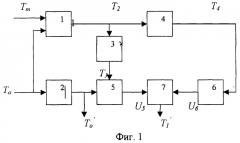

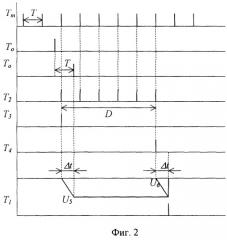

В прецизионных генераторах импульсов, предназначенных для генерирования последовательностей импульсов с задаваемыми длительностью, временной задержкой и периодом повторения, возникает проблема фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска. Если необходимая точность привязки сопоставима с периодом следования опорных тактовых импульсов, вырабатываемых внутренним кварцевым генератором и синхронизирующих работу всех узлов генератора импульсов, то эта проблема легко решается средствами цифровой схемотехники, т.е. запуск вырабатываемой последовательности импульсов осуществляется по первому тактовому импульсу, следующему за импульсом внешнего запуска. Поскольку импульс внешнего запуска никак не привязан к импульсам опорной тактовой последовательности генератора импульсов, то погрешность привязки вырабатываемой генератором последовательности импульсов к импульсу внешнего запуска при таком способе привязки может варьироваться в пределах одного периода опорных тактовых импульсов. Если же допустимая временная погрешность привязки должна быть существенно меньше периода опорной тактовой последовательности, то ее решение значительно усложняется. Средствами цифровой схемотехники удается осуществить фазовую привязку только с точностью, соответствующей половине периода тактовых импульсов [1, 2]. При использовании последовательной цепочки элементов задержки с суммарной задержкой, соответствующей периоду тактовых импульсов, удается снизить эту погрешность до величины, соответствующей величине задержки одного элемента задержки, которая примерно соответствует периоду тактовых импульсов, поделенному на число элементов задержки в последовательной цепочке [3]. Для точной привязки генерируемой импульсной последовательности к сигналу внешнего запуска используются средства аналоговой схемотехники. Примером такого решения может служить устройство фазовой привязки, используемое в прецизионном генераторе импульсов Г5-66 [4], структурная схема которого приведена на фиг.1, а временные диаграммы, поясняющие принцип его работы, - на фиг.2. Именно это решение принято в качестве прототипа.

Схема фазовой привязки (фиг.1) состоит из логического устройства 1, схемы задержки 2 импульса внешнего запуска, селектора 3 первого импульса тактовой последовательности, делителя частоты 4 с переменным коэффициентом деления, задающего 5 и воспроизводящего 6 генераторов линейно изменяющегося напряжения (ГЛИН) и аналогового компаратора 7.

Устройство работает следующим образом.

От генератора тактовых импульсов на вход Вх1 логического устройства 1 непрерывно поступает последовательность тактовых импульсов Тm частотой 10 МГц. Импульс внешнего запуска Т0 поступает на вход Вх2 логического устройства 1 и одновременно на вход схемы задержки 2 импульса внешнего запуска, которая задерживает его на время, примерно равное периоду следования тактовых импульсов. Логическое устройство 1 пропускает импульсы тактовой последовательности, только начиная с первого импульса, следующего за импульсом внешнего запуска Т0 (последовательность импульсов Т2 на фиг.2). Эти импульсы попадают на входы делителя частоты 4 с переменным коэффициентом деления и селектора 3 первого импульса последовательности. Установкой коэффициента деления делителя частоты 4 с переменным коэффициентом деления задают необходимую временную задержку D между внешним импульсом запуска и генерируемым импульсом (или между первым и вторым генерируемыми импульсами, если первый импульс формируется по задержанному импульсу внешнего запуска Т0). Селектор 3 первого импульса последовательности выделяет первый из пропущенных логическим устройством 1 импульсов (T3). Этот импульс запускает задающий ГЛИН 5, построенный как интегратор заданного тока, который может отключаться по управляющему сигналу, в результате чего на выходе ГЛИН будет сохраняться уровень напряжения, соответствующий моменту прихода управляющего импульса. В качестве управляющего импульса используется задержанный импульс внешнего запуска Т'0, поступающий с выхода схемы задержки 2 импульса внешнего запуска. Задержка импульса внешнего запуска необходима для обеспечения возможности запоминания временного сдвига между импульсом внешнего запуска и ближайшим к нему предшествующим импульсом тактовой последовательности с тем, чтобы на тот же интервал сдвинуть выходной импульс генератора относительно выбранного тактового импульса. Таким образом, в момент прихода задержанного импульса внешнего запуска Т'0 на управляющий вход ГЛИН 5 уровень напряжения на нем запоминается и поступает на один из входов компаратора 7. Импульс Т4 с выхода делителя частоты 4 с переменным коэффициентом деления запускает ГЛИН 8, выходное напряжение которого поступает на второй вход компаратора 7. В момент, когда оно сравняется с напряжением, сохраняемым на первом входе компаратора, он срабатывает и формирует импульс Т1, который будет сдвинут относительно импульса Т'0 ровно на установленное время задержки D, поскольку скорости нарастания линейно изменяющихся напряжений у обоих ГЛИН должны быть одинаковы.

Однако описанное устройство фазовой привязки имеет существенные недостатки:

1. При времени задержки D, намного превышающем период тактовых импульсов, запоминающий конденсатор задающего ГЛИН, на котором должно поддерживаться постоянное напряжение в течение всего времени задержки, будет разряжаться, что приведет к неравенству ширины формируемых ГЛИН 5 и ГЛИН 6 импульсов Δt1 и Δt2, а значит, и к несоответствию действительной задержки выходного импульса Т1 установленному значению (действительно, в генераторе импульсов Г5-66 погрешность времени задержки пропорционально возрастает с увеличением времени задержки).

2. При необходимости формирования нескольких задержек (например, при формировании последовательности импульсов, задерживаемых на заданные значения: D1, D2, D3 и т.д.) этот способ потребует дублирования узлов 4, 6 и 7 по числу формируемых задержек и при этом запоминающий конденсатор ГЛИН 5 окажется нагруженным на соответствующее число входов компараторов, что приведет к усугублению первого недостатка.

Техническими задачами, на решение которых направлено настоящее изобретение, являются повышение точности формируемых задержек при привязке их к импульсу внешнего запуска при любой заданной длительности задержки и обеспечение возможности формирования любого необходимого числа временных задержек без соответствующего дублирования оборудования.

Решение этих задач обеспечивается путем использования аналого-цифрового способа сохранения напряжения на выходе задающего ГЛИН, пропорционального временному интервалу между импульсом внешнего запуска и предшествующим ему импульсом опорной тактовой последовательности и временному сдвигу на этот интервал всей опорной тактовой последовательности, из которой затем формируются все необходимые временные интервалы, соответствующие заданным задержкам и длительностям импульсов. Реализация этого способа осуществляется за счет того, что вместо делителя частоты с переменным коэффициентом деления в устройстве используется счетчик импульсов и дополнительно введены второе логическое устройство, схема сравнения кодов, запоминающее устройство, логический автомат, формирователь выходных синхроимпульсов, аналого-цифровой преобразователь, цифроаналоговый преобразователь и аналоговый ключ. При этом выход первого логического устройства соединен с входами селектора первого импульса, второго логического устройства и счетчика импульсов. Второй вход второго логического устройства соединен с выходом схемы задержки импульса внешнего запуска. Выход селектора первого импульса соединен с первым управляющим входом задающего генератора линейно изменяющегося напряжения, второй управляющий вход которого подключен к выходу схемы задержки импульса внешнего запуска. Выход второго логического устройства подключен к первому управляющему входу воспроизводящего генератора линейно изменяющегося напряжения, второй управляющий вход которого соединен с выходом компаратора, который также соединен с первым входом формирователя выходных синхроимпульсов. Параллельный выход счетчика импульсов соединен с одним из входов схемы сравнения кодов, второй вход которой соединен с запоминающим устройством, в которое предварительно заносятся коды длительностей формируемых задержек. Выход схемы сравнения кодов соединен со вторым входом формирователя выходных синхроимпульсов и одним из входов логического автомата, второй вход которого соединен с выходом схемы задержки импульса внешнего запуска. Первый выход логического автомата соединен с управляющим входом запоминающего устройства, а второй выход - с управляющим входом аналогового ключа, сигнальный вход которого соединен с выходом цифроаналогового преобразователя, а выход - с первым входом компаратора. Вход цифроаналогового преобразователя соединен с выходом аналого-цифрового преобразователя, а вход последнего - с выходом задающего генератора линейно изменяющегося напряжения.

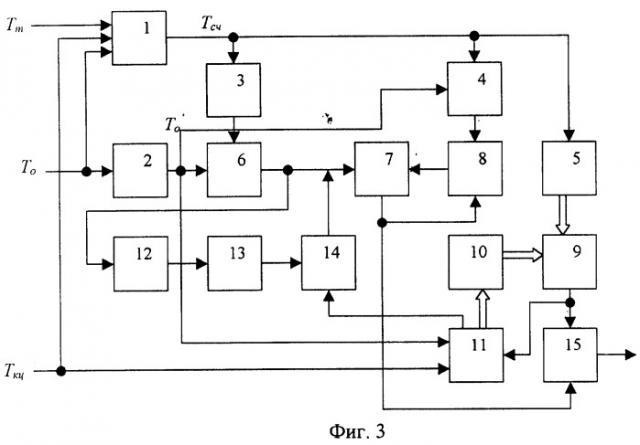

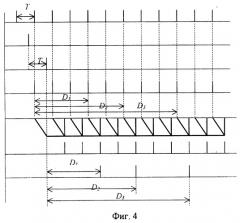

Структурно-функциональная схема предлагаемого устройства фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска представлена на фиг.3, а поясняющие ее функционирование временные диаграммы - на фиг.4.

Устройство фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска состоит из первого логического устройства 1, схемы задержки 2 импульса внешнего запуска, селектора первого импульса 3, второго логического устройства 4, счетчика импульсов 5, задающего ГЛИН 6, компаратора 7, воспроизводящего ГЛИН 8, устройства сравнения кодов 9, запоминающего устройства 10, логического автомата 11, аналого-цифрового преобразователя 12, цифроаналогового преобразователя 13, аналогового ключа 14 и формирователя 15 выходных синхроимпульсов. Логическое устройство 1 имеет три входа. На первый вход поступает тактовая последовательность импульсов Tm, на второй вход - импульс конца цикла генерации Ткц и на третий вход - импульс внешнего запуска Т0. Этот же импульс Т0 поступает на вход схемы задержки 2 импульса внешнего запуска. Выход логического устройства 1 соединен с входами селектора первого импульса 3, второго логического устройства 4 и счетчика импульсов 5, Выход селектора первого импульса 3 соединен с первым управляющим входом задающего ГЛИН б, второй управляющий вход которого соединен с выходом схемы задержки 2 импульса внешнего запуска. Выход второго логического устройства 4 соединен с первым управляющим входом воспроизводящего ГЛИН 8, а второй вход второго логического устройства 4 соединен с выходом схемы задержки 2 импульса внешнего запуска. Выход задающего ГЛИН 6 соединен с первым входом компаратора 7 и с входом аналого-цифрового преобразователя 12. Выход воспроизводящего ГЛИН 8 соединен со вторым входом компаратора 7, выход которого соединен с первым входом формирователя 15 выходных синхроимпульсов и со вторым управляющим входом воспроизводящего ГЛИН 8. Параллельный выход счетчика импульсов 5 соединен с одним из входов схемы сравнения кодов 9, второй вход которой соединен с выходом запоминающего устройства 10, в которое предварительно заносятся коды длительностей формируемых задержек. Выход схемы сравнения кодов 9 соединен со вторым входом формирователя 15 выходных синхроимпульсов и одним из входов логического автомата 11, второй вход которого соединен с выходом схемы задержки 2 импульса внешнего запуска. Первый выход логического автомата 11 соединен с управляющим входом запоминающего устройства 10, а второй выход - с управляющим входом аналогового ключа 14, сигнальный вход которого соединен с выходом цифроаналогового преобразователя 13. Вход цифроаналогового преобразователя 13 соединен с выходом аналого-цифрового преобразователя 12.

Устройство фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска работает следующим образом.

При поступлении импульса внешнего запуска Т0 логическое устройство 1 начинает пропускать импульсы опорной тактовой последовательности Тm, начиная с импульса, следующего за импульсом внешнего запуска T0 (см фиг.4). Эти импульсы поступают на входы селектора первого импульса 3, второго логического устройства 4 и счетчика импульсов 5. Импульс, прошедший через селектор первого импульса 3, запускает задающий ГЛИН 6, а воспроизводящий ГЛИН 8 в это время не работает, т.к. второе логическое устройство 4 не пропускает первый импульс, прошедший через первое логическое устройство 1, поскольку открывается лишь после прихода задержанного импульса внешнего запуска Т'0. Схема задержки 2 импульса внешнего запуска задерживает этот импульс на интервал времени, равный периоду следования тактовых импульсов Тm. Генераторы линейно изменяющегося напряжения ГЛИН 6 и ГЛИН 8 построены как интеграторы тока, задаваемого высокостабильными управляемыми генераторами тока. В момент прихода на второй управляющий вход задающего ГЛИН 6 задержанного импульса внешнего запуска Т'0 его генератор тока отключается и на выходе ГЛИН 6 сохраняется уровень напряжения, соответствующий моменту прихода задержанного импульса внешнего запуска Т'0. В воспроизводящем ГЛИН 8, который запускается лишь вторым и последующими тактовыми импульсами, прошедшими через логическое устройство 1, уровень выходного напряжения возрастает лишь до уровня напряжения, поддерживаемого на первом входе компаратора 7 (т.е. до уровня напряжения, сохраняемого на выходе задающего ГЛИН 6 после прохождения первого тактового импульса, прошедшего через логическое устройство 1). После достижения этого уровня напряжение на выходе ГЛИН 8 обнуляется, т.к. перепад напряжения на выходе компаратора 7 сбрасывает его, после чего компаратор возвращается в исходное состояние. Поскольку скорости нарастания линейно изменяющихся напряжений ГЛИН 6 и ГЛИН 8 одинаковы, то длительности их фронта нарастания Δt1 и Δt2 (см. фиг.4) тоже будут одинаковы. Короткие импульсы, формируемые на выходе компаратора 7 после прихода каждого очередного тактового импульса (начиная со второго), окажутся сдвинутыми относительно исходной тактовой последовательности импульсов на этот интервал времени Δt, равный сдвигу импульса внешнего запуска Т0 относительно предшествующего ему тактового импульса. Из этой сдвинутой последовательности импульсов затем и формируются все необходимые временные задержки, что и обеспечивает их фазовую привязку к импульсу внешнего запуска. Для этого эти импульсы поступают на один из входов формирователя 15 выходных синхроимпульсов.

Формирование заданных временных задержек Di производится с помощью счетчика импульсов 5, заполняемого тактовыми импульсами, прошедшими через логическую схему 1, устройства сравнения кодов 9 и запоминающего устройства 10, в которое предварительно заносятся цифровые коды длительностей формируемых задержек Ni. Коды чисел, непрерывно формируемые на счетчике 5 по мере поступления на его вход тактовых импульсов, последовательно сравниваются схемой сравнения кодов 9 с каждым из кодов задержек (начиная с наименьшего), записанных в запоминающем устройстве 10. Последовательностью выборки из запоминающего устройства кодов задержек управляет логический автомат 11. Для этого на один из его входов подаются выходные импульсы Тзад со схемы сравнения кодов 9, формируемые при совпадении кодов на обоих его входах, задержанный импульс внешнего запуска Т0 и импульс конца цикла Ткц, определяющий период повторения генерируемой последовательности импульсов генератора. Формирователь выходных синхроимпульсов фактически выполняет функцию схемы “И”, на один из входов которой поступают задержанные на интервалы Di импульсы Тзад с выхода схемы совпадения кодов, длительность которых соответствует периоду следования тактовых импульсов, а на второй вход - короткие импульсы Тm сдвинутой на Δt тактовой последовательности с выхода компаратора.

Точность фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска при больших длительностях задержек (в генераторе Г5-66 времена задержек могут задаваться в пределах от 200 нс до 999999 мкс) обеспечивается за счет аналого-цифрового способа поддержания постоянства сформированного на выходе ГЛИН 6 уровня напряжения, подаваемого на первый вход компаратора 7. Это осуществляется с помощью последовательно включенных аналого-цифрового преобразователя 12, цифроаналогового преобразователя 13 и аналогового ключа 14. На вход аналого-цифрового преобразователя 12 поступает напряжение, формируемое на выходе ГЛИН 6. Оно преобразуется в цифровой код, который поступает на вход цифроаналогового преобразователя 13, а с его выхода соответствующее напряжение подается на аналоговый ключ 14. Аналоговый ключ управляется логическим автоматом 11, который открывает его тогда, когда гарантированно закончатся все переходные процессы в аналого-цифровом и цифроаналоговом преобразователях, что занимает определенное число тактов (в зависимости от быстродействия выбранных АЦП и ЦАП, причем требования к их быстродействию не жесткие). Все это время на первом входе компаратора уровень напряжения поддерживается постоянным за счет ГЛИН 6, находящегося в режиме хранения выходного напряжения. Далее аналоговый ключ 14 открывается и к входу компаратора подключается выходное напряжение цифроаналогового преобразователя 13, которое остается неизменным до конца цикла генерации, после чего выход ГЛИН 6 с помощью того же аналогового ключа обнуляется и он готов к следующему циклу. Такой способ формирования задержек обеспечивает независимость точности их формирования от длительности назначаемых задержек и в то же время не требует использования высокоскоростных АЦП и ЦАП. Количество же формируемых задержек ограничивается лишь емкостью запоминающего устройства.

Логический автомат 11 в данном устройстве работает следующим образом. Задержанный импульс внешнего запуска Т0', поступающий на его первый вход, инициирует начало цикла его работы. Этот импульс устанавливает имеющийся в нем формирователь адреса (им может быть счетчик импульсов) ячеек запоминающего устройства 10, в которые предварительно заносят цифровые коды, соответствующие моментам всех событий в цикле генерируемой последовательности (моменты фронтов и спадов импульсов и включения аналогового ключа 14), в первое состояние, соответствующее адресу ячейки, в которую занесен код момента первого события. Выход формирователя адреса подключен к входу запоминающего устройства 10, а выход управления аналоговым ключом 14 - к его управляющему входу. Импульсы, поступающие с выхода устройства сравнения кодов 9, переключают формирователь адреса (счетчик) в следующие состояния, которым соответствуют адреса ячеек с последовательно возрастающими длительностями задержек. Если интервал времени между задержанным импульсом внешнего запуска Т0' и очередным (включая и первый) импульсом Тзад, поступившим с выхода устройства сравнения кодов 9, меньше времени установления аналого-цифрового 12 и цифроаналогового 13 преобразователей, то работает только аналоговый способ поддержания постоянства сформированного на выходе задающего ГЛИН напряжения (т.е. на первый вход компаратора 7 поступает постоянное напряжение, сохраняемое на запоминающем конденсаторе задающего ГЛИН 6). Если же этот интервал времени превышает длительность времени установления, то включается аналого-цифровая схема поддержания постоянства этого напряжения, состоящая из последовательно соединенных аналого-цифрового преобразователя 12, цифроаналогового преобразователя 13 и аналогового ключа 14. Импульс конца цикла генерации Ткц, поступающий на третий вход логического автомата, приводит его в исходное состояние с одновременным обнулением выходного напряжения задающего ГЛИН 6. Тем самым логический автомат (и все устройства в целом) приводится в состояние готовности к следующему циклу генерации.

Схемотехнически логический автомат может быть реализован различным образом (на жесткой логике или как микропрограммный), поэтому подробно раскрывать его структуру нет смысла.

Можно добавить, что описанное устройство фазой привязки генерируемой последовательности импульсов к импульсу внешнего запуска реализовано в новой модификации прецизионного генератора импульсных последовательностей, который разрабатывается на Курском ФГУП "Маяк". Изготовлены опытные образцы этого генератора, которые успешно прошли приемку Заказчика и представлены на межведомственные испытания.

Литература

1. А.с. СССР № 1465950 А1, кл. Н 03 К 3/64. Устройство для парафазной временной привязки импульсов / А.М.Машкин, А.Г.Алаев. Бюл. №10, 1989.

2. А.с. СССР № 1758844 А1, кл. Н 03 К 3/64. Формирователь последовательности импульсов / А.С.Чередниченко, Е.А.Евсеев. Бюл. №32, 1992.

3. Патент РФ № 2042264 С1, кл. 6 Н 03 К 3/72. Управляемый генератор импульсной последовательности / В.И.Беркутов. Бюл. №23, 1995.

4. Генератор импульсов Г5-66. Техническое описание и инструкция по эксплуатации (3.269.085 ТО). Внешторгиздат. 2000.

Устройство фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска, содержащее первое логическое устройство, предназначенное для пропускания тактовых импульсов, начиная с первого импульса, следующего за импульсом внешнего запуска, схему задержки импульса внешнего запуска, селектор первого импульса, задающий и воспроизводящий генераторы линейно изменяющихся напряжений и компаратор, отличающийся тем, что в устройство введены второе логическое устройство, предназначенное для пропускания тактовых импульсов с первого логического устройства без первого импульса, счетчик импульсов, устройство сравнения кодов, запоминающее устройство, логический автомат, предназначенный для отпирания аналогового ключа и последовательной выборки кодов задержек из запоминающего устройства, формирователь выходных синхроимпульсов, аналого-цифровой преобразователь, цифроаналоговый преобразователь и аналоговый ключ, причем на первый, второй и третий входы первого логического устройства поступают соответственно тактовая последовательность импульсов, импульс конца цикла генерации и импульс внешнего запуска, а его выход соединен с входами селектора первого импульса, второго логического устройства и счетчика импульсов, выход селектора первого импульса соединен с вторым управляющим входом задающего генератора линейно изменяющегося напряжения, первый управляющий вход которого соединен с выходом схемы задержки, на вход которой поступает импульс внешнего запуска; второй вход второго логического устройства соединен с выходом схемы задержки импульса внешнего запуска, а выход второго логического устройства - с первым управляющим входом воспроизводящего генератора линейно изменяющегося напряжения, а второй управляющий вход последнего - с выходом компаратора, который также соединен с первым входом формирователя выходных синхроимпульсов; выход воспроизводящего генератора линейно изменяющегося напряжения соединен с вторым входом компаратора, первый вход которого соединен с выходом задающего генератора линейно изменяющегося напряжения; параллельный выход счетчика импульсов соединен с одним из входов устройства сравнения кодов, второй вход которого соединен с выходом запоминающего устройства; выход устройства сравнения кодов соединен с вторым входом формирователя выходных синхроимпульсов и одним из входов логического автомата, второй вход которого соединен с выходом схемы задержки импульса внешнего запуска, а на третий вход поступает импульс конца цикла генерирования последовательности импульсов; первый выход логического автомата соединен с управляющим входом запоминающего устройства, а второй выход - с управляющим входом аналогового ключа, сигнальный вход которого соединен с выходом цифроаналогового преобразователя, а выход соединен с первым входом компаратора, вход цифроаналогового преобразователя соединен с выходом аналого-цифрового преобразователя, а вход последнего - с выходом задающего генератора линейно изменяющегося напряжения.