Модульный масштабируемый коммутатор и способ распределения кадров в сети быстрого ethernet

Иллюстрации

Показать всеИзобретение относится к системам передачи данных, и в частности, к коммутаторам сетей быстрого Ethernet. Техническим результатом является обеспечение гибкости управления распределения данных. Технический результат достигается тем, что коммутатор Ethernet выполнен в виде множества индивидуально программируемых однопортовых модулей связи для доступа к общей распределительной шине (10), при этом каждый однопортовый модуль связи содержит программируемый микроконтроллер (1), выполненный как блок управления доступом к передающей среде Ethernet (MAC), содержащий процессор с сокращенным набором команд (RISC CPU), и логическое устройство (5) распределения кадров данных, предусматривающие обработку в реальном времени и передачу на адресуемые порты назначения кадров данных Ethernet, поступающих на указанный однопортовый модуль связи, процесс передачи является последовательным и осуществляется в режиме "сохранить-и-переслать". 2 н. и 12 з.п. ф-лы, 7 ил.

Реферат

Изобретение относится к модульной, масштабируемой структуре для построения коммутаторов сетей быстрого Ethernet, обращающихся к общей шине распределения данных, и к методу распределения кадров в сети Ethernet в режиме “сохранить-и-переслать” (store-and-forward).

В настоящее время коммутаторы для сетей Ethernet, в особенности соответствующие стандарту IEEE 802.1D, основаны на двух различных подходах к реализации фильтрования и передачи кадров сети Ethernet, a именно:

a) на основе режима “сохранить-и-переслать” (store-and-forward)

b) на основе режима “отсечение-при-пересылке” (cut-through-forwarding).

Коммутаторы, функционирующие в режиме “сохранить-и-переслать ”, как определено стандартом IEEE 802.3 (издание 1998 года), запоминают поступающие кадры данных полностью перед последующим их отправлением. Функции фильтрования выполняются в то время, когда кадры данных получены и/или содержатся в буфере. Такие функции фильтрования включают, например,

- обнаружение адреса и определение порта получения (всегда);

- фильтрация кадров, содержащих ошибки, путем проверки CRC (Cycling Redundancy Check, контроль при помощи циклического избыточного кода) (всегда);

- обнаружение дефектных структур кадров (всегда), адресов, поля данных кадра, частоты передачи кадров (частично или никогда).

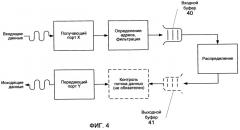

Поток данных в коммутаторах, функционирующих в режиме “сохранить-и-переслать” (а), схематично показан на Фиг.4.

Входной буфер 40 требуется в этой структуре переключателя всегда. Такая буферизация данных серьезно влияет на работу соответствующего переключателя и может приводить состоянию блокировки. Кратковременные перегрузки, возникающие при соответствующей перегрузке принимающего порта, могут быть сбалансированы таким промежуточным звеном буферизации. Реализация распределения приемных портов зависит от соответствующей архитектуры. Одной из возможностей является обеспечение дополнительной буферизации кадров данных, связанных с приемным или передающим портом, как показано в виде дополнительного (необязательного) выходного буфера 41. Недостатком данной стратегии является то, что из-за промежуточного звена буферизации должно учитываться дополнительное время ожидания для всей системы.

Выключатели типа “сохранить-и-переслать” обычно являются системами на основе процессора. Процессор или жесткая логика фильтрует данные множества портов, которые обрабатываются последовательно. Как правило, обработка выполняется копированием кадра данных в общую память коммутатора, к которому также имеет доступ процессор приемного порта.

Согласно стратегии “отсечение-при-пересылке” (b) кадры данных отправляются немедленно после анализа адреса получателя, то есть без промежуточной буферизации. В сравнении с вышеупомянутой стратегией (a) время ожидания минимально, однако никакие сложные функции фильтрации не могут применяться, так как кадры данных передаются в реальном времени для распределения. Содержащие ошибки или искаженные кадры данных также передаются, и соответственно занимают дорогостоящую полосу пропускания в сети.

Фиг.5 и Фиг.6 изображают две архитектуры, работающие согласно принципу разделяемой памяти, при котором все порты имеют доступ к общему полю памяти.

Согласно структуре блока на Фиг.5, центральный компонент 50 ответствен за обработку и отправление всех поступающих кадров данных. Если число портов и/или темп обмена данных увеличивается, центральный компонент 50 может стать узким местом всей архитектуры. Кроме того, общая шина данных 51 обычно сильно загружена, так как все пересылки данных идут через упомянутую шину. Сначала поступающие кадры передаются через общую шину данных 51 в разделяемую память 52, а затем фильтруются и передаются центральным процессором в централизованном компоненте 50. Затем кадры данных распределяются из разделяемой памяти 52 через шину данных 51 к выходным портам 53. Соответственно, каждый кадр данных передается по шине 51 дважды. Это объясняет тот факт, что множитель "2" должен использоваться в следующем уравнении для оценки требуемой полосы пропускания:

Ширина полосы пропускания=число портов ·частота входного потока· 2=3.2 Гбит/сек (для случая 16 портов по 100 Мбит/сек).

Это уравнение справедливо, только если один кадр должен быть отправлен одному выходному порту (unicast). Для широковещательной передачи (multicast, один кадр к множеству выходов) требуемая ширина полосы соответственно увеличивается. Типичный пример прототипа коммутационной структуры Ethernet согласно методу “сохранить-и-переслать ” для 16 полных дуплексных, быстрых Ethernet каналов создан компанией LEVEL ONE, которая использует центральный сетевой процессор типа 1ХР1200.

Фиг.6 показывает другой пример для упомянутого принципа разделяемой памяти, имеющий распределенную архитектуру. Все подмодули 60 работают независимо друг от друга, когда кадры данных должны быть отправлены только в пределах соответствующего узла. Соединение множества элементов блока предусмотрено через общую шину данных 61. Такая распределенная архитектура легче масштабируется, потому что увеличение числа портов 62 может быть осуществлено добавлением соответствующих подмодулей.

Типичный прототип этого типа архитектуры - это семейство GALNETII компании GALILEO TECHNOLOGIES, LTD. Предварительная обработка кадра и фильтрация на базе порт-за-портом (port-by-port-basis) обеспечивается жесткой логикой. Это, однако, ограничено всего лишь несколькими функциями, которые не могут быть изменены или расширены или запрограммированы пользователем. В частности, ограничивающим фактором этого типа архитектуры является ширина полосы высокоскоростного соединения (объединительная плата). Кроме того, из-за ограниченной полосы пропускания объединительной платы нужно учитывать значительное снижение скорости распределения кадров широковещательной передачи, если большее количество портов должно обслуживаться.

Стратегия отсечения при пересылке была далее развита в так называемых переключателях ячеек канала. Входные кадры данных разделяются на блоки данных (ячейки равного размера), тем самым обеспечивая фиксированное время передачи в пределах распределительного узла переключателя. Это дает возможность обеспечить независимость пропускной способности от размера кадра данных, объема передаваемых данных и числа портов. В порте назначения осуществляется дефрагментация и реорганизация ячеек для того, чтобы восстановить первоначальный кадр данных, обычно осуществляемые перекопированием кадров данных в выходной буфер. Однако следует заметить, что распределение данных на основе ячеек не допустимо для приложений, критических с точки зрения безопасности, например в бортовой электронике.

Наконец, что касается прототипов, полностью отличающийся метод распределения кадров данных реализуется в коммутаторах, построенных на базе заказных БИС, как показано на Фиг.7. После анализа целевого адреса или адреса получателя соединение точка-точка устанавливается через коммутационную матрицу. По сравнению с концепцией шины, кратко описанной выше, концепция коммутационной матрицы имеет преимущество, состоящее в том, что она допускает одновременное существование множества соединений, то есть полоса пропускания увеличивается по запросу. Однако это преимущество может быть реализовано только тогда, когда нет необходимости в передаче кадров нескольким портам одновременно (широковещание). В этом случае полное распределение данных блокировано, пока каждый из приемных портов не освободится для получения соответствующего кадра данных.

Типичный пример этого типа архитектуры - семейство LS100/LS101 компании l-Cube. Ltd.

Технология коммутирующей матрицы имеет следующие преимущества:

- Высокая производительность данных, так как множество соединений может существовать одновременно;

- Малые задержки;

- Допускается последовательная коммутация;

- Простота аппаратной реализации, то есть высокая надежность.

Недостатками этой технологии, с другой стороны, являются:

- Требуется большое число выводов (число портов *2* ширина шины интерфейса порта), что означает, что масштабируемость ограничена;

- Отсутствует концентрация полосы пропускания, если кадры должны быть отправлены нескольким портам получателям;

- Отказ элемента коммутационной матрицы влечет полный выход из строя коммутатора;

- Не существует возможности программируемой обработки кадров на базе портов.

Целью изобретения является усовершенствование коммутаторов быстрого Ethernet, а также известных методов распределения кадров данных Ethernet, таким образом, что большая гибкость управления распределением данных при минимальной задержке может быть достигнута на основе концепции “сохранить-и-переслать”.

В соответствии с изобретением, модульная масштабируемая структура для разработки коммутаторов быстрого Ethernet достигается применением высокой гибкости индивидуальной передачи или широковещательной передачи с минимальным числом пакетов, желательно в одном пакете, то есть за один цикл передачи, выполняя, в соответствии с пунктом 1 формулы изобретения, каждый коммутатор Ethernet как индивидуально программируемый модуль с одним коммуникационным портом.

Выгодные варианты конструкции, модификации и усовершенствования являются предметом зависимых пунктов формулы изобретения и объясняются необходимыми ссылками на фигуры в описании.

Метод распределения кадров данных Ethernet, организованный в режиме “сохранить-и-переслать”, характеризуется, в соответствии с пунктом 8 формулы изобретения, построением модульной масштабируемой структуры, состоящей из индивидуально программируемых однопортовых модулей связи, которые организованы для внутренней передачи кадров данных таким образом, что каждый порт после приема, сохранения и проверки целостности кадра данных конкурирует за доступ к высокоскоростной шине обмена данными, для чего используется схема арбитража на основе номера и идентификатора порта. Затем соответствующий кадр данных передается одному или нескольким приемным (выходным) портам, предпочтительно в течение одного цикла кадра данных. Выходные порты независимо решают, согласно статусу связанного выходного буфера, следует принимать или отбрасывать соответствующий переданный кадр данных.

Желательно, чтобы кадры данных, полученные одним модулем связи, были отфильтрованы в реальном времени, по крайней мере, по полосе пропускания, размеру кадра и полям адреса кадра, в частности, управляющим процессором с уменьшенным набором команд (RISC). Это выгодно, если указанный управляющий процесс, в соответствии с изобретением, может быть оперативно изменен в отношении объема фильтрации с помощью перезагружаемых конфигурационных параметров.

Особенно выгодное свойство изобретения состоит в том, что, по крайней мере один из данных однопортовых модулей связи может быть специально назначен, согласно специальным таблицам конфигурации, или до начала, или во время функционирования, для мониторинга потока информации, для того, чтобы осуществлять фильтрацию и захват некоторых кадров данных для анализа потока информации без затрат дополнительной полосы пропускания на соединительной плате.

Еще одно преимущество изобретения состоит в том, что любая необходимая максимальная задержка коммутатора, имеющая значение меньшее, чем заранее заданное, определяется только размером выходной очереди однопортового модуля связи. Определенное преимущество может быть достигнуто при использовании данного изобретения в том случае, если все, или хотя бы один из данных однопортовых модулей связи сконфигурирован для выполнения одной или нескольких административных и/или управляющих функций, например, путем исполнения простого протокола управления сетью (SNMP), управляющей базы данных (МIВ), в особенности для организации структуры Ethernet коммутатора, обеспечивающей необходимые сетевые адреса и/или последовательности уровня приложения, то есть доступные для сетевого уровня через любой однопортовый модуль связи.

Особое преимущество изобретения состоит в том, что структуры данных, полученные от определенного однопортового модуля связи, являются обработанными в реальном времени фильтрованием, по крайней мере относительно полосы пропускания, размера кадра и адресов кадра, путем обработки на сокращенном наборе команд, работающей на сетевом уровне два, то есть на уровне управления доступом к среде передачи (MAC).

В дальнейшем, чтобы избежать избыточных объяснений для хорошо осведомленного читателя, будут использоваться сокращения, которые, однако, объяснены в тексте.

Изобретение, выгодные детали и варианты конструкции его будут описаны ниже со ссылками на сопроводительные фигуры, на которых:

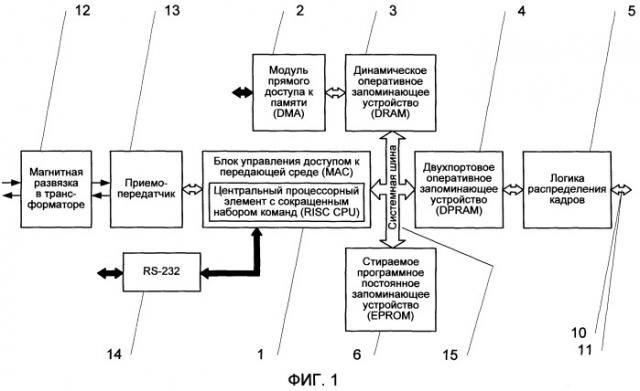

На Фиг.1 изображена функциональная схема однопортового модуля связи согласно изобретению;

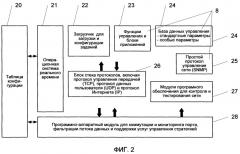

На Фиг.2 показаны блоки взаимодействия функциональных элементов программного обеспечения, как пример для типичных однопортовых модулей связи согласно изобретению;

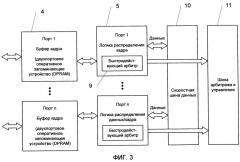

На Фиг.3 показана блок-схема распределения типа “сохранить-и-переслать”;

На Фиг.4 отображен принцип стратегии “сохранить-и-переслать” согласно изобретению (уже объяснен);

На Фиг.5 показана централизованная архитектура для обработки и отправления поступающих кадров данных с использованием разделяемой памяти согласно прототипу (уже объяснено);

На Фиг.6 показана распределенная архитектура построения Ethernet коммутаторов согласно прототипу, включающая независимые подузлы (уже объяснено);

На Фиг.7 показано построение Ethernet коммутатора на базе заказной БИС для соединений типа “точка-точка” с коммутационной матрицей согласно прототипу (уже объяснено).

Структура оборудования типичного примера конструктивного исполнения в соответствии с изобретением и его взаимодействие с типовыми элементами программного обеспечения описаны далее со ссылками на Фиг.1, 2 и 3.

В функциональной схеме блока Фиг.1 сигналы Ethernet подаются, к примеру, через экранированную витую пару на каждое направление с гальваническим разделением посредством магнитной развязки в трансформаторе 12. Далее следует в качестве физического устройства приемопередатчик 13, то есть Ethernet передатчик/приемник, ответственный, среди прочего, за преобразование кода последовательного в параллельный и обратно и за управление кодированием в канале. Приемопередатчик 13 связан с Ethernet блоком управления доступом к передающей среде (MAC) 1, который содержит центральный процессорный элемент с сокращенным набором команд (RISC CPU). В этом блоке MAC+RISC CPU 1, отвечающем за структурирование и обработку поступающих кадров Ethernet, центральный процессорный элемент CPU осуществляет пошаговое исполнение в каждом цикле команды из сокращенного набора. Блок 14 является последовательным интерфейсом согласно протоколу RS-232, с асинхронными стартовым и стоповым битами и контролем четности, соответствующим СОМ интерфейсу персонального компьютера с максимальной скоростью 115 кбид. MAC+RISC CPU 1 связан через системную шину, состоящую, например, из 32 битов, с одной стороны, с двухпортовым оперативным запоминающим устройством (DPRAM) 4, а с другой стороны - с динамическим оперативным запоминающим устройством (DRAM) 3, который взаимодействует с функциональным модулем прямого доступа к памяти (DMA) 2, осуществляющим пересылки память - память независимо от CPU 1. Стираемое программное постоянное запоминающее устройство (EPROM) 6 связано через системную шину с CPU 1, DRAM 3 и DPRAM 4. DPRAM 4 и последующая логика распределения кадров 5, включая быстродействующий арбитр 9, обслуживают однопортовые модули связи, образующие коммутатор Ethernet согласно изобретению на Фиг.3, соединенные, с одной стороны, со скоростной шиной данных 10, а с другой стороны, через быстродействующий арбитр 9 - с шиной арбитража и управления 11.

Типовые функциональные элементы программного обеспечения однопортовых модулей связи согласно изобретению показаны на Фиг.2. Эти функциональные элементы программного обеспечения включают:

- таблицы конфигурации 20, содержащиеся в стираемом постоянном запоминающем устройстве (EPROM), определяющие функции модулей;

- операционная система реального времени 21;

- загрузчик 22 для загрузки конфигурации и заданий, их проверки и связи с блоком обслуживания/пользователя;

- функция управления и блоки приложений 23, которые являются модулем (модулями) программного обеспечения для управления, регистрации и т.д. эксплуатационных параметров;

- Простой протокол управления сети (SNMP) в блоке 25, то есть протокол для передачи / обмена эксплуатационными параметрами;

- База данных управления (MIВ) 24, включая систему для классификации и кодирования эксплуатационных параметров;

- блок стека протоколов 26, необходимый для установления соединения и обмена данными, включая протокол управления передачей (TCP), протокол данных пользователя (UDP) и протокол Интернета (IP);

- множество модулей программного обеспечения 27 для контроля и тестирования сети, а также трафика данных;

- программно-аппаратный модуль 28 для коммутации и мониторинга порта, т.е. для коммутации кадров Ethernet и для отображения обмена данными на порт/канал.

В данном контексте фильтрация потока информации означает фильтрование данных согласно определенным критериям, например размеру кадра, адресам и т.д. Услуги управления стратегией (policing services) относятся к управлению/мониторингу потока данных по отношению к определенной скорости передачи данных и полосе пропускания.

Ниже описан принцип действия.

При использовании программируемых однопортовых модулей связи согласно изобретению для коммутаторов быстрого Ethernet процесс передачи является строго последовательным по своей природе, соответствует дисциплинам экономии нагрузки (work-conserving service disciplines) и организован в режиме “сохранить-и-переслать”, упомянутому выше. Контроль целостности кадра до начала процесса передачи предполагает механизм “сохранить-и-переслать ”. Чтобы обеспечивать максимум определенности, как требуется, например, в бортовом оборудовании, этот проект согласно изобретению предполагает выполнение по строго заданной схеме.

Механизм работает таким образом, что порт после получения и обработки корректного и полного кадра, т.е. после фильтрации потока данных, отработки стратегии, обновляет (внутренний) заголовок этого кадра вместе с соответствующей информацией об отправлении (САМ-вектор) в буфере кадра, то есть в DPRAM 4, так, чтобы эта структура была промаркирована для отправления. Это выполняется скоростной логикой распределения кадров коммутатора 5, которая, как показано на Фиг.1, имеет также доступ к DPRAM 4.

По завершении состязания за доступ к скоростной внутренней шине распределения данных коммутатора 10 логика распределения данных/кадра 5 теперь передает полный кадр одному (unicast) или нескольким (multicast) выходным портам назначения одним пакетом в соответствии с заданным вектором САМ. Любой выходной порт независимо решает, в соответствии со статусом его выходного буфера, который вновь является портом, связанным с DPRAM 4, принимать или отбросить отправляемый кадр в соответствии с требованиями внутренней задержки, объясненными ниже детально.

В качестве примера для коммутатора с 16 портами, скорость передачи по проводам определяет внутреннее время передачи кадра приблизительно в 420 нсек на кадр (то есть 16·148800 кадров минимального размера в секунду=2,4 миллионов кадров в секунду).

Скорость передачи данных по шине распределения данных 10 достаточно высока, чтобы обслуживать все порты ("например, до 16 портов), постоянно передавая 64-байтовые кадры с проводной скоростью. Благодаря структуре однопортового модуля, услуги фильтрования потока данных порта могут легко быть осуществлены в реальном времени, в режиме кадр-за-кадром, что предполагает, что требуемая скорость передачи коммутатора зависит только от скорости передачи по шине 10 (соединительная панель).

Процесс передачи через логику распределения кадров 5 работает следующим образом:

Внутренний механизм распределения данных работает так, что порт, получив и проверив полный фрейм, хранящийся в DPRAM 4, конкурирует за доступ к скоростной шине распределения данных 10 модуля. Децентрализованные скоростные арбитры 9, установленные в узле логики распределения кадров 5 каждого порта модуля связи, согласно схеме справедливого арбитража (fair arbitration scheme) предоставляет доступ на шину 10 в соответствии с номером порта или его идентификатором. Затем порт передает кадр одному (unicast) или нескольким (multicast) выходным портам одним пакетом. Каждый выходной порт, в соответствии со статусом его буфера, независимо решает, принять или отбросить передаваемый кадр.

В соответствии с изобретением максимальное время ожидания может быть конфигурироваться, как объяснено ниже:

Время ожидания определено как разность между временем прибытия первого бита кадра и временем отправления первого бита последнего экземпляра того же самого кадра из переключателя, где термин “последний экземпляр” относится к широковещательной пересылке, когда копируемые кадры могут покидать коммутатор в разные моменты времени.

Как описано ниже, любая дополнительная задержка из-за внутренней обработки данных коммутатора и функций отправления равна нулю, и любое требуемое максимальное время ожидания меньше чем tbd <так в оригинале - прим. перев.> миллисекунд определяется размером выходной очереди коммутатора, размещенной только в DPRAM 4.

Пример:

Требуемое максимальное время ожидания должно быть 1 мсек. Для кадров с 64 байтовыми MAC размерами данных размеры выходных очередей должны быть рассчитаны такими, чтобы они могли содержать 149 кадров, в точном соответствии со скоростью передачи в среде 100 Мбит/сек с межкадровым интервалом 96 битов. Для кадров, имеющих длину большую, чем 64 байта, число кадров, хранящихся в выходных очередях, соответственно уменьшается. Это происходит вследствие того, что число кадров, которые могут быть переданы при установленной скорости в среде 100 Мбит/сек, в пределах интервала TR=1 мсек уменьшается при увеличении длины кадров.

В результате выходные очереди DPRAM 4 имеют емкость

149*(размер внутреннего блока сообщения для 64-байтовых кадров) [байтов].

В зависимости от статуса/уровня выходной очереди (выходных очередей), любой порт независимо решает, принимать или отказаться от кадра, отправленного внутренней логикой распределения данных. Размер выходной очереди однопортового модуля связи конфигурируется программным обеспечением или загрузкой параметров конфигурации в процессе работы.

Далее описаны программируемые функции:

Возможность мониторинга потока данных: полагая, что число однопортовых модулей равно n, один или несколько из них могут выполнять эту задачу. Основная цель такого порта контроля состоит в том, чтобы фильтровать и захватывать некоторые кадры для анализа потока.

Порт контроля имеет особую таблицу конфигурации, которая позволяет выбирать, какой MAC адрес назначения среди группы входных портов, кроме самого порта контроля, должен быть перекопирован на выход порта контроля. Таблица конфигурации 20 разрешает выбирать один или более MAC адресов, которые достигают коммутатора, и отсылать их через порт контроля.

Все порты, не назначенные на мониторинг потока данных, постоянно посылают копию каждого полученного годного кадра в порт контроля, не занимая дополнительную полосу пропускания высокоскоростной шины передачи данных 10. Это обеспечивается благодаря встроенным широковещательным свойствам шины данных, описанным выше. Таблица конфигурации порта контроля определяет, какой из этих кадров должен быть отобран для передачи, например, по MAC адресу назначения. Все другие кадры игнорируются. Поэтому изменения в конфигурации мониторинга не влияют на таблицы передачи, связанные со всеми другими портами.

Способности фильтрования/стратегии потока: Каждый полученный кадр может быть оценен относительно определенных прикладных параметров, записанных в таблице конфигурации в накопителе EPROM 6. Поскольку функции фильтрования/стратегии осуществляются программно из-за доступности одного MAC+RISC CPU 1 на каждый порт, то любой алгоритм может применяться в зависимости от специфических прикладных требований. В бортовом оборудовании важные услуги фильтрования расширяются на (но не ограничиваются этим):

- полосу пропускания и контроль дрожания (jitter);

- контроль длины кадра;

- контроль адреса кадра;

- контроль данных кадра, и другие.

Например, контроль полосы пропускания и контроль дрожания могут быть выполнены благодаря введению величины бюджета, ассоциированной с кадром, которая базируется на следующих параметрах:

- интервал полосы пропускания (выраженный в секундах), связанный с определенным MAC адресом,

- максимальное значение величины бюджета согласно значению дрожания, выраженному в секундах, ассоциированное с определенным MAC адресом.

Основной концепцией и целью описанной архитектуры коммутатора согласно изобретению является обеспечение оптимальной полосы пропускания и производительности обработки данных по всем функциональным блокам между любой парой портов входа и выхода, так, чтобы могла быть достигнута установившаяся (sustained) проводная скорость. Это включает производительность функции фильтрования/стратегии потока данных порта, главным образом достигнутой (как пример) 32-битовыми MAC+RISC CPU 1, выделенными каждому порту.

Можно привести пример для оценки работы:

Максимальная нагрузка на входной порт коммутатора образуется при приеме кадров минимального размера, к примеру, 64 байтов поля данных MAC, соответствующих 18 байтам данных пользователя с применением протокола UDP/IP, с минимальным межкадровым промежутком в 12 байтов. При скорости передачи информации в среде, к примеру, 100 Мбит/сек, это дает 149 кадров/мсек. Согласно структуре кадра MAC no стандарту IEEE 802.3 и без признака заголовка по стандарту 802.1 p/1Q, имеющего размер 4 байта, полный размер MAC кадра составляет 84 байта.

Устройства Ethernet MAC, установленные в каждом порту коммутатора, способны сохранять не только единицу данных MAC протокола, но также и так называемый внутренний блок сообщения, который также включает CRC поле, MAC адреса источника и назначения, поле типа/длины, также как и другую специальную информацию, например, метки времени, статус, указатели, вектор САМ и т.д., используемую для управления коммутаторами. В худшем случае минимальный размер внутреннего блока сообщений состоит из 128 байтов (=32·4 байта, то есть 32 битовое слово <так в оригинале, прим. перев.>), мощность обработки RISC процессора, необходимая для управления полосой пропускания, то есть стратегии расчета бюджета, так же как и для обновления блока сообщений, достигнет нижеследующего значения инструкций в секунду (IPS):

Оставшаяся типовая функция фильтрации потока, то есть фильтрация кадров по MAC адресу назначения, может быть оценена в дополнительные ~2.25 MIPS, таким образом, полная нагрузка на процессор достигает ~10 MIPS для порта, работающего на полной проводной скорости и минимальным размером кадра. При использовании одного MAC+RISC процессора 1 на один порт при 10 MIPS, фильтрация кадров в реальном времени в режиме кадр-за-кадром, может быть обеспечена даже на полной проводной скорости.

Время, необходимое для фильтрации потока данных одного кадра, будет составлять

10 MIPS/149·103 кадров ≈67 IPS/кадр, что дает на 1,34 мксек при времени цикла процессора 20 нсек, то есть для 50-мегагерцового RISC процессора 1; при 33 мегагерцах время вычисления достигнет 67·33 нсек=2.2 мксек.

Полученные кадры передаются в DRAM 3 контроллером прямого доступа к памяти, входящего в состав MAC+RISC CPU 1. На полной проводной скорости кадры с 64 байтами данных MAC имеют продолжительность передачи кадра ~5.76 мксек, за которым следует интервал 0.96 мсек для 12 октетов межкадрового промежутка. Это дает полное минимальное время передачи 6.72 мксек на один кадр.

Таким образом, используется только 1.34/6.72=20% (для 2.2/6.72=33%, соответственно) минимального времени передачи кадра, что фактически означает, что любая дополнительная задержка из-за внутренней обработки данных коммутатора и функции отправления равна нулю, и требуемое максимальное время ожидания меньше чем 1 мсек определяется только длиной выходной очереди коммутатора.

Это утверждение справедливо только при времени t0=0 для кадра, полностью переданного и сохраненного в DPRAM 4. Затем немедленно начинается процесс фильтрования кадра и выполняется параллельно с процессом получения следующего кадра в MAC+RISC CPU 1 (действие трубопровода).

Далее описаны возможности функции управления сетью:

Модульная архитектура коммутатора согласно изобретению обеспечивает возможность доступа к внутренней открытой информации через простой протокол управления сети (SNMP), к базе информации управления (MIB) путем, например, использования протокола данных пользователя/протокола Интернет (UDP/IP) и простого протокола управления сетью на MAC+RISC CPU 1 любого порта, что обозначено ссылкой 8 на Фиг.2. Интерфейс организован так, что SNMP протокол используется для получения этой информации.

Для того, чтобы внутренней трафик SNMP не занимал слишком широкую часть полосы пропускания соединительной платы коммутатора, что может снизить быстродействие, т.е. увеличить время ожидания, вместо этого может использоваться шина разделяемой памяти прямого интерфейса памяти (DMI) 2. Блок DMI 2 обеспечивает разделение, к примеру, 16-битовой шины и обеспечивает обмен данными, хранящимися в локальной памяти каждого процессора, то есть DRAM 3, EPROM 6 и DPRAM 4.

Далее, в случае отказа порта в рамках его коммутационных услуг, этот подход все еще позволяет контролировать MAC+RISC CPU 1, получая информацию о статусе/ошибках на соответствующем дефектном порту, который не будет обеспечивать, к примеру, смешанный поток данных с информацией о статусе на соединительной плате.

1. Модульная масштабируемая архитектура коммутатора быстрого Ethernet, отличающаяся тем, что коммутатор Ethernet выполнен в виде множества индивидуально программируемых однопортовых модулей связи для доступа к общей распределительной шине (10), при этом каждый однопортовый модуль связи содержит программируемый микроконтроллер (1), выполненный как блок управления доступом к передающей среде Ethernet (MAC), содержащий процессор с сокращенным набором команд (RISC CPU), и логическое устройство (5) распределения кадров данных, предусматривающие обработку в реальном времени и передачу на адресуемые порты назначения кадров данных Ethernet, поступающих на указанный однопортовый модуль связи.

2. Архитектура коммутатора быстрого Ethernet по п.1, отличающаяся тем, что каждый индивидуально программируемый однопортовый модуль связи содержит двухпортовый буфер кадров (4), выполненный таким образом, чтобы взаимодействовать, с одной стороны, с данным программируемым микроконтроллером (1) и, с другой стороны, с указанным логическим устройством (5) распределения данных таким образом, что принятый верный кадр данных обновляется, по крайней мере, в части информации о передаче (САМ вектор) в указанном буфере кадров (4), чтобы быть пригодным для передачи через упомянутую шину распределения данных (10).

3. Архитектура коммутатора быстрого Ethernet по п.2, отличающаяся тем, что содержит логическое устройство (9) арбитража, организованное так, что оно выполнено децентрализованным и содержится в каждом из упомянутых индивидуально программируемых однопортовых модулей связи, при этом указанное устройство взаимосвязано с соответствующим одним из логических устройств (5) распределения кадров данных для предоставления доступа верных кадров данных к упомянутой шине распределения данных (10) согласно справедливому распределению прав доступа и схеме сигналов управления, основанной на нумерации портов или их идентификации.

4. Архитектура коммутатора быстрого Ethernet по п.1, отличающаяся тем, что упомянутый программируемый микроконтроллер выполнен с возможностью доступа для индивидуального программирования через интерфейсный блок.

5. Архитектура коммутатора быстрого Ethernet по п.4, отличающаяся тем, что упомянутый интерфейсный блок является интерфейсом RS-232.

6. Архитектура коммутатора быстрого Ethernet по п.1, отличающаяся тем, что дополнительно содержит прямой интерфейс памяти (DMI 2), связанный с DRAM (динамическое оперативное запоминающее устройство) (3) для осуществления прямых операций память-память и/или обмена управляющими данными и/или информацией о состоянии в случае отказа в логическом устройстве (5) распределения кадров данных или шины данных (10).

7. Способ распределения кадров данных Ethernet в режиме “хранить-и-отправлять” с применением модульной масштабируемой архитектуры индивидуально программируемых однопортовых модулей связи, включающий следующие операции: обеспечение указанной модульной масштабируемой архитектуры индивидуально программируемых однопортовых модулей связи, организованных для внутреннего распределения кадров данных таким образом, что каждый порт после приема, сохранения и проверки кадра данных на целостность конкурирует за доступ к высокоскоростной шине распределения данных согласно справедливой схеме арбитража, основанной на нумерации или идентификации портов, передачу соответствующего кадра данных, по меньшей мере, на один выходной порт в течение определенного числа циклов кадра данных, и осуществление операции принятия решения таким образом, что каждый выходной порт независимо друг от друга решает в соответствии со статусом его выходных буферов принять или отклонить соответствующий передаваемый кадр данных.

8. Способ по п.7, отличающийся тем, что упомянутым числом циклов кадра данных является один и только один, независимо от числа выходных портов, одновременно обслуживаемых упомянутым индивидуально программируемым однопортовым модулем связи.

9. Способ по п.7, в котором кадры данных, получаемые упомянутым индивидуально программируемым однопортовым модулем связи, обрабатываются в реальном времени путем фильтрации, по меньшей мере, по ширине полосы, размеру кадра и адресам кадра посредством управляющего процесса, на сетевом уровне 2 (уровень доступа к сети - MAC) с использованием сокращенного набора команд.

10. Способ по п.9, отличающийся тем, что упомянутый управляющий процесс является изменяемым с точки зрения объема фильтрации с помощью перезагружаемых конфигурационных параметров.

11. Способ по п.7, отличающийся тем, что по меньшей мере один из упомянутых индивидуально программируемых однопортовых модулей связи может быть назначен специальными таблицами конфигурации до и/или в течение времени работы для выполнения мониторинга потока данных, чтобы обеспечить фильтрацию и захват некоторых кадров данных для анализа потока данных.

12. Способ по любому из предшествующих пунктов, отличающийся тем, что любое требуемое значение задержки переключения, которое меньше заранее заданного времени, определяется только длиной выходной очереди индивидуально программируемого однопортового модуля связи.

13. Способ по п.12, отличающийся тем, что по меньшей мере один индивидуально программируемый однопортовый модуль связи сконфигурирован для выполнения по меньшей мере одной функции администрирования/управления.

14. Способ по п.13, отличающийся тем, что указанная, по меньшей мере, одна функция администрирования/управления осуществляется простым протоколом управления сетью (SNMP) и/или базой данных управления (MIB) для представления доступа к информации об архитектуре коммутатора Ethernet, обеспечивая соответствующие сетевые адреса и уровень приложения (последовательно для уровня сети 7), доступные через любой индивидуально программируемый однопортовый модуль связи.