Устройство фазовой автоподстройки генератора импульсов

Иллюстрации

Показать всеИзобретение относится к области генерирования импульсов с автоматической подстройкой их фазы. Достигаемый технический результат - расширение частотного диапазона входных сигналов и уменьшение искажений генерируемых импульсов. Устройство содержит мультифазный генератор импульсов, селектор импульсов, логический фильтр, реверсивный сдвигающий регистр, элемент ИЛИ-НЕ. 3 з.п. ф-лы, 2 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к технике генерирования импульсов с автоматической подстройкой их фазы, в частности к устройствам фазовой синхронизации с использованием мультифазного генератора импульсов.

Уровень техники

Для фазовой синхронизации генераторов импульсов применяются устройства с цифровым управлением фазой генерируемых импульсов, в частности устройства синхронизации с субквантованием шкалы отсчета фазы на основе мультифазного генератора импульсов. В таких устройствах благодаря дополнительному разделению периода генератора импульсов на множество равных интервалов, составляющих шаг квантования фазы, рабочая тактовая частота снижается во столько раз, сколько выходов имеет мультифазный генератор импульсов. Это позволяет резко снизить требования к быстродействию элементной базы устройства.

Известна цифровая петля фазовой автоподстройки [1], содержащая опорный кварцевый генератор и цепь задержки с отводами, к которым присоединены входы регистра для записи значений сигналов на отводах. Выходной мультиплексор, также соединенный с отводами цепи задержки своими информационными входами, выбирает сигнал с одного из отводов под управлением цифрового контроллера на основании измеренной фазовой разности. Недостаток данного аналога состоит в невысокой точности синхронизации, так как не обеспечивается равномерность шагов квантования фазы в пределах опорного периода из-за возможного отличия полного времени задержки цепи задержки от длительности опорного периода.

Тот же принцип селекции выходного импульса из множества смещенных по фазе копий основного сигнала генератора импульсов использует устройство фазовой синхронизации [2]. Данный аналог состоит из мультифазного опорного генератора с выходным мультиплексором и блоков - регистра, шифратора, вычитателя и накапливающего сумматора, образующих цифровой сигнал управления мультиплексором на основании цифрового отсчета и преобразования текущей фазовой разности входного и выходного импульсов. Устройство отличается расширенной частотной полосой синхронизации, точность синхронизации определяется шагом квантования фазы, равным Δϕ=2π/N (N - число фаз мультифазного генератора импульсов). Недостатком устройства является его сложность.

Известно также устройство синхронизации [3], состоящее из мультифазного генератора импульсов в виде многоотводной линии задержки с обратной связью через первый мультиплексор и инвертор, второго мультиплексора с элементом ИСКЛЮЧАЮЩЕЕ ИЛИ на выходе, первого и второго реверсивных счетчиков импульсов, управляющих мультиплексорами, и фазочастотного компаратора. В этом устройстве осуществляется одновременно автоподстройка частоты мультифазного генератора импульсов с помощью первых счетчика и мультиплексора и автоподстройка фазы выходного сигнала с помощью вторых счетчика и мультиплексора. Недостатками данного аналога являются сложность структуры и ограниченные функциональные возможности, поскольку ввиду присущего ему эффекта частотной дискриминации устройство нельзя использовать с нерегулярными кодовыми входными сигналами.

Из известных аналогов наиболее близким по технической сущности к настоящему изобретению является устройство фазовой автоподстройки генератора импульсов [4]. Данное устройство, выбранное за прототип, состоит из мультифазного генератора импульсов, выходами подключенного к соответствующим сигнальным входам селектора импульсов в виде мультиплексора, выход которого соединен с выходным зажимом устройства. Кроме того, имеется реверсивный счетчик импульсов, сигнальным входом связанный с входным зажимом, входом управления направлением счета - с выходным зажимом, а выходами подключенный к соответствующим адресным входам мультиплексора.

При ограниченной частотной полосе синхронизации устройство отличается простой структурой. Однако время задержки при выборе выходного импульса мультифазного генератора импульсов в качестве выходного сигнала устройства в устройстве-прототипе довольно велико. Суммарное время задержки включает, в частности, время задержки распространения переноса по межразрядным цепям реверсивного счетчика импульсов и время дешифрирования адреса в мультиплексоре. В течение этого времени состояние выходного сигнала устройства не определено, то есть имеется зона нечувствительности, которая особенно проявляется при высокой частоте входных сигналов. Таким образом, недостатком устройства-прототипа является ограниченный сверху диапазон рабочей частоты входных сигналов и возможные искажения выходных импульсов ввиду зоны нечувствительности при переключении мультиплексора в процессе фазовой автоподстройки.

Сущность изобретения

Целью настоящего изобретения является расширение частотного диапазона входных сигналов и уменьшение искажений генерируемых импульсов. Указанная цель достигается путем специального исполнения селектора импульсов (мультиплексора), который управляется реверсивным сдвигающим регистром, и введения в устройство логического фильтра. Направление перемещения единственной "единицы" по разрядам реверсивного сдвигающего регистра задается фазовым отношением входного и выходного сигналов устройства. Положение "единицы" в разрядной сетке определяет порядковый номер выхода мультифазного генератора импульсов (МГИ), импульс с которого выбирается селектором импульсов в качестве выходного сигнала устройства фазовой автоподстройки. За счет этого фаза выходного сигнала приближается к фазе входного сигнала, а в дальнейшем отслеживает ее. Поскольку коррекция фазы выходного сигнала производится только в моменты поступления входных сигналов, то эффект частотной дискриминации исключается. Поэтому устройство способно работать с нерегулярными сигналами данных, восстанавливая синхросигналы, необходимые для декодирования данных. Логический фильтр устраняет искажения выходных импульсов устройства, проявляющиеся в прототипе как короткие ложные импульсы в момент переключения селектора импульсов.

С этой целью в цифровое устройство фазовой синхронизации, содержащее МГИ, выходами подключенный к соответствующим сигнальным входам селектора импульсов, дополнительно введены реверсивный сдвигающий регистр, элемент ИЛИ-НЕ и логический фильтр. При этом тактовый вход реверсивного сдвигающего регистра подключен к входному зажиму устройства, его вход управления направлением сдвига присоединен к выходному зажиму устройства, а объединенные сигнальные входы для последовательной записи информации при сдвиге вправо и влево соединены с выходом элемента ИЛИ-НЕ. Выходы сдвигающего регистра и выход элемента ИЛИ-НЕ подключены к соответствующим управляющим входам селектора импульсов. Вновь введенный логический фильтр, в свою очередь, включен между выходом селектора импульсов и выходным зажимом устройства.

При 2n выходов МГИ реверсивный сдвигающий регистр должен быть (2n-1) - разрядным, а селектор импульсов иметь по 2n управляющих и сигнальных входов.

В предпочтительном варианте исполнения МГИ выполняется в виде последовательной цепи n элементов задержки, причем выход каждого элемента задержки подключен также к входу соответствующего буферного элемента с прямым и инверсным выходами. Последовательная цепь элементов задержки замкнута в кольцо, для чего инверсный выход буферного элемента, соединенного с выходом n-го элемента задержки, подключен к входу первого элемента задержки. Множество прямых выходов всех буферных элементов образуют одну группу n выходов МГИ, а множество их инверсных выходов - другую группу n выходов МГИ. Элементами задержки могут служить секции многоотводной электромагнитной линии задержки, однако предпочтительно применение электронных элементов задержки, допускающих ручное и электронное регулирование времени задержки.

Селектор импульсов может быть построен на 2n элементах И, выходами подключенных к соответствующим входам элемента ИЛИ. При этом первые входы всех элементов И служат сигнальными входами, а вторые входы всех элементов И - управляющими входами селектора импульсов, выходом которого является выход элемента ИЛИ.

Логический фильтр игнорирует входные импульсы с длительностью, меньшей времени задержки элемента задержки, входящего в состав МГИ. Он может состоять из инерционного звена, например RC-цепи первого порядка с соответствующей постоянной времени, нагруженного на триггер Шмитта.

Перечень фигур чертежей

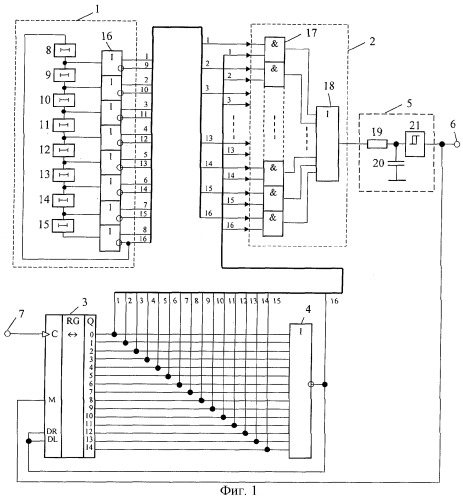

На фиг.1 представлена функциональная электрическая схема устройства фазовой автоподстройки генератора импульсов в соответствии с настоящим изобретением.

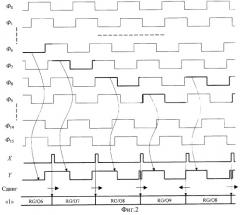

На фиг.2 показаны временные диаграммы сигналов, иллюстрирующие принцип действия устройства фазовой автоподстройки генератора импульсов, схема которого изображена на фиг.1.

Сведения, подтверждающие возможность осуществления изобретения.

Схема устройства фазовой автоподстройки генератора импульсов (фиг.1) содержит МГИ 1, 2n выходов которого подключены к 2n сигнальным входам селектора 2 импульсов. В описываемом примере осуществления изобретения на схеме для определенности принято n=8. Селектор 2 импульсов своими 2n управляющими входами соединен с соответствующими выходами (2n-1) - разрядного реверсивного сдвигающего регистра 3 и выходом элемента 4 ИЛИ-НЕ. Входы элемента 4 ИЛИ-НЕ присоединены к выходам указанного регистра 3. В устройстве имеется также логический фильтр 5, входом соединенный с выходом селектора 2 импульсов, а выходом - с выходным зажимом 6. При этом тактовый вход С реверсивного сдвигающего регистра 3 присоединен к входному зажиму 7, его вход М управления направлением сдвига - к выходному зажиму 6, а объединенные входы DR и DL последовательной записи информации при сдвиге соответственно вправо и влево - с выходом элемента 4 ИЛИ-НЕ.

МГИ 1 в представленном варианте осуществления изобретения выполнен в виде кольца из n элементов 8...15 задержки, замкнутого через инвертор. Выход каждого элемента 8...15 задержки подключен к входу своего буферного элемента, все буферные элементы, имеющие прямой и инверсный выходы, показаны на фиг.1 единым блоком 16. Элементы задержки передают фронт и спад своего входного импульса с одинаковой задержкой, ими могут служить секции многоотводной электромагнитной линии задержки или электронные элементы задержки. Электронные элементы задержки предпочтительны для интегрального исполнения устройства и допускают ручное либо автоматическое регулирование времени задержки с целью стабилизации частоты импульсов МГИ 1. Первую половину выходов МГИ 1, перекрывающих диапазон 0...π в фазовом измерении периода импульсов МГИ 1 образует множество прямых выходов буферных элементов 16, вторую половину выходов в диапазоне 0...2π - множество их инверсных выходов. Кольцо из элементов 8...15 задержки замкнуто путем подключения входа элемента 8 задержки к инверсному выходу буферного элемента из блока 16, связанного с выходом элемента 15 задержки.

Селектор 2 импульсов может быть выполнен по общеизвестной схеме в виде двухступенчатой структуры из элементов И, показанных единым блоком 17, и элемента 18 типа ИЛИ, собирающего выходы элементов И на общий выход селектора 2 импульсов.

Логический фильтр 5 может состоять из каскадного соединения инерционного звена в виде RC-фильтра нижних частот 19, 20 и триггера Шмитта 21. Постоянная времени RC-фильтра нижних частот 19, 20 выбирается соизмеримой с временем задержки одного из элементов 8...15 задержки.

Необходимо отметить, что схемы описанных выше вариантов функциональных блоков не являются единственно возможными и допускают другое исполнение в зависимости от элементной базы и рабочей частоты устройства.

Работа устройства иллюстрируется временными диаграммами сигналов, показанными на фиг.2.

МГИ 1 непрерывно вырабатывает на своих 2n выходах импульсы типа "меандр", следующие с периодом Т=2nΔt, где Δt - время задержки одного из одинаковых элементов 8...15 задержки, входящих в состав МГИ 1. Импульс на каждом следующем по порядку выходе задержан относительно импульса на предшествующем выходе на время Δt. Множество импульсов, вырабатываемых на прямых выходах буферных элементов 16, располагаются в диапазоне от 0 до π периода (диаграммы Ф0...Ф7 на фиг.2) и образуют первую группу выходных импульсов МГИ 1. Множество импульсов, вырабатываемых на инверсных выходах буферных элементов 16 и представляющих собой инверсию импульсов первой группы выходов МГИ 1, образуют вторую группу выходных импульсов МГИ 1 и перекрывают фазовый диапазон от π до 2π (диаграммы Ф8...Ф15 на фиг.2).

Импульсы со всех 2n выходов МГИ 1 одновременно поступают на первые входы соответствующих 2n элементов 17 типа И в селекторе 2 импульсов, на вторые входы этих элементов поступают логические уровни с соответствующих (2n-1) выходов реверсивного сдвигающего регистра 3 и выхода элемента 4 ИЛИ-НЕ. Реверсивный сдвигающий регистр 3 и элемент 4 ИЛИ-НЕ, выходом подключенный к объединенному входу DR+DL последовательной записи информации регистра 3, образуют распределитель импульсов с 2n выходами. В любой момент времени только на одном из 2n выходов такого распределителя импульсов присутствует уровень логической "1", на остальных выходах при этом сохраняется уровень "0". Направление сдвига информации в регистре 3 задается логическим уровнем напряжения по его входу М управления направлением сдвига, поступающим с выходного зажима 6 устройства. Если на управляющем входе М присутствует уровень "0", то происходит сдвиг информации влево, если уровень "1", то - вправо. При сдвиге информации в любом направлении, пока на одном из выходов регистра 3 имеется "1", на выходе элемента 4 ИЛИ-НЕ остается уровень логического "0". Поэтому в момент прихода тактового импульса на вход С регистра 3 в освобождающийся в процессе сдвига левый (при сдвиге вправо) или правый (при сдвиге влево) разряд регистра 3 записывается "0". Когда все разряды регистра 3 обнуляются, уровень "1" появляется на выходе элемента 4 ИЛИ-НЕ. В следующем после этого такте "1" записывается в крайний разряд регистра 3, что приводит к возвращению исходного уровня "0" на выход элемента 4 ИЛИ-НЕ.

На входной зажим 7 поступают входные сигналы Х (фиг.2), интервал между которыми (единичный интервал τX) кратен в среднем периоду Т0 импульсов МГИ 1. В рассматриваемом примере осуществления устройства для достижения и удержания режима синхронизма значение τX не должно отличаться от значения Т0 более, чем на Δt. Входные сигналы могут быть нерегулярными, если представляют собой информационный поток битов.

Пусть в исходном состоянии в распределителе импульсов, состоящем из реверсивного сдвигающего регистра 3 и элемента 4 ИЛИ-НЕ, логическая "1" присутствует на выходе регистра 3 с порядковым номером "6" (RG/Q6 - диаграмма позиции "1" на фиг.2). Тогда селектор 2 импульсов, в котором открыт соответствующий вентиль - элемент типа И из блока 17, пропускает через элемент 18 ИЛИ на свой выход импульс Y (фиг.2) с выхода Ф6 МГИ 1.

Режиму синхронизма в описываемом устройстве соответствует совпадение во времени фронтов входного Х и выходного Y сигналов на зажимах 7 и 6 соответственно. Допустим, как показано в начале диаграммы (фиг.2), что фронт выходного сигнала Y на выходном зажиме 6 появляется прежде, чем на входной зажим 7 поступает фронт входного сигнала X. Тогда фронт первого входного импульса Х приходится на высокий уровень логической "1" выходного импульса Y, который служит сигналом управления направлением сдвига в реверсивном сдвигающем регистре 3 и определяет сдвиг его информации вправо. В результате уровень логической "1" перемещается из разряда RG/Q6 в разряд RG/Q7 (фиг.2). После этого селектор 2 импульсов начинает через соответствующий элемент И блока 17 и элемент 18 ИЛИ передавать на выходной зажим 6 импульс Ф7 МГИ 1.

Если фронт следующего сигнала на входном зажиме 7 (X) вновь приходится на высокий уровень выходного сигнала Y на выходном зажиме 6, то уровень "1" оказывается уже на выходе Q8 регистра 3. Как видно непосредственно из диаграммы, сдвиг вправо "1" по разрядам регистра 3 приводит к смещению вправо по оси времени сигнала Y в следующем такте. Таким образом осуществляется коррекция фазы выходного сигнала Y в направлении компенсации фазовой ошибки. Благодаря направленному перебору селектором 2 импульсов с выходов МГИ 1, с каждым входным сигналом Х на зажиме 7 происходит приближение к нему по фазе выходного сигнала Y на зажиме 6. Так продолжается до тех пор, пока фронт очередного входного сигнала Х не придется уже на низкий уровень логического "0" выходного сигнала Y. Тогда (см. фиг.2) направление сдвига в регистре 3 изменится на противоположное, что обусловит коррекцию фазовой ошибки в необходимом направлении.

После этого устройство работает в режиме синхронизма, в котором поддерживается синфазность выходного и входного сигналов (совпадение во времени их фронтов) с погрешностью не более Δt по времени, или π/n в фазовом исчислении.

Для пояснения роли логического фильтра 5 выходные сигналы Y на фиг.2 показаны такими, какими они получаются непосредственно на выходе селектора 2 импульсов. В режиме синхронизма при переключении селектора 2 импульсов возможен "дребезг" фронта сигнала на его выходе. Благодаря сглаживанию фронтов сигналов RC-фильтром 19, 20 и гистерезисной передаточной характеристике триггера 21 Шмитта в логическом фильтре 5. результирующие сигналы на выходном зажиме 6 не имеют "дребезга". Время задержки логического фильтра 5 на динамике работы устройства не отражается.

Литература

1. Патент ЕПВ №0185779, кл. H 03 L 7/00.

2. Патент РФ №2119717, кл. H 03 L 7/00.

3. Патент РФ №2167493, кл. H 03 L 7/00.

4. Чулков В.А. Дискретно-фазовая автоподстройка в устройстве синхронизации данных. - Вопросы радиоэлектроники, сер. ЭВТ, 1990, вып.13, с.71, рис.1 (прототип).

1. Устройство фазовой автоподстройки генератора импульсов, содержащее мультифазный генератор импульсов, выходами подключенный к соответствующим сигнальным входам селектора импульсов, отличающееся тем, что в него дополнительно введены включенный между выходом селектора импульсов и выходным зажимом устройства логический фильтр, реверсивный сдвигающий регистр и элемент ИЛИ-НЕ, входами подключенный к соответствующим выходам реверсивного сдвигающего регистра, а выходом - с объединенными сигнальными входами последовательной записи информации реверсивного сдвигающего регистра, причем выходы реверсивного сдвигающего регистра и выход элемента ИЛИ-НЕ присоединены к соответствующим управляющим входам селектора импульсов, вход управления направлением сдвига реверсивного сдвигающего регистра подключен к выходному зажиму устройства, а его тактовый вход - к входному зажиму устройства.

2. Устройство фазовой автоподстройки генератора импульсов по п.1, отличающееся тем, что мультифазный генератор импульсов имеет 2n выходов и выполнен в виде последовательной цепи n элементов задержки, выход каждого элемента задержки подключен также к входу соответствующего буферного элемента с прямым и инверсным выходами, при этом инверсный выход буферного элемента, соединенного с выходом n-ого элемента задержки, подключен к входу первого элемента задержки, множество прямых выходов всех буферных элементов образуют одну группу n выходов мультифазного генератора импульсов, а множество их инверсных выходов - другую группу n выходов мультифазного генератора импульсов.

3. Устройство фазовой автоподстройки генератора импульсов по п.1, отличающееся тем, что селектор импульсов включает 2n элементов И, выходами подключенных к соответствующим входам элемента ИЛИ, при этом первые входы всех элементов И служат сигнальными входами, а вторые входы всех элементов И - управляющими входами селектора импульсов, выходом которого является выход элемента ИЛИ.

4. Устройство фазовой автоподстройки генератора импульсов по п.1, отличающееся тем, что логический фильтр представляет собой триггер Шмитта с входным инерционным звеном.