Устройство адаптивной кодовой цикловой синхронизации

Иллюстрации

Показать всеУстройство адаптивной кодовой цикловой синхронизации относится к системам передачи дискретной информации и может быть использовано для цикловой синхронизации корректирующих кодов, в частности помехоустойчивых каскадных кодов. Достигаемый технический результат - повышение помехоустойчивости. Устройство адаптивной кодовой цикловой синхронизации содержит регистр задержки (1), узел обнаружения ошибок (2), блок дешифраторов (10), счетчик (11), пороговый блок (21), генератор синхронизирующей последовательности (18), выходной сумматор по модулю два (12), оперативное запоминающее устройство (15), блок сумматоров по модулю два (16), блок сравнения номеров (13), полный сумматор (19), счетчик синхронизации (17), сумматор ошибок (14), преобразователь кода (20). Узел обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффмена (3,4) и регистра синдрома (5), при этом каждый фильтр Хаффмена состоит из регистра (6/7) и сумматора по модулю два (8/9). 1 ил.

Реферат

Изобретение относится к системам передачи дискретной информации и может быть использовано для цикловой синхронизации корректирующих кодов, в частности помехоустойчивых каскадных кодов.

В устройствах кодовой цикловой синхронизации синхронизирующие признаки, определяющие начало (конец) помехоустойчивого кода, передают в самом помехоустойчивом коде. Для цикловой синхронизации не требуется передача в канале связи дополнительных символов, а используется избыточность помехоустойчивого кода. После установления цикловой синхронизации признаки синхронизации снимаются с помехоустойчивого кода, при этом не уменьшается способность кода обнаруживать и корректировать ошибки.

Наиболее эффективно использование кодовой цикловой синхронизации в помехоустойчивых каскадных кодах. В этом случае синхронизация обеспечивается путем многократного повторения признаков синхронизации в различных словах внутреннего кода помехоустойчивого каскадного кода.

Актуальной является задача повышения помехоустойчивости устройства цикловой синхронизации при работе в нестационарных каналах связи с переменными параметрами и высоким уровнем помех. В таких каналах целесообразно использование устройства адаптивной кодовой цикловой синхронизации. Адаптацией в предлагаемом устройстве называется автоматическое и целенаправленное изменение параметров кодовой цикловой синхронизации с целью достижения оптимального функционирования устройства при изменении условий приема сообщений в канале связи.

Известно устройство кодовой цикловой синхронизации, содержащее регистр задержки, узел обнаружения ошибок, блок дешифраторов, счетчик, пороговый блок, генератор синхронизирующей последовательности, выходной сумматор по модулю два, причем регистр задержки и узел обнаружения ошибок объединены по входу и соединены с информационным входом устройства, узел обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффмена и регистра синдрома, причем каждый фильтр Хаффмена состоит из последовательно соединенных регистра и сумматора по модулю два, вход регистра синдрома соединен с выходом второго фильтра Хаффмена, а выход соединен с входом блока дешифраторов, выход генератора синхронизирующей последовательности соединен с первым входом выходного сумматора по модулю два, второй вход которого соединен с выходом регистра задержки, а выход соединен с информационным выходом устройства (Авторское свидетельство СССР №849521, кл. Н 04 L 7/08, опубл. 1981).

Однако это устройство обладает недостаточной помехоустойчивостью.

Наиболее близким к предлагаемому устройству является устройство (прототип), содержащее регистр задержки, узел обнаружения ошибок, блок дешифраторов, счетчик, пороговый блок, генератор синхронизирующей последовательности, выходной сумматор по модулю два, оперативное запоминающее устройство (ОЗУ), блок сумматоров по модулю два, блок сравнения номеров, полный сумматор и счетчик синхронизации, причем регистр задержки и узел обнаружения ошибок объединены по входу и соединены с информационным входом устройства, узел обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффмена и регистра синдрома, причем каждый фильтр Хаффмена состоит из последовательно соединенных регистра и сумматора по модулю два, вход регистра синдрома соединен с выходом второго фильтра Хаффмена, а выход соединен с входом блока дешифраторов, выход генератора синхронизирующей последовательности соединен с первым входом выходного сумматора по модулю два, второй вход которого соединен с выходом регистра задержки, а выход является информационным выходом устройства. При этом первый выход блока дешифраторов соединен с входом блока сумматоров по модулю два, остальные входы которого соединены с выходами регистра второго фильтра Хаффмена, второй выход блока дешифраторов соединен с входом разрешения записи ОЗУ, выходы блока сумматора по модулю два соединены с входами блока сравнения номеров, другие входы которого соединены со старшими разрядами счетчика, выход блока сравнения номеров соединен со старшими разрядами адресного входа ОЗУ, младшие разряды адресного входа которого соединены с младшими разрядами счетчика, тактовый вход счетчика соединен с входом синхронизации устройства, а также с тактовым входом счетчика синхронизации, установочные входы которого соединены с выходами блока сумматора по модулю два, разрешающий вход счетчика синхронизации соединен с выходом порогового блока, выход ОЗУ соединен с входом полного сумматора, выход полного сумматора соединен с информационным входом ОЗУ, выход счетчика синхронизации соединен с разрешающим входом генератора синхронизирующей последовательности и является выходом синхронизации устройства (Патент РФ №2197788, МПК 7 Н 04 L 7/08, опубл. 2003).

Недостатком известного устройства является невысокая помехоустойчивость, обусловленная тем, что при определении цикловой синхронизации не учитывается качество приема кодовых слов из канала связи.

Цель изобретения - увеличение помехоустойчивости устройства кодовой цикловой синхронизации сообщений и, как следствие, обеспечение возможности работы устройства в каналах связи с высоким уровнем помех за счет того, что наличие цикловой синхронизации определяют с учетом качества канала связи.

Для достижения цели предложено устройство адаптивной кодовой цикловой синхронизации, содержащее регистр задержки, узел обнаружения ошибок, блок дешифраторов, счетчик, пороговый блок, генератор синхронизирующей последовательности, выходной сумматор по модулю два, оперативное запоминающее устройство (ОЗУ), блок сумматоров по модулю два, блок сравнения номеров, полный сумматор и счетчик синхронизации, причем регистр задержки и узел обнаружения ошибок объединены по входу и соединены с информационным входом устройства, узел обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффмена и регистра синдрома, причем каждый фильтр Хаффмена состоит из последовательно соединенных регистра и сумматора по модулю два, вход регистра синдрома соединен с выходом второго фильтра Хаффмена, а выход соединен с входом блока дешифраторов, выход генератора синхронизирующей последовательности соединен с первым входом выходного сумматора по модулю два, второй вход которого соединен с выходом регистра задержки, а выход является информационным выходом устройства. При этом первый выход блока дешифраторов соединен с входом блока сумматоров по модулю два, остальные входы которого соединены с выходами регистра второго фильтра Хаффмена, второй выход блока дешифраторов соединен с входом разрешения записи ОЗУ, выходы блока сумматора по модулю два соединены с входами блока сравнения номеров, другие входы которого соединены со старшими разрядами счетчика, выход блока сравнения номеров соединен со старшими разрядами адресного входа ОЗУ, младшие разряды адресного входа которого соединены с младшими разрядами счетчика, тактовый вход счетчика соединен с входом синхронизации устройства, а также с тактовым входом счетчика синхронизации, установочные входы которого соединены с выходами блока сумматора по модулю два, разрешающий вход счетчика синхронизации соединен с выходом порогового блока, выход ОЗУ соединен с входом полного сумматора, выход полного сумматора соединен с информационным входом ОЗУ, выход счетчика синхронизации соединен с разрешающим входом генератора синхронизирующей последовательности и является выходом синхронизации устройства. Новым является то, что в устройство введены сумматор ошибок и преобразователь кода, при этом выход блока дешифраторов соединен с входом сумматора ошибок, выход которого соединен с входом преобразователя кода, выход которого связан со вторым входом полного сумматора, выход которого соединен с входом порогового блока.

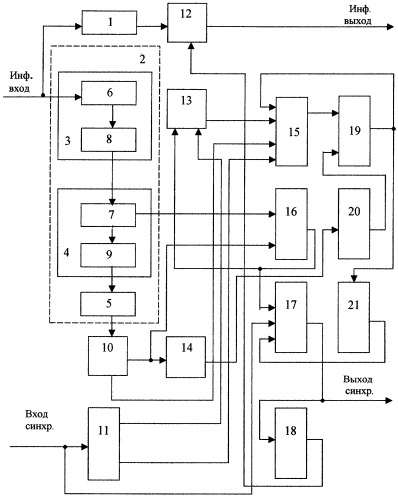

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство адаптивной кодовой цикловой синхронизации содержит регистр задержки 1, узел обнаружения ошибок 2, выполненный из двух последовательно соединенных первого фильтра 3 и второго фильтра 4 Хаффмена и регистра синдрома 5, причем каждый фильтр состоит соответственно из регистров 6 и 7 и сумматоров 8 и 9 по модулю два, блок дешифраторов 10, счетчик 11, выходной сумматор 12 по модулю два, блок сравнения номеров 13, сумматор ошибок 14, ОЗУ 15, блок сумматоров 16 по модулю два, счетчик синхронизации 17, генератор 18 синхронизирующей последовательности, полный сумматор 19, преобразователь кода 20 и пороговый блок 21.

Устройство работает следующим образом.

На передающей стороне формируется входная последовательность. Эта последовательность представляет собой сумму по модулю два трех последовательностей: внутренних двоичных кодов каскадного кода с1, синхронизирующей двоичной последовательности с2 и последовательности c3, нарушающей циклические свойства исходного кода.

Вначале на передающей стороне исходное сообщение, объемом k m-ичных (m>1) символов, кодируется m-ичным помехоустойчивым кодом, например, m-ичным помехоустойчивым кодом Рида-Соломона. Код Рида-Соломона является внешним кодом или кодом первой ступени помехоустойчивого каскадного кода.

В результате кодирования информации получается кодовое слово кода Рида-Соломона (n, k), информационная длина которого равна k, а блоковая - n символов.

Далее информация кодируется двоичным кодом, например двоичным кодом Боуза - Чоудхури - Хоквингема (БЧХ - коды) с проверочным многочленом h1(x). Код БЧХ является внутренним кодом или кодом второй ступени помехоустойчивого каскадного кода. Код БЧХ имеет параметры: n1 - блоковая длина кода, k1 - информационная длина кода.

Исходной информацией для каждого слова кода БЧХ являются символы кода Рида-Соломона, рассматриваемые как последовательность двоичных символов. В результате кодирования кодом БЧХ будет n двоичных слов кода БЧХ (n1,k1).

Далее осуществляется сложение по модулю два синхронизирующей последовательности с2 со словами кода БЧХ. В качестве синхронизирующей последовательности выбирается двоичный код с блоковой длиной n1 и информационной длиной k1, например, код Рида-Маллера (РМ) 1-го порядка (последовательность максимального периода) с проверочным многочленом h2(x). Между номерами слов БЧХ в каскадном коде и информационной частью синхронизирующей последовательности (кода РМ) устанавливается взаимно однозначное соответствие. Первое слово БЧХ складывается с последовательностью, полученной в результате кодирования 1 кодом РМ, второе - в результате кодирования кодом РМ-2 и т.д. Такое сложение выполняется со всеми словами кода БЧХ. Если проверочные многочлены суммируемых кодов h1(x) и h2(x) взаимно просты и являются делителями двучлена хn1+1, в результате будет получено n слов циклического кода БЧХ с блоковой длиной n1 и информационной - k1+k2. Этот код будет иметь вполне определенное гарантированное минимальное кодовое расстояние и обладать определенными корректирующими свойствами.

Третья последовательность с3, с которой складываются слова БЧХ, будет постоянная для всех слов последовательность длины n1 бит, нарушающая циклические свойства кода БЧХ. Такой последовательностью может быть любая последовательность, не являющаяся кодовым словом кода БЧХ, например, последовательность 10000...000.

На приемной стороне входная последовательность, сформированная в виде суммы трех последовательностей, поступает на информационный вход устройства цикловой синхронизации. При этом входная последовательность записывается в регистр задержки 1 и одновременно поступает на вход узла обнаружения ошибок 2, состоящего из двух последовательно соединенных первого фильтра 3 и второго фильтра 4 Хаффмена и регистра синдрома 5.

В первом фильтре 3 и втором фильтре 4 Хаффмена осуществляется умножение входной последовательности соответственно на проверочные многочлены кодов БЧХ и РМ - h1(x) и h2(х). Таким образом, в первом фильтре 3 Хаффмена вычисляется синдром кода БЧХ или последовательности с1, а во втором фильтре 4 - синдром кода РМ или последовательности c2.

При поступлении безошибочного слова синдром кода равен нулю и в регистре синдрома 5 будет записана комбинация d0, соответствующая преобразованной в первом фильтре 3 и втором фильтре 4 Хаффмена последовательности c3.

Предлагаемое устройство осуществляет цикловую синхронизацию не только по безошибочным словам кода БЧХ, но и по словам кода БЧХ, принятым с ошибками.

При поступлении на вход слова с ошибками, кратность которых лежит в пределах исправляющей способности кода, в регистре синдрома 5 будет записана комбинация из некоторого множества {di}, соответствующая преобразованной в первом фильтре 3 и втором фильтре 4 Хаффмена последовательности с3 и вектора ошибок.

Блок дешифраторов 10 при обнаружении комбинации d0 либо комбинации из множества {di} выдает сигнал разрешения записи на вход ОЗУ 15.

В этот момент времени в регистре 7 второго фильтра 4 Хаффмена находится комбинация, однозначно соответствующая последовательности c2, поскольку последовательность c1 снимается первым фильтром 3 Хаффмена, а последовательность c3 является постоянной.

Эта комбинация с выхода регистра 7 подается на вход блока сумматоров 16 по модулю два. В блоке сумматоров 16 осуществляется коррекция разрядов рассматриваемой комбинации так, чтобы на выходе блока сумматоров 16 по модулю два была комбинация, соответствующая номеру слова кода БЧХ. Для этого блок дешифраторов 10 путем распознавания комбинации синдрома в регистре синдрома 5 определяет вектор ошибок и выдает соответствующие корректирующие сигналы на вторые входы блока сумматоров 16 по модулю два.

Структура блока дешифраторов 10 соответствует комбинациям синдрома для исправляемых векторов ошибок. Комбинации синдрома, которые следует распознавать, получаются путем вычисления синдрома для каждого из требуемых векторов ошибок. Пример построения блока дешифраторов ошибок представлен в Кларк Дж., мл., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи: Пер. с англ. - М.: Радио и связь, 1987, стр.96-101.

Скорректированная комбинация с выхода блока сумматоров 16 поступает на первый вход блока сравнения номеров 13. На второй вход блока сравнения номеров 13 поступают сигналы со старших разрядов счетчика 11.

Счетчик 11 работает на тактовой частоте, поступающей по входу синхронизации устройства. Частота тактов равна скорости поступления информации на вход устройства.

Счетчик 11 состоит из двух частей: младшие разряды имеют коэффициент пересчета, равный длине слова кода БЧХ - n1, старшие разряды изменяются по сигналу переноса с младших разрядов и считают количество слов кода БЧХ, поступающих на вход устройства. Количество старших разрядов счетчика выбирается так, чтобы обеспечить счет всех n слов кода БЧХ каскадного кода.

В блоке сравнения номеров 13 вычисляется разность между номерами кодовых слов, вычисленных по принятым кодовым словам и отсчитанных счетчиком 11. Для правильно принятых кодовых слов эта разность должна быть постоянной, поскольку старшие разряды счетчика 11 изменяются синхронно с номерами кодовых слов, поступающих на вход устройства кодовой цикловой синхронизации.

Выход блока сравнения номеров 13 соединен с адресными входами ОЗУ 15. Остальные адресные входы ОЗУ 15 соединены с младшими разрядами счетчика 11. Таким образом, на адресный вход ОЗУ 15 поступают сигналы, определяющие фазу принятых кодовых слов или местоположение слов кода БЧХ в каскадном коде.

В ОЗУ 15 по каждому адресу, соответствующему фазе принятых кодовых слов, хранится число, соответствующее суммарной достоверности принятых из канала связи кодовых слов. По сигналу установки, который на схеме не показан, содержимое ОЗУ 15 обнуляется. С поступлением очередного кодового слова к содержимому ОЗУ 15, соответствующему суммарной достоверности кодовых слов, принятых с данной фазой, с помощью полного сумматора 19 добавляется определенное число, величина которого зависит от достоверности принятого кодового слова.

Качество канала связи определяется суммарной достоверностью принятых кодовых слов.

Оценка достоверности принятого кодового слова осуществляется по количеству ошибок в кодовом слове с помощью сумматора ошибок 14 и преобразователя кода 20.

Оценка достоверности отдельного принятого кодового слова выполняется следующим образом. Достоверность кодового слова определяется количеством ошибок в кодовом слове. Оценка количества двоичных разрядов f, используемых для обнаружения ошибок в блоке дешифраторов 10, будет равна

где k, n - информационная и блоковая длина кода соответственно, a t - количество ошибок в кодовом слове.

Достоверность кодового слова γ(t) при обнаружении t ошибок оценивают относительным числом разрядов кодового слова, используемых для обнаружения ошибок, и записывают в виде

при этом достоверность кодового слова, в котором не обнаружено ни одной ошибки, равна β - некоторому коэффициенту, введенному для нормирования величины достоверности. Нормирующий коэффициент выбирают таким образом, чтобы величины достоверности выражались целым числом (или величиной, близкой к целому числу), что позволяет упростить реализацию устройства. С увеличением числа ошибок t в принятом кодовом слове достоверность кодового слова, в соответствии с последней формулой, будет уменьшаться.

На выходе блока дешифраторов 10 при приеме кодового слова будет двоичная комбинация, соответствующая вектору ошибок. Эта двоичная комбинация поступает на вход сумматора ошибок 14, который осуществляет суммирование разрядов входной двоичной комбинации, и в результате на выходе сумматора ошибок 14 получается число ошибок t в принятом кодовом слове. Далее это число ошибок поступает на вход преобразователя кода 20. Преобразователь кода реализует функциональную зависимость между количеством ошибок t в принятом кодовом слове и достоверностью кодового слова γ(t), которая задается формулой (1). Преобразователь кода представляет собой комбинационную логическую схему. Для реализации этой схемы функциональную зависимость по формуле (1) зададим в табличном виде. Аргументом этой функциональной зависимости, заданной таблично, будет количество ошибок в кодовом слове, а выходом - достоверность кодового слова γ(t). Количество ошибок в кодовом слове может изменяться в пределах от 0 до максимального числа ошибок, которое может обнаружить помехоустойчивый код. Для используемых на практике помехоустойчивых кодов это число, как правило, не будет превышать величины двух, трех ошибок, и табличная функциональная зависимость по формуле (1) будет задаваться всего в трех, четырех точках. Эту табличную зависимость будем рассматривать как таблицу истинности некоторой логической функции. По таблице истинности логической функции составим логическую функцию и логическую комбинационную схему, реализующую эту таблицу, как это описано, например в Уэйкерли Дж. Ф. Проектирование цифровых устройств, том 1, Москва, Постмаркет, 2002, стр.237. В силу того, что объем таблицы, задающей функциональную зависимость (1) небольшой, то и реализация преобразователя кода 20 потребует незначительных аппаратных затрат.

После получения на выходе полного сумматора 19 суммарной достоверности принятых кодовых слов осуществляется сравнение этой достоверности с пороговым значением.

В случае, если суммарная достоверность кодовых слов с совпавшими нумерующими и синхронизирующими последовательностями превысит некоторый заранее выбранный порог γmax

то выполняется цикловая синхронизация. Это означает, что входная информация поступает на дальнейшую обработку. Превышение суммарной достоверности принятых кодовых слов заданной величины определяется пороговым блоком 21. На выходе порогового блока 21 возникает сигнал разрешения, поступающий на первый вход счетчика синхронизации 17. По этому сигналу осуществляется установка счетчика синхронизации 17 в состояние, соответствующее номеру последнего принятого кодового слова. При этом номер последнего кодового слова, при котором произошло превышение порога, с выхода блока сумматоров 16 по модулю два поступает на установочные входы счетчика синхронизации 17. По сигналу разрешения младшие разряды счетчика синхронизации 17 устанавливаются в 0, а в старшие - записывается номер последнего кодового слова.

Полный объем счетчика синхронизации 17 равен n кодовым словам кода БЧХ или n·n1, поскольку длина каждого слова БЧХ составляет n1 бит. На тактовый вход счетчика синхронизации 17 подается тактовая частота с входа синхронизации устройства кодовой цикловой синхронизации, равная скорости поступления информации на вход этого устройства, и по окончании приема всех слов кода БЧХ каскадного кода на выходе счетчика синхронизации 17 возникает сигнал переполнения.

По этому сигналу генератор 18 синхронизирующей последовательности начинает вырабатывать синхронизирующую последовательность, равную сумме последовательностей с2 и c3.

Синхронизирующая последовательность подается на первый вход выходного сумматора 12 по модулю два.

Число разрядов регистра задержки 1 выбрано равным длине всего каскадного кода, и в момент начала синхронизирующей последовательности на второй вход выходного сумматора 12 по модулю два поступают кодовые слова каскадного кода.

Синхронизирующая последовательность снимается с кодовых слов, и на информационный выход устройства кодовой цикловой синхронизации поступают слова исходного кода БЧХ или последовательность с1.

Одновременно сигнал переполнения с выхода счетчика синхронизации 17 поступает на выход синхронизации устройства кодовой цикловой синхронизации, сопровождая начало каскадного кода.

В предлагаемом устройстве количество кодовых слов с совпавшими нумерующими и синхронизирующими последовательностями, при котором принимается решение о наличии цикловой синхронизации, устанавливается в зависимости от качества канала связи. Достоверность принятия решения по неискаженным кодовым словам выше, и для надежной синхронизации требуется прием меньшего числа кодовых слов. При ухудшении качества канала связи достоверность принятых кодовых слов уменьшается, и для надежной синхронизации требуется большее число совпадений нумерующих и синхронизирующих последовательностей, поскольку часть кодовых слов принята с ошибками.

Максимальное число ошибок tmax, обнаруживаемых в кодовом слове, и пороговое значение суммарной достоверности γmax кодовых слов с совпавшими нумерующими и синхронизирующими последовательностями выбирают таким образом, чтобы обеспечить высокую вероятность цикловой синхронизации, не уступающую, по крайней мере, вероятности правильного приема помехоустойчивого каскадного кода без учета цикловой синхронизации. Оптимальный выбор указанных параметров обеспечивает существенное увеличение вероятности цикловой синхронизации по сравнению с известным устройством.

Например, для каскадного кода, внутренним кодом которого является двоичный код БЧХ (31, 16), а внешним кодом - код Рида - Соломона (24, 16) над полем Галуа GF(28), вероятность установления цикловой синхронизации в канале связи с независимыми ошибками при коэффициенте ошибок 0,05 составляет в прототипе 0,97. В то же время при рациональном выборе параметров предлагаемого устройства: максимальном числе ошибок, обнаруживаемых в кодовом слове tmax=1, пороговом значении суммарной достоверности принятых кодовых слов γmax=6 и нормирующем коэффициенте β=3 вероятность установления цикловой синхронизации в предлагаемом устройстве составит не менее 0,99. Достоверность кодового слова, принятого без ошибок, согласно формуле (1), равна 3, достоверность кодового слова с одиночной ошибкой, согласно той же формуле, равна 2. Поэтому цикловая синхронизация устанавливается по двум принятым без ошибок кодовым словам (3+3=6) либо по трем кодовым словам, если хотя бы одно из первых двух принято с одиночной ошибкой (3+2+2>6, 2+3+2>6, 2+2+3>6, 2+2+2=6).

В предлагаемом изобретении, в отличие от известного устройства, при определении цикловой синхронизации учитывают качество канала связи. Качество канала связи оценивается суммарной достоверностью принятых кодовых слов, что в свою очередь определяется кратностью ошибок, обнаруженных в принятых кодовых словах. Каждому принятому кодовому слову сопоставляется некоторое число, характеризующее достоверность кодового слова при обнаружении ошибок в этом кодовом слове. Учет величины достоверности приема кодовых слов, характеризующей качество канала связи, повышает помехоустойчивость цикловой синхронизации.

Достигаемым техническим результатом предлагаемого устройства адаптивной кодовой цикловой синхронизации является повышение помехоустойчивости.

Устройство адаптивной кодовой цикловой синхронизации, содержащее регистр задержки, узел обнаружения ошибок, блок дешифраторов, счетчик, пороговый блок, генератор синхронизирующей последовательности, выходной сумматор по модулю два, оперативное запоминающее устройство (ОЗУ), блок сумматоров по модулю два, блок сравнения номеров, полный сумматор и счетчик синхронизации, причем регистр задержки и узел обнаружения ошибок объединены по входу и соединены с информационным входом устройства, узел обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффмена и регистра синдрома, причем каждый фильтр Хаффмена состоит из последовательно соединенных регистра и сумматора по модулю два, вход регистра синдрома соединен с выходом второго фильтра Хаффмена, а выход соединен с входом блока дешифраторов, выход генератора синхронизирующей последовательности соединен с первым входом выходного сумматора по модулю два, второй вход которого соединен с выходом регистра задержки, а выход является информационным выходом устройства, при этом первый выход блока дешифраторов соединен с входом блока сумматоров по модулю два, остальные входы которого соединены с выходами регистра второго фильтра Хаффмена, второй выход блока дешифраторов соединен с входом разрешения записи ОЗУ, выходы блока сумматоров по модулю два соединены с входами блока сравнения номеров, другие входы которого соединены со старшими разрядами счетчика, выход блока сравнения номеров соединен со старшими разрядами адресного входа ОЗУ, младшие разряды адресного входа которого соединены с младшими разрядами счетчика, тактовый вход счетчика соединен с входом синхронизации устройства, а также с тактовым входом счетчика синхронизации, установочные входы которого соединены с выходами блока сумматоров по модулю два, разрешающий вход счетчика синхронизации соединен с выходом порогового блока, выход ОЗУ соединен с входом полного сумматора, выход полного сумматора соединен с информационным входом ОЗУ, выход счетчика синхронизации соединен с разрешающим входом генератора синхронизирующей последовательности и является выходом синхронизации устройства, отличающееся тем, что в устройство введены сумматор ошибок и преобразователь кода, при этом выход блока дешифраторов соединен с входом сумматора ошибок, выход которого соединен с входом преобразователя кода, выход которого связан со вторым входом полного сумматора, выход которого соединен с входом порогового блока.