Система передачи информации помехоустойчивым кодом с переменными параметрами

Иллюстрации

Показать всеСистема передачи информации помехоустойчивым кодом с переменными параметрами относится к системам передачи дискретной информации и может быть использована для передачи информации с помощью помехоустойчивого кода с переменными параметрами, в частности с помощью адаптивного каскадного помехоустойчивого кода. Технический результат - увеличение скорости передачи дискретной информации, повышение помехоустойчивости приема информации и достоверности передачи параметров помехоустойчивого кода. Для этого в систему на передающей стороне введены регистр параметров кода передающей части, распределитель управляющих сигналов передающей части и коммутатор передающей части, причем вход управления передающей части системы соединен с входом регистра параметров кода передающей части, первый выход которого соединен с управляющим входом кодирующего устройства внешнего кода, а второй выход - с первым информационным входом коммутатора передающей части, вход синхронизации передающей части системы соединен с входом распределителя управляющих сигналов передающей части, первый выход которого является управляющим входом генератора синхронизирующей последовательности, на приемной стороне введены распределитель управляющих сигналов приемной части, коммутатор приемной части, вычислитель синдрома внутреннего кода, дешифратор синдрома внутреннего кода, блок вычисления параметров кода, причем вход синхронизации приемной части системы соединен с входом распределителя управляющих сигналов, управляющий вход которого связан с выходом устройства цикловой синхронизации, а выход соединен с входом дешифратора синдрома. 1 з.п. ф-лы, 3 ил.

Реферат

Изобретение относится к системам передачи дискретной информации и может быть использовано для передачи информации с помощью помехоустойчивого кода с переменными параметрами, в частности с помощью адаптивного каскадного помехоустойчивого кода.

При работе кодека (кодирующего и декодирующего устройств) помехоустойчивого кода в нестационарных каналах связи целесообразно использование адаптивного помехоустойчивого кода, параметры которого могут изменяться в зависимости от состояния канала связи.

Для правильного декодирования адаптивного помехоустойчивого кода на приемной стороне системы передачи информации необходимо заранее знать информационную длину и блоковую длину помехоустойчивого кода. Поэтому передача параметров помехоустойчивого кода: информационной и блоковой длин кода с передающей стороны на приемную сторону системы передачи информации является актуальной задачей.

Наиболее эффективно предлагаемая система может применяться при использовании адаптивного каскадного помехоустойчивого кода (АКПК).

Известна система передачи информации помехоустойчивым кодом с переменными параметрами по протоколу MNP4 (или сходному по возможностям протоколу V.42), при котором параметры информационного пакета - количество байт в пакете, передаются с помощью специальных служебных команд. Пакет может содержать 32, 64, 128, 192 или 256 байт. С изменением качества канала связи размеры пакета изменяются. При большом уровне шумов передаются пакеты меньших размеров.

Известная система содержит на передающей стороне кодирующее устройство помехоустойчивого кода и генератор синхронизирующей последовательности, а на приемной - буферное запоминающее устройство, устройство цикловой синхронизации и декодирующее устройство помехоустойчивого кода (Минкин Э.Б., Белоцерковский И.Л. Модемы для передачи данных по коммутируемой телефонной сети. Сети, №4, 1991, стр.22).

Недостатком этой системы является снижение скорости передачи информации за счет передачи служебной информации о размере пакета и невысокая достоверность передачи параметров сообщения.

Наиболее близкой к предлагаемой системе передачи информации помехоустойчивым кодом с переменными параметрами является система (прототип), содержащая на передающей стороне кодирующее устройство внешнего кода, кодирующее устройство внутреннего кода, генератор синхронизирующей последовательности, сумматор по модулю два, причем информационный вход передающей части системы соединен с входом кодирующего устройства внешнего кода, выход которого соединен с входом кодирующего устройства внутреннего кода, выход которого соединен с входом сумматора по модулю два, выход которого является информационным выходом передающей части системы, на приемной стороне содержащая буферное запоминающее устройство, устройство цикловой синхронизации, декодирующее устройство внутреннего кода и декодирующее устройство внешнего кода, причем информационный вход приемной части системы соединен с входом буферного запоминающего устройства и входом устройства цикловой синхронизации, выход декодирующего устройства внутреннего кода является входом декодирующего устройства внешнего кода, информационный выход которого является выходом приемной части системы, а выход синхронизации является выходом синхронизации приемной части системы. (Квашенников В.В., Слепухин Ф.В. Система передачи информации помехоустойчивым кодом с переменными параметрами. Системы и средства связи, телевидения и радиовещания, вып.1, 2, 2003, стр.54).

Недостаток известной системы заключается в снижение скорости передачи информации за счет того, что информация о длине сообщения передается в первом блоке помехоустойчивого кода, что требует увеличения информационной части кода. Недостатком также является невысокая достоверность передачи параметров кода и снижение помехоустойчивости передачи информации.

Цель изобретения - повышение помехоустойчивости передачи информации за счет увеличения достоверности передачи параметров помехоустойчивого кода, а также повышение скорости передачи дискретной информации по каналу связи за счет того, что для передачи параметров помехоустойчивого кода не требуется увеличения информационной части кода.

Для достижения цели предложена система передачи информации помехоустойчивым кодом с переменными параметрами, содержащая на передающей стороне кодирующее устройство внешнего кода, кодирующее устройство внутреннего кода, генератор синхронизирующей последовательности, сумматор по модулю два, причем информационный вход передающей части системы соединен с входом кодирующего устройства внешнего кода, выход которого соединен с входом кодирующего устройства внутреннего кода, выход которого соединен с входом сумматора по модулю два, выход которого является информационным выходом передающей части системы, на приемной стороне содержащая буферное запоминающее устройство, устройство цикловой синхронизации, декодирующее устройство внутреннего кода и декодирующее устройство внешнего кода, причем информационный вход приемной части системы соединен с входом буферного запоминающего устройства и входом устройства цикловой синхронизации, выход декодирующего устройства внутреннего кода является входом декодирующего устройства внешнего кода, информационный выход которого является выходом приемной части системы, а выход синхронизации является выходом синхронизации приемной части системы. Новым является то, что на передающей стороне предлагаемая система дополнительно содержит регистр параметров кода передающей части, распределитель управляющих сигналов передающей части и коммутатор передающей части, причем вход управления передающей части системы соединен с входом регистра параметров кода передающей части, первый выход которого соединен с управляющим входом кодирующего устройства внешнего кода, а второй выход соединен с первым информационным входом коммутатора передающей части, вход синхронизации передающей части системы соединен с входом распределителя управляющих сигналов передающей части, первый выход которого является управляющим входом генератора синхронизирующей последовательности, второй выход соединен с управляющим входом коммутатора передающей части, а третий выход является выходом синхронизации передающей части системы, выход коммутатора передающей части соединен со вторым входом сумматора по модулю два, выход генератора синхронизирующей последовательности соединен со вторым информационным входом коммутатора передающей части, также на приемной стороне дополнительно содержит распределитель управляющих сигналов приемной части, коммутатор приемной части, вычислитель синдрома внутреннего кода, дешифратор синдрома внутреннего кода, блок вычисления параметров кода, причем вход синхронизации приемной части системы соединен с входом распределителя управляющих сигналов приемной части, управляющий вход которого связан с выходом устройства цикловой синхронизации, а выход соединен с входом дешифратора синдрома внутреннего кода, выход устройства цикловой синхронизации соединен с входом вычислителя синдрома внутреннего кода, второй вход которого соединен с информационным входом приемной части системы, выход вычислителя синдрома внутреннего кода соединен с входом дешифратора синдрома внутреннего кода и информационным входом блока вычисления параметров кода, выход дешифратора синдрома внутреннего кода соединен с входом управления блока вычисления параметров кода, информационный выход которого соединен с входом декодирующего устройства внутреннего кода и с входом декодирующего устройства внешнего кода, а также с управляющим входом коммутатора приемной части, информационный вход которого соединен с информационным выходом буферного запоминающего устройства, а выход коммутатора приемной части соединен со входом декодирующего устройства внутреннего кода. При этом блок вычисления параметров кода, в свою очередь, содержит регистр параметров кода приемной части, оперативное запоминающее устройство (ОЗУ), регистр числа совпадений, сумматор, схему сравнения, пороговый элемент, схему разрешения, причем информационный вход блока вычисления параметров кода соединен с информационным входом регистра параметров кода приемной части, вход управления блока вычисления параметров кода является разрешающим входом регистра параметров кода приемной части, выход которого соединен с адресным входом ОЗУ и информационным входом схемы разрешения, выход ОЗУ соединен с первым входом сумматора, на второй вход которого постоянно подана логическая единица, выход сумматора соединен с информационным входом ОЗУ, информационным входом регистра числа совпадений и входом схемы сравнения, управляющий вход регистра числа совпадений соединен с выходом схемы сравнения, второй вход которой соединен с выходом регистра числа совпадений и входом порогового элемента, выход которого соединен с управляющим входом схемы разрешения, выход схемы разрешения является информационным выходом блока вычисления параметров кода.

Система передачи информации помехоустойчивым кодом с переменными параметрами состоит из двух частей, относящихся соответственно к передающей и приемной частям системы.

Предлагаемая система иллюстрируется фиг.1-3.

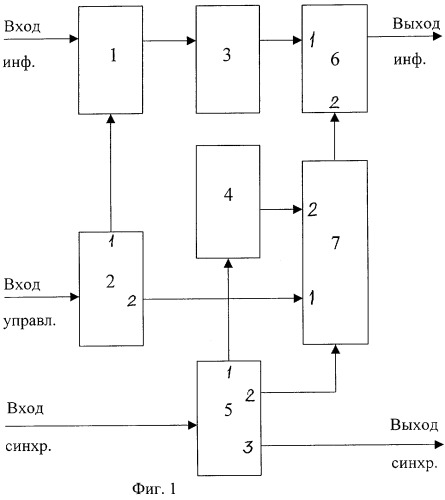

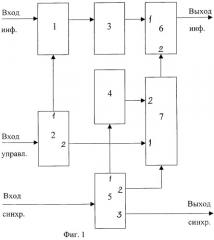

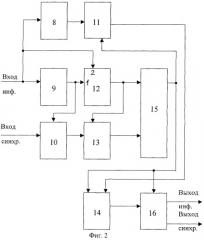

Структурная электрическая схема передающей части системы представлена на фиг.1, структурная электрическая схема приемной части системы показана на фиг.2. Структурная электрическая схема блока вычисления параметров кода, являющегося составной частью системы на приемной стороне, показана на фиг.3.

Передающая часть системы состоит из кодирующего устройства внешнего кода 1, регистра параметров кода передающей части 2, кодирующего устройства внутреннего кода 3, генератора синхронизирующей последовательности 4, распределителя управляющих сигналов передающей части 5, сумматора по модулю два 6, коммутатора передающей части 7.

Приемная часть рассматриваемой системы состоит из буферного запоминающего устройства 8, устройства цикловой синхронизации 9, распределителя управляющих сигналов приемной части 10, коммутатора приемной части 11, вычислителя синдрома внутреннего кода 12, дешифратора синдрома внутреннего кода 13, декодирующего устройства внутреннего кода 14, блока вычисления параметров кода 15, декодирующего устройства внешнего кода 16.

Блок вычисления параметров кода 15 состоит из регистра параметров кода 17 приемной части, ОЗУ 18, регистра числа совпадений 19, сумматора 20, схемы сравнения 21, порогового элемента 22, схемы разрешения 23.

Рассмотрим работу системы передачи информации помехоустойчивым кодом с переменными параметрами на передающей стороне (фиг.1).

Работу системы будем рассматривать на примере использования помехоустойчивого каскадного кода, внешним кодом которого является код Рида - Соломона, а внутренним - двоичный код Боуза-Чоудхури -Хоквинхема (код БЧХ).

Вначале исходное сообщение, поступающее по информационному входу рассматриваемой системы, объемом k m-ичных (m>1) символов, кодируется m-ичным помехоустойчивым кодом Рида-Соломона. Код Рида-Соломона является внешним кодом или кодом первой ступени помехоустойчивого каскадного кода.

На управляющий вход передающей части системы поступает информация, определяющая параметры кода: соответственно блоковую n и информационную k длины каскадного кода. Двоичные комбинации, соответствующие параметрам кода, запоминаются в регистре параметров кода передающей части 2.

Кодом Рида-Соломона информация кодируется в кодирующем устройстве внешнего кода 1, на управляющий вход которого с выхода регистра параметров кода передающей части 2 поступают значения параметров кода. В результате кодирования информации на выходе кодирующего устройства внешнего кода 1 получается кодовое слово кода Рида-Соломона (n, k), информационная длина которого равна k, а блоковая - n символов.

С выхода кодирующего устройства внешнего кода 1 информация поступает на вход кодирующего устройства внутреннего кода 3.

В этом устройстве информация кодируется двоичным кодом БЧХ. Код БЧХ является внутренним кодом или кодом второй ступени помехоустойчивого каскадного кода. Код БЧХ имеет постоянные параметры: n1-блоковая длина кода, k1-информационная длина кода.

Исходной информацией для каждого слова двоичного кода БЧХ являются символы кода Рида-Соломона, рассматриваемые как последовательность двоичных символов. В результате кодирования кодом БЧХ будет n двоичных слов кода БЧХ(n1, k1).

На вход синхронизации передающей части системы поступает сигнал, который запускает распределитель управляющих сигналов передающей части 5. Распределитель управляющих сигналов передающей части 5 формирует сигнал управления на генератор синхронизирующей последовательности 4 и коммутатор передающей части 7.

По этому сигналу с генератора синхронизирующей последовательности 4 начинает поступать синхронизирующая последовательность, а коммутатор передающей части 7 соединяет выход генератора синхронизирующей последовательности 4 с входом сумматора по модулю два 6. При этом в сумматоре по модулю два 6 осуществляется сложение синхронизирующей последовательности со словами кода БЧХ, поступающими на второй вход сумматора по модулю два 6. Такое сложение выполняется в течение времени, когда с выхода кодирующего устройства внутреннего кода 3 поступают первые n2(n2<n) слов кода БЧХ. Синхронизирующая последовательность далее используется на приемной стороне системы для цикловой синхронизации каскадного кода.

Для следующих n3(n2+n3≤n) слов кода БЧХ часть символов проверочных частей этих слов суммируется по модулю два с двоичными символами, соответствующими параметрам кода: информационной длине k кода и блоковой - n.

Для этого по окончании вывода n2 слов кода БЧХ распределитель управляющих сигналов передающей части 5 вырабатывает управляющий сигнал, по которому коммутатор передающей части 7 соединяет выход регистра параметров кода передающей части 2 с входом сумматора по модулю два 6. При этом символы проверочных частей следующих n3 слов кода БЧХ суммируются по модулю два с двоичными символами, соответствующими параметрам кода.

Таким образом, на информационном выходе передающей части системы будет n слов кода БЧХ, на первые n2 слов которого наложена последовательность синхронизации, а на следующие n3 слов - двоичная последовательность, соответствующая параметрам кода.

Слова кода БЧХ на информационном выходе передающей части системы сопровождаются сигналами синхронизации на выходе синхронизации передающей части системы.

На приемной стороне (фиг.2) принятая из канала связи информация поступает на информационный вход приемной части системы.

На приемной стороне вначале по первым n2 словам внутреннего кода осуществляют цикловую синхронизацию каскадного кода.

Для этого устройство цикловой синхронизации 9 пропускает входную информацию через цифровой фильтр, который выделяет синхронизирующую последовательность. По сихронизирующей последовательности устройство цикловой синхронизации 9 выдает сигнал, определяющий начало слов кода БЧХ, на которые наложены параметры кода. По этому сигналу запускается распределитель управляющих сигналов приемной части 10, а также вычислитель синдрома внутреннего кода 12. Распределитель управляющих сигналов приемной части 10 работает на тактовой частоте, поступающей по входу синхронизации приемной части системы. Тактовая частота на входе синхронизации соответствует скорости поступления входной информации.

Для неискаженных кодовых слов синдром кода будет равен нулю для тех символов кода, на которые не были наложены параметры кода, и будет равен параметрам кода в остальной части. Дешифратор синдрома внутреннего кода 13 по сигналам с выхода вычислителя синдрома внутреннего кода 12 определяет в фиксированные моменты времени, задаваемые сигналами с распределителя управляющих сигналов приемной части 10, наличие нулей в той части синдрома, которая соответствует символам проверочной части, на которые не накладывались параметры кода. Таким образом, дешифратор синдрома внутреннего кода 13 определяет наличие неискаженных кодовых слов и выдает соответствующий сигнал на вход блока вычисления параметров кода 15.

Блок вычисления параметров кода 15 по мажоритарному принципу определяет параметры кода. Более подробно работа блока вычисления параметров кода 15 будет рассмотрена ниже. Значения параметров кода с информационного выхода блока вычисления параметров кода 15 поступают на входы декодирующего устройства внутреннего кода 14 и декодирующего устройства внешнего кода 16. Блок вычисления параметров кода 15 выдает также с информационного выхода сигнал на управляющий вход коммутатора приемной части 11, который соединяет один из выходов буферного запоминающего устройства 8, соответствующего блоковой длине кода с входом декодирующего устройства внутреннего кода 14. При этом принятый каскадный код с соответствующего выхода буферного запоминающего устройства 8 через коммутатор приемной части 11 начинает поступать на вход декодирующего устройства внутреннего кода 14.

Декодирующее устройство внутреннего кода 14 снимает наложенные параметры кода с проверочных частей кода БЧХ и декодирует кодовые слова с обнаружением и исправлением ошибок. Восстановленная при этом информация составляет символы кода Рида-Соломона, которые далее декодируются в соответствии с вычисленными параметрами кода в декодирующем устройстве внешнего кода 16. Восстановленная в декодирующем устройстве внешнего кода 16 информация поступает на информационный выход приемной части системы. Информация сопровождается сигналами синхронизации с выхода синхронизации декодирующего устройства внешнего кода 16.

Блок вычисления параметров кода 15 определяет по мажоритарному принципу параметры кода и может быть реализован, например, как показано на фиг.3.

Параметры кода для неискаженного кодового слова БЧХ, полученные при вычислении синдрома кода, с выхода вычислителя синдрома внутреннего кода 12 поступают на информационный вход блока вычисления параметров кода 15. При наличии на входе управления блока вычисления параметров кода 15 разрешающего сигнала с выхода дешифратора синдрома внутреннего кода 13 параметры кода записываются в регистр параметров кода 17 приемной части. Выход регистра параметров кода 17 приемной части соединен с адресным входом ОЗУ 18. В ОЗУ 18 по каждому адресу, соответствующему параметрам кода, хранится количество принятых неискаженных кодовых слов с данными параметрами. По сигналу установки, который на структурной схеме не показан, содержимое ОЗУ 18 обнуляется. С поступлением очередного неискаженного кодового слова к содержимому ОЗУ 18, соответствующему принятым параметрам кода, с помощью сумматора 20 добавляется единица и это новое значение числа совпавших параметров кода записывается в ОЗУ 18 по старому адресу. В регистре числа совпадений 19 хранится максимальное число совпадений параметров кода. Запись максимального числа совпадений в регистр числа совпадений 19 осуществляется следующим образом. Новое число совпавших параметров с выхода сумматора 20 поступает на вход схемы сравнения 21, на второй вход которой подается максимальное число совпадений с выхода регистра числа совпадений 19. Если новое число совпадений больше старого, на выходе схемы сравнения 21 возникает сигнал разрешения и новое число совпадений записывается в регистр числа совпадений 19. Если число совпадений параметров кода превысит заданную величину, на выходе порогового элемента 22 возникает сигнал разрешения и параметры кода с выхода регистра параметров кода 17 приемной части поступают через схему разрешения 23 на информационный выход блока вычисления параметров кода 15.

Пороговый элемент 22 срабатывает при определенном числе совпадений параметров кодов, передаваемых различными словами внутреннего кода.

Пороговое значение, при котором срабатывает пороговый элемент 22, выбирается таким образом, чтобы обеспечить высокую достоверность передачи параметров кода.

Правильный выбор указанного порогового значения имеет немаловажное значение при реализации рассматриваемого устройства. Для АКПК, внутренним кодом которого является двоичный код БЧХ(31,16) а внешним - код Рида-Соломона, определенный над полем Галуа GF(28), четырех градациях информационной длины, восьми градациях блоковой длины АКПК, т.е. если для передачи параметров кода достаточно 5 бит, пороговое значение лежит в диапазоне от 2 до 3.

Достигаемым техническим результатом предлагаемой системы является повышение достоверности передачи параметров кода за счет многократного повторения параметров кода в различных словах внутреннего кода и, следовательно, высокая помехоустойчивость передаваемой информации. Кроме того, в рассматриваемой системе увеличивается скорость передачи информации в канале связи, поскольку параметры кода передаются в проверочных частях внутренних кодов каскадного кода без увеличения информационной части помехоустойчивого кода.

1. Система передачи информации помехоустойчивым кодом с переменными параметрами, содержащая на передающей стороне кодирующее устройство внешнего кода, кодирующее устройство внутреннего кода, генератор синхронизирующей последовательности, сумматор по модулю два, причем информационный вход передающей части системы соединен с входом кодирующего устройства внешнего кода, выход которого соединен с входом кодирующего устройства внутреннего кода, выход которого соединен с входом сумматора по модулю два, выход которого является информационным выходом передающей части системы, на приемной стороне содержащая буферное запоминающее устройство, устройство цикловой синхронизации, декодирующее устройство внутреннего кода и декодирующее устройство внешнего кода, причем информационный вход приемной части системы соединен с входом буферного запоминающего устройства и входом устройства цикловой синхронизации, выход декодирующего устройства внутреннего кода является входом декодирующего устройства внешнего кода, информационный выход которого является выходом приемной части системы, а выход синхронизации является выходом синхронизации приемной части системы, отличающаяся тем, что на передающей стороне предлагаемая система дополнительно содержит регистр параметров кода передающей части, распределитель управляющих сигналов передающей части и коммутатор передающей части, причем вход управления передающей части системы соединен с входом регистра параметров кода передающей части, первый выход которого соединен с управляющим входом кодирующего устройства внешнего кода, а второй выход соединен с первым информационным входом коммутатора передающей части, вход синхронизации передающей части системы соединен с входом распределителя управляющих сигналов передающей части, первый выход которого является управляющим входом генератора синхронизирующей последовательности, второй выход соединен с управляющим входом коммутатора передающей части, а третий выход является выходом синхронизации передающей части системы, выход коммутатора передающей части соединен со вторым входом сумматора по модулю два, выход генератора синхронизирующей последовательности соединен со вторым информационным входом коммутатора передающей части, также на приемной стороне дополнительно содержит распределитель управляющих сигналов приемной части, коммутатор приемной части, вычислитель синдрома внутреннего кода, дешифратор синдрома внутреннего кода, блок вычисления параметров кода, причем вход синхронизации приемной части системы соединен с входом распределителя управляющих сигналов приемной части, управляющий вход которого связан с выходом устройства цикловой синхронизации, а выход соединен с входом дешифратора синдрома внутреннего кода, выход устройства цикловой синхронизации соединен с входом вычислителя синдрома внутреннего кода, второй вход которого соединен с информационным входом приемной части системы, выход вычислителя синдрома внутреннего кода соединен с входом дешифратора синдрома внутреннего кода и информационным входом блока вычисления параметров кода, выход дешифратора синдрома внутреннего кода соединен с входом управления блока вычисления параметров кода, информационный выход которого соединен с входом декодирующего устройства внутреннего кода и с входом декодирующего устройства внешнего кода, а также с управляющим входом коммутатора приемной части, информационный вход которого соединен с информационным выходом буферного запоминающего устройства, а выход коммутатора приемной части соединен со входом декодирующего устройства внутреннего кода.

2. Система по п.1, отличающаяся тем, что блок вычисления параметров кода содержит регистр параметров кода приемной части, ОЗУ (оперативное запоминающее устройство), регистр числа совпадений, сумматор, схему сравнения, пороговый элемент, схему разрешения, причем информационный вход блока вычисления параметров кода соединен с информационным входом регистра параметров кода приемной части, вход управления блока вычисления параметров кода является разрешающим входом регистра параметров кода приемной части, выход которого соединен с адресным входом ОЗУ и информационным входом схемы разрешения, выход ОЗУ соединен с первым входом сумматора, на второй вход которого постоянно подана логическая единица, выход сумматора соединен с информационным входом ОЗУ, информационным входом регистра числа совпадений и входом схемы сравнения, управляющий вход регистра числа совпадений соединен с выходом схемы сравнения, второй вход которой соединен с выходом регистра числа совпадений и входом порогового элемента, выход которого соединен с управляющим входом схемы разрешения, выход схемы разрешения является информационным выходом блока вычисления параметров кода.