Проверка схемы на асинхронный сброс

Иллюстрации

Показать всеИзобретение относится к области проверки интегральных схем. Сущность: интегральная схема снабжена последовательной цепью тестового сканирования для выполнения проверки надлежащий работы интегральной схемы. Работа асинхронного сигнала сброса может быть проверена с использованием ячейки цепи сканирования, генерирующей сигнал сброса, которая выполнена так, что значение сигнала сброса, хранящееся в схеме этой ячейки с фиксацией состояния, асинхронно запирается, чтобы оно подавалось на схемную часть, под управлением сигнала, обеспечивающего сканирование. Схемы с фиксацией состояния, входящие в схемную часть, подвергаемую проверке, которые переводятся в состояние с заданными значениями при правильной работе сброса, могут быть предварительно загружены противоположными значениями сигнала до выполнения проверки функции сброса. 2 н. и 8 з.п. ф-лы, 7 ил.

Реферат

Это изобретение относится к области проверки интегральных схем. Более конкретно, изобретение касается проверки функции сброса интегральных схем.

Сразу после изготовления интегральных схем важно проверить их надлежащую работу. По мере усложнения интегральных схем заметно увеличивается объем испытаний, которые должны быть проведены для надлежащего контроля выполнения в достаточной степени функций интегральной схемы. Эти проблемы усугубляются по мере разработки и продвижения на рынок конструкций типа "система на кристалле", на основе которых многочисленные функциональные блоки, которые могут быть созданы и поставлены различными источниками, объединяются в одной интегральной схеме. Число имеющихся штырьковых выводов, которыми снабжен корпус интегральной схемы, ограничивает возможности доступа к точкам, находящимся в пределах корпуса интегральной схемы, для проведения проверки.

Один из путей увеличения возможностей по проведению проверки интегральных схем заключается в использовании последовательных цепей тестового сканирования, таких как цепи, предложенные в Стандарте IEEE JTAG. Последовательные цепи тестового сканирования могут быть использованы для развертки тестовых векторов для точек, находящихся в глубине в пределах интегральной схемы, ввода этих тестовых векторов и сбора результирующих значений, которые затем могут быть проанализированы для подтверждения правильной работы. Несмотря на то, что подход, связанный с цепью сканирования, имеет существенные достоинства и хорошо подходит для конструкций "система на кристалле", в которых различные участки могут быть снабжены своими собственными последовательными цепями тестового сканирования, недостатком этого подхода является сложность в осуществлении проверки надлежащей работы по функции сброса.

Методы, в которых используются последовательные цепи тестового сканирования, предусматривают развертку данных, ввод данных и сбор данных в режиме синхронизма с управляющим тактовым сигналом. Этот синхронный тип тестовой работы достаточно хорошо подходит для проведения проверки, когда нормальная работа схемы будет осуществляться в синхронном режиме. Однако существует проблема в проведении проверки для случая, когда нормальными являются асинхронные режимы работы интегральной схемы. Очень значимым примером такого асинхронного типа работы является отклик на асинхронный сигнал сброса. Обычно схемные части в пределах интегральной схемы реагируют на асинхронно подаваемый сигнал сброса и возвращаются в состояние инициализации. Неправильная работа по выполнению функции сброса является существенным недостатком интегральной схемы и важно, чтобы работа схемы по асинхронному сбросу проверялась надлежащим образом. Один из способов выполнения такой проверки заключается в том, чтобы для каждой схемной части формировать штырьковый вывод сброса, так чтобы он мог использоваться для проверки работы по функции сброса этой схемной части. Однако, как упоминалось ранее, число штырьков, которыми может быть снабжен корпус интегральной схемы, является постоянным ограничивающим фактором конструкции системы и нежелательно эти ценные штыревые выводы отводить для выполнения проверочных операций. Более того, при увеличении использования конструкций "система на кристалле", в которых применяется множество схемных частей или макроячеек из различных источников, на каждую из которых может подаваться свой собственный сигнал сброса, этот подход может привести к тому, что потребуется множество внешних штырьков сброса на корпусе схемы только для выполнения проверки схемы.

Рассмотренное с позиции одного аспекта настоящее изобретение предлагает интегральную схему, содержащую:

схемную часть, имеющую по меньшей мере одну схемную часть с фиксацией состояния, выполненную с возможностью запоминать значение сигнала, которое сбрасывается в заданное значение сброса при приеме схемной частью сигнала сброса; и

одну или более последовательных цепей тестового сканирования, каждая из который имеет ряд ячеек цепи сканирования, причем по меньшей мере одна из последовательных цепей тестового сканирования выполнена с возможностью запоминать тестовые сигналы и подавать их на схемную часть в качестве части выполнения проверки правильной работы этой схемной части, при этом тестовые сигналы подаются на схемную часть под управлением сигнала, обеспечивающего сканирование, и синхронно с тактовым сигналом, в которой последовательная цепь тестового сканирования включает ячейку цепи сканирования, генерирующую сигнал сброса, выполненную с возможностью, когда запомнено заданное значение сигнала сброса, генерировать сигнал сброса под управлением сигнала, обеспечивающего сканирование, и независимо от тактового сигнала и асинхронно с тактовым сигналом.

Изобретение признает, что в то время как сигнал, обеспечивающий сканирование, и тактовый сигнал нормально действуют синхронно для подачи тестовых сигналов, сигнал, обеспечивающий сканирование, может использоваться в сочетании с модифицированной ячейкой цепи сканирования для генерации сигнала сброса, чтобы генерировать этот сигнал сброса в момент, асинхронный с тактовым сигналом, и, следовательно, для контроля работы асинхронного сброса схемной цепи при выполнении проверки. Система может включать одну или более цепей сканирования (обычно более одной, но небольшая конструкция может иметь одну цепь сканирования).

Хотя будет понятно, что схемная часть, для которой проверяется работа по функции сброса, может иметь много различных видов и может быть всей интегральной схемой, изобретение особенно полезно, когда схемная часть, для которой проверяется функция сброса, представляет собой схемную часть в виде макроячейки. Такие схемные части в виде макроячейки часто имеют свою собственную особенную работу по выполнению функции сброса, которая требует надлежащей проверки. Проверка работы по выполнению функции сброса особенно значима, когда макроячейка представляет собой микропроцессор, поскольку микропроцессор - это схемный элемент, от которого вполне возможно может потребоваться выполнение операции сброса из-за аварийных отказов системы.

В контексте конструкций "система на кристалле", для которых изобретение особенно ценно, последовательная цепь тестового сканирования может быть обычным образом выполнена в виде граничной цепи тестового сканирования, окружающей схемную часть. Схемная часть и относящаяся к ней граничная цепь тестового сканирования часто будут поставляться специальным поставщиком и, соответственно, очень удобно, чтобы приспособления для проверки сброса были заключены в одну оболочку с этим поставляемым элементом.

Ячейки цепи сканирования могут включать запоминающие схемы с фиксацией состояния, значения которых обновляются в фиксированной точке в пределах цикла тактового сигнала. Это обеспечивает нормальный синхронный режим работы тестирующей цепи сканирования. В конкретном предпочтительном варианте выполнения ячейки цепи сканирования, генерирующей сигнал сброса, запоминающая схема с фиксацией состояния, находящаяся в этой ячейке, выполнена так, чтобы запоминать сигнал, значение которого также стробируется с помощью вентильной схемы, управляемой сигналом, обеспечивающим сканирование. Таким образом, значение сигнала, требующееся для генерации сигнала сброса, может быть загружено в ячейку цепи сканирования, генерирующую сигнал сброса, но сигнал не допускается для подачи на схемную часть, пока он не будет разблокирован путем соответствующего изменения сигнала, обеспечивающего сканирование.

Рассмотренное с позиции другого аспекта настоящее изобретение предлагает способ выполнения проверки работы интегральной цепи по функции сброса, при этом интегральная цепь имеет схемную часть, включающую по меньшей мере одну схемную часть с фиксацией состояния, выполненную с возможностью запоминать значение сигнала, которое сбрасывается в заданное значение сброса при приеме схемной частью сигнала сброса, и одну или более последовательных цепей тестового сканирования, каждая из который имеет ряд ячеек цепи сканирования, причем по меньшей мере одна из последовательных цепей тестового сканирования выполнена с возможностью запоминать тестовые сигналы и подавать их на схемную часть, в качестве части выполнения проверки правильной работы этой схемной части, при этом тестовые сигналы подаются на схемную часть под управлением сигнала, обеспечивающего сканирование, и синхронно с тактовым сигналом, содержащий этапы:

запоминание заданного значения сигнала сброса в ячейке цепи сканирования, генерирующей сигнал сброса, входящей в последовательную цепь тестового сканирования;

генерирование сигнала сброса исходя из заданного значения сигнала сброса под управлением сигнала, обеспечивающего сканирование, и независимо от тактового сигнала и асинхронно с тактовым сигналом.

Теперь будет описан вариант выполнения изобретения, но только в качестве примера, со ссылкой на прилагаемые чертежи, на которых:

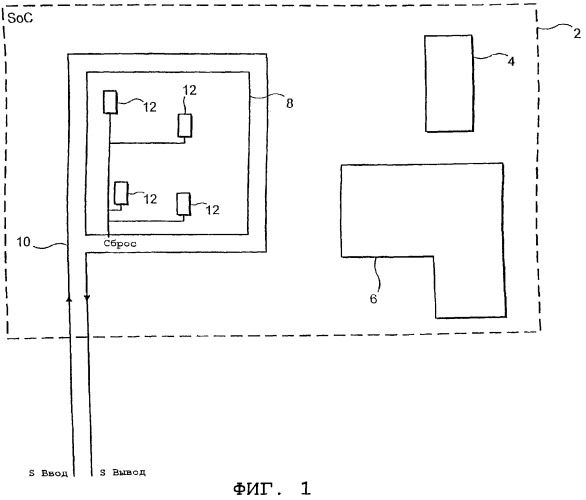

фиг.1 схематично иллюстрирует конструкцию "система на кристалле", содержащую ряд макроячеек;

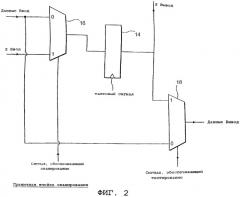

фиг.2 иллюстрирует граничную ячейку сканирования;

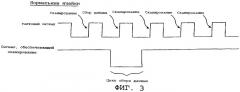

фиг.3 иллюстрирует тактовый сигнал и сигнал, обеспечивающий сканирование, используемый для управления граничной ячейкой сканирования, показанной на фиг.2;

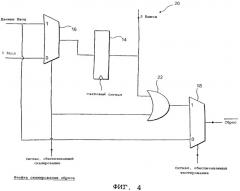

фиг.4 иллюстрирует ячейку цепи сканирования, генерирующую сигнал сброса;

фиг.5 и 6 схематично иллюстрируют работу схемы, показанной на фиг.4;

фиг.7 схематично иллюстрирует различные возможные соотношения между сигналом, обеспечивающим сканирование, и тактовым сигналом, когда производится проверка асинхронного сброса.

Фиг.1 иллюстрирует интегральную схему 2, включающую ряд макроячеек 4, 6, 8. Каждая из этих макроячеек может обеспечивать различные функциональные возможности интегральной схемы 2 и может быть создана и поставлена различными поставщиками. Макроячейка 8 представляет собой микропроцессорное ядро 8 и окружена граничной цепью 10 ячеек сканирования. В пределах микропроцессорного ядра 8 имеется ряд схем 12 с фиксацией состояния, которые запоминают значения сигнала, которые переводятся в заданное значение сигнала сброса во время нормальной, правильной работы сигнала сброса. Путем перевода каждой из этих схем с фиксацией состояния в это состояние с заданным сигналом сброса микропроцессор 8 может быть установлен в известное состояние сброса, из которого процесс обработки данных может быть благополучно возобновлен. Сигнал сброса при нормальной работе может быть подан асинхронно с любым из других сигналов, управляющих работой интегральной схемы 2, и поэтому важно, чтобы правильная работа сигнала сброса также проверялась в асинхронном режиме. Как только сигнал сброса подан асинхронно во время проверки, значения сигнала, запомненные в схемах 12 с фиксацией состояния, могут быть просканированы для проверки правильной работы.

Граничная цепь 10 ячеек сканирования формируется из ряда последовательно соединенных ячеек цепи сканирования, которые могут управляться в соответствии с Стандартом IEEE JTAG, они расположены по периметру микропроцессора 8. Ячейки цепи сканирования используются для ввода в микропроцессор 8 тестовых сигналов и сбора результирующих сигналов из микропроцессора 8.

Фиг.2 иллюстрирует один возможный вид стандартной граничной ячейки сканирования. Схема 14 с фиксацией состояния выполнена в пределах ячейки цепи сканирования, и она может быть использована либо для запоминания значения сигнала, подаваемого на схемную часть при проверке, либо для снятия значения с схемной части при проверке. Когда это требуется, то для последовательного изменения значений сигнала в цепи ячеек сканирования или вывода их из цепи ячеек сканирования, используется сигнал, обеспечивающий сканирование, для переключения мультиплексора 16, чтобы последовательно осуществлять соединения с ячейками цепи сканирования. Схема 14 с фиксацией состояния выполнена так, чтобы ее значение обновлялось при повышающем перепаде тактового сигнала, подаваемого на ключевую схему 14 с фиксацией состояния. Таким образом, при каждом повышающем перепаде тактового сигнала значения сигнала, хранящиеся в соответствующих схемах 14 с фиксацией состояния, повышаются на одну позицию в цепи ячеек сканирования и на выходе цепи ячеек сканирования в целом. Дополнительный мультиплексор 18 выполнен для шунтирования ячейки сканирования в целом, когда не выполняется работа по проверке схемы, и он управляется сигналом, обеспечивающим тестирование.

На фиг.3 показана сигнальная диаграмма, иллюстрирующая работу схемы, представленной на фиг.2. Схема 14 с фиксацией состояния обновляется при каждом повышающем перепаде тактового сигнала. Когда сигнал, обеспечивающий сканирования, высокий, то повышающий перепад тактового сигнала будет запускать последовательное изменение значений сигнала по цепи ячеек сканирования. Когда сигнал, обеспечивающий сканирование, низкий, тогда повышающий перепад тактового сигнала будет запускать снятие значения сигнала из схемной части, подвергаемой проверке, когда ячейка представляет собой ячейку, предназначенную для сбора сигнала. Когда новые значения сигнала запоминаются в схеме 14 с фиксацией состояния в синхронном режиме с тактовым сигналом, то они подаются на схемную часть при проверке.

Фиг.4 иллюстрирует ячейку 20 цепи сканирования, генерирующую сигнал сброса. Эта ячейка 20 цепи сканирования, генерирующая сигнал сброса, модифицирована на основе ячейки, показанной на фиг.2, путем включения логического элемента 22 ИЛИ. Логический элемент 22 ИЛИ предназначен для осуществления селекции сигнала, хранящегося в схеме 14 с фиксацией состояния, используя значение, обеспечивающее сканирование, чтобы сигнал либо подавался как сигнал сброса, либо не подавался как сигнал сброса. Сигнал сброса, генерированный ячейкой 20 цепи сканирования, генерирующей сигнал сброса, является активным, когда сигнал, обеспечивающий сканирование, низкий, и, соответственно, если сигнал, обеспечивающий сканирование, высокий, тогда действие логического элемента 22 ИЛИ будет заключаться в том, чтобы "держать" сигнал сброса в качестве неактивного сигнала независимо от того, какое значение сигнала хранится в схеме 14 с фиксацией состояния.

Обратимся к фиг.5, когда требуется, чтобы проверка работы функции сброса не выполнялась, тогда высокое значение может быть запомнено в схеме 14 с фиксацией состояния и, следовательно, сигнал сброса будет удерживаться неактивным независимо от величины сигнала, обеспечивающего сканирование.

Как показано на фиг.6, когда требуется провести проверку асинхронной генерации сигнала сброса, тогда это производится путем загрузки сначала схемы 14 с фиксацией состояния низким значением сигнала. Это низкое значение сигнала препятствует тому, чтобы сигнал появился на выходе ячейки 20 цепи сканирования, генерирующей сигнал сброса, пока сигнал, обеспечивающий сканирование, также не станет низким. Сигнал, обеспечивающий сканирование, может быть сделан низким независимо от текущего состояния тактового сигнала и, таким образом, активный сигнал сброса может быть разблокирован для подачи в схемную часть, подвергаемую проверке, в асинхронном режиме, если это требуется.

Для того чтобы выполнить тщательную проверку асинхронной природы функции сброса, временной интервал с низким значением сигнала, обеспечивающего сканирование, однозначно не должен в себя момент повышающего перепада тактового сигнала CLK, как показано на фиг.7.

Вернемся к фиг.1, для того чтобы выполнить тщательно проверку работы функции сброса, каждая из схем 12 с фиксацией состояния, которая переводится в заданное значение сброса путем подачи сигнала сброса, может быть предварительно, до проверки сигнала сброса, загружена значением сигнала, противоположным заданному значению сигнала сброса. Эти установленные значения могут быть введены в схемы 12 с фиксацией состояния с помощью соответствующей цепи ячеек сканирования. Когда все схемы 12 с фиксацией состояния надлежащим образом загружены, тогда может быть разблокирован асинхронный сигнал сброса, и в каждой схеме 12 с фиксацией состояния должен произойти переход значения сигнала, если работа функции сброса выполняется правильно. Правильная работа этого асинхронного сброса может быть проверена путем сбора и сканирования новых значений в схемах 12 с фиксацией состояния и других значений, указывающих на состояние, из области вокруг микропроцессора 8.

1. Интегральная схема, содержащая схемную часть, имеющую по меньшей мере одну схемную часть с фиксацией состояния, выполненную с возможностью запоминания значения сигнала, которое сбрасывается в заданное значение сброса при принятии схемной частью сигнала сброса; и одну или более последовательных цепей тестового сканирования, каждая из которых имеет ряд ячеек цепи сканирования, причем по меньшей мере одна из последовательных цепей тестового сканирования выполнена с возможностью запоминания тестовых сигналов и подачи их на схемную часть в качестве части выполнения проверки правильной работы этой схемной части, при этом тестовые сигналы подаются на схемную часть под управлением сигнала, обеспечивающего сканирование, и синхронно с тактовым сигналом; в которой последовательная цепь тестового сканирования включает ячейку цепи сканирования, генерирующую сигнал сброса, выполненную с возможностью при запоминании заданного значения сигнала сброса генерирования сигнала сброса под управлением сигнала, обеспечивающего сканирование, и независимо от тактового сигнала и асинхронно с тактовым сигналом.

2. Интегральная схема по п.1, в которой схемная часть представляет собой схемную часть в виде макроячейки.

3. Интегральная схема по п.2, в которой схемная часть представляет собой макроячейку микропроцессора.

4. Интегральная схема по любому из пп.1-3, в которой последовательная цепь тестового сканирования представляет собой граничную цепь тестового сканирования, окружающую схемную часть.

5. Интегральная схема по любому из предыдущих пунктов, в которой последовательная цепь тестового сканирования подает тестовый сигнал на схемную часть и снимает сигналы-отклики со схемной части.

6. Интегральная схема по любому из предыдущих пунктов, в которой ячейки цепи сканирования включают схему с фиксацией состояния для запоминания сигнала, которая выполнена с возможностью обновления в фиксированной точке в пределах сигнального цикла тактового сигнала.

7. Интегральная схема по любому из предыдущих пунктов, в которой ячейка цепи сканирования, генерирующая сигнал сброса, включает схему с фиксацией состояния для запоминания сигнала сброса, которая выполнена с возможностью обновления в фиксированной точке в пределах сигнального цикла тактового сигнала.

8. Интегральная схема по п.7, в которой ячейка цепи сканирования, генерирующая сигнал сброса, включает вентильную схему, выполненную с возможностью стробирования генерированного сигнала сброса из схемы с фиксацией состояния, запоминающей сигнал сброса, с помощью сигнала, обеспечивающего сканирование.

9. Интегральная схема по любому из предыдущих пунктов, в котором каждая схемная часть с фиксацией состояния загружается значением сигнала, отличающимся от заданного значения сброса, до генерации сигнала сброса.

10. Способ выполнения проверки работы функции сброса интегральной цепи, при этом интегральная цепь имеет схемную часть, включающую по меньшей мере одну схемную часть с фиксацией состояния, выполненную с возможностью запоминать значение сигнала, которое сбрасывается в заданное значение сброса при приеме схемной частью сигнала сброса, и одну или более последовательных цепей тестового сканирования, каждая из которых имеет ряд ячеек цепи сканирования, причем по меньшей мере одна из последовательных цепей тестового сканирования запоминает тестовые сигналы и подает их на схемную часть в качестве части выполнения проверки правильной работы этой схемной части, при этом тестовые сигналы подают на схемную часть под управлением сигнала, обеспечивающего сканирование, и синхронно с тактовым сигналом, содержащий этапы, при которых запоминают заданное значение сигнала сброса в ячейке цепи сканирования, генерирующей сигнал сброса, входящей в последовательную цепь тестового сканирования; и осуществляют генерирование сигнала сброса из заданного значения сигнала сброса под управлением сигнала, обеспечивающего сканирование, и независимо от тактового сигнала и асинхронно с тактовым сигналом.