Устройство для контроля и самоконтроля знаний обучаемых

Иллюстрации

Показать всеИзобретение относится к учебным устройствам и может быть использовано для обучения и контроля знаний и диагностики качества обучения в различных учебных заведениях независимо от формы обучения, в том числе и с применением дистанционных технологий, а также может найти применение в отделах охраны труда и техники безопасности предприятий. Устройство для контроля и самоконтроля знаний обучаемых содержит блок ввода ответных действий обучаемого, входами которого являются клавиши клавиатуры компьютера, а его выходы связаны с соответствующими на этой клавиатуре клавишами, преобразователь кодов, блок режимов работы, формирователь пароля, блок индикаторов, последовательно соединенный с формирователем пароля, коммутатор, пять блоков памяти, блок равенства, блок управления повторами, преобразователь ответа без учета порядка и блок управления сбросом. Входы первого блока памяти подключены к выходам блока ввода ответных действий обучаемого, а выход служит для подключения к компьютеру. Этим обеспечивается возможность компьютерной обработки результатов самостоятельной работы обучаемого, осуществления самоконтроля знаний, так как все его действия записываются в этот блок памяти. Правильность введенного ответа обучаемый определяет по состоянию индикаторов. Кроме этого входы еще двух блоков памяти предназначены для подключения к компьютеру. Автоматизированный контроль знаний и компьютерная обработка расширяют эксплуатационные характеристики устройства. Всякое задание, выдаваемое обучаемому, содержит специальный код, получаемый путем преобразования ответа по определенному алгоритму. Длина кода задания меньше длины кода ответа. Этим обеспечивается устойчивость системы кодирования против попыток получить хорошую оценку иным путем, кроме правильного решения всех задач задания. Благодаря \секретным\ кодам, хранящимся в одном из блоков памяти, обучаемый не может сам сконструировать пароль так, чтобы в результате его расшифровки получились все или большинство правильных ответов. Заявляемое устройство допускает возможность кодирования заданий в любых системах, для чего достаточно подключить его к компьютеру и сменить в нем систему преобразования ответов. Наличие определенных блоков, из которых состоит устройство, их функциональные связи создают возможность управления повторами вводимых знаков, повышают информативность пароля, обеспечивают возможность реализации сложных критериев дихотомической оценки ответов, задаваемых булевыми функциями в системах множественного выбора. Все это расширяет логико-дидактические возможности устройства и его эксплуатационные характеристики. 1 з.п.ф-лы, 13 ил., 2 табл.

Реферат

Изобретение относится к области обучения, а именно к учебным устройствам, и может быть использовано для обучения и контроля знаний и диагностики качества обучения в различных учебных заведениях независимо от формы обучения, в том числе и с применением дистанционных технологий, а также может найти применение в отделах охраны труда и техники безопасности предприятий.

Известно устройство для контроля знаний обучаемых по авторскому свидетельству СССР на изобретение №1149302, МПК G 09 В 7/02, опубл. 07.04.85. Бюл. №13. Оно содержит блок ввода ответных действий обучаемого, генератор импульсов, три распределителя импульсов, два формирователя импульсов, блок формирователей импульсов, блок регистрации правильных ответов, блок регистрации неправильных ответов, три элемента задержки, триггер, первый, второй элементы И, элементы И первой группы, элементы И второй группы, блок элементов И, первый, второй, третий элементы ИЛИ. Выход блока регистрации правильных ответов соединен с одним из входов блока регистрации неправильных ответов, а один из его входов - с выходами элементов И второй группы. Входы элементов И второй группы соединены с выходом второго формирователя импульсов, с выходом первого распределителя импульсов, другой выход которого через первый элемент задержки подключен к входу первого элемента И, а вход - непосредственно к выходу второго элемента ИЛИ. Вход второго элемента ИЛИ соединен с выходом первого формирователя импульсов. Входы элементов И первой группы подключены к выходу второго элемента задержки. Вход второго элемента И соединен с выходом первого элемента ИЛИ, а выход - с входом второго распределителя импульсов, другой вход которого через блок элементов И подключен к выходам блока формирователей импульсов и третьего распределителя импульсов. Вход третьего распределителя импульсов соединен с выходом второго элемента ИЛИ, подключенным к входу триггера. Вход блока формирователей импульсов подключен к выходу блока ввода ответных действий обучаемого. Блоки и узлы, из которых состоит это известное устройство, их взаимосвязь обеспечивают функционирование устройства в режимах обучения и контроля знаний. Причем, каждому коду задания при использовании этого устройства соответствует единственный ответ. К недостаткам этого устройства следует отнести то, что оно не распознает правильность неоднозначных ответов, связанных с неупорядоченной последовательностью символов в ответе, с необходимостью ограничения числа значащих символов ответа, использованием в ответе специальных символов, например таких, как +, ;, (). Следовательно, эксплуатационные характеристики устройства ограничены, поскольку его невозможно использовать для целого класса заданий с неоднозначными ответами. Кроме этого, это устройство не может быть использовано для осуществления самоконтроля знаний обучаемых.

Наиболее близким по технической сущности и решаемой задаче является устройство для контроля и самоконтроля знаний обучаемых, защищенное патентом Российской Федерации на изобретение №2084962, МПК G 09 В 7/02, опубл. 20.07.97. Бюл. №20. Это устройство содержит блок ввода ответных действий обучаемого, два распределителя импульсов, блок управления режимами (блок режимов работы), последовательно соединенные первый блок суммирования, блок формирования пароля и блок индикации пароля (блок индикаторов), а также последовательно соединенные блок суммирования по модулю два, второй блок суммирования и блок формирования цифр кода задания, блок регистров режимной части задания, блок регистрации исходной части задания, блок формирования операндов. Кроме этого устройство содержит последовательно соединенные коммутационный блок (коммутатор) и блок сравнения, блок регистрации, три элемента И, два из которых первыми входами соединены с выходами блока сравнения, а вторыми входами - с управляющим выходом блока ввода ответных действий обучаемого. Выходами эти два элемента И связаны с входами блока регистрации, выход которого подключен к управляющему входу блока управления режимами. Входы третьего элемента И связаны с выходом первого распределителя импульсов и выходом блока управления режимами, а его выход соединен с входом сброса второго блока суммирования. Вход блока ввода ответных действий обучаемого подключен к управляющему выходу блока управления режимами, а выходы блока ввода ответных действий обучаемого соединены со входами распределителей импульсов и с управляющими входами блока управления режимами. Ввод кода задания и ответов в блок ввода ответных действий обучаемого осуществляется нажатием одной из \n\ кнопок (клавиш), каждой из которых поставлено в соответствие некоторое множество символов. Каждый из распределителей импульсов соответственно его функциям связан с другими входящими в это устройство блоками, а в совокупности оба распределителя объединяют все блоки устройства.

Последовательное включение двух блоков суммирования при совместной работе распределителей импульсов позволяет реализовать многовариантные режимы ответов на один код задания, т.е. осуществить принцип кодовой избыточности за счет возможности удлинения кодов. Кроме этого при использовании данного устройства обеспечивается возможность распознавания правильности неоднозначных ответов и достигается соответствие каждому ответу неограниченного числа кодов заданий. Естественно, что все это расширяет логико-дидактические возможности устройства и улучшает его эксплуатационные характеристики. Однако это известное устройство имеет ряд недостатков.

Во-первых, в системах множественного выбора устройство не обеспечивает возможность реализации сложных критериев правильности ответов, задаваемых булевыми функциями, что значительно ограничивает логико-дидактические возможности устройства.

Во-вторых, формируемый устройством пароль является малоинформативным. Под \паролем\ понимается последовательность нескольких цифр и букв, которая обеспечивает простоту и удобство внешнего контроля, так как вместо громоздких ответов (формул, чисел, слов, фраз) проще работать с короткими паролями. С помощью пароля, формируемого устройством по прототипу, можно определить правильность ответа только к одному вопросу, а при наличии в задании нескольких вопросов по одному паролю невозможно определить, какие ответы являются правильными, а какие - неправильными. Поэтому в случае внешнего контроля, например, в дистанционном образовании, обучаемый вынужден отчитываться о выполнении индивидуального задания, перечисляя десятки и сотни паролей, то есть по одному паролю на каждый вопрос. Такой способ отчета даже при коротких паролях является громоздким и неудобным в работе.

В-третьих, кодирование заданий осуществляется только по одной, жестко зафиксированной системе, в которой заложена устойчивость против попыток разгадать принцип кодирования ответов. Но по мере накопления статистических сведений эта устойчивость может снизиться до нуля, и контроль, осуществляемый устройством, потеряет информативность.

В-четвертых, в известном устройстве ограничены функции автоматизированного контроля знаний обучаемых, поскольку известным устройством невозможно организовать контроль качества обучения и анализ самостоятельной работы обучаемых, в частности при дистанционном обучении. Невозможность организации многофункционального автоматизированного контроля связана с тем, что конструктивное выполнение известного устройства не предусматривает возможность компьютерной обработки введенной в устройство информации.

Задача изобретения - улучшить логико-дидактические и эксплуатационные характеристики устройства и расширить сферу его применения.

Задача решена следующим образом.

Общим с прототипом является то, что устройство для контроля и самоконтроля знаний обучаемых содержит блок ввода ответных действий обучаемого, входами которого являются клавиши клавиатуры, соответствующие определенным вводимым символам, блок режимов работы, формирователь пароля, блок индикаторов, последовательно соединенный с формирователем пароля, и коммутатор, но в отличие от прототипа согласно изобретению оно дополнительно содержит первый блок памяти, первый вход которого соединен с первым выходом блока ввода ответных действий обучаемого, второй блок памяти, третий блок памяти, первым входом соединенный с первым выходом второго блока памяти, а выходом - с первым входом формирователя пароля, четвертый блок памяти, первый вход которого соединен с первым выходом коммутатора, пятый блок памяти, к выходу которого подключен второй вход формирователя пароля. Кроме этого заявляемое устройство в отличие от прототипа дополнительно содержит блок равенства, первый вход которого соединен со вторым выходом второго блока памяти, а его второй вход соединен с выходом четвертого блока памяти, блок управления повторами, первый вход которого подключен к первому выходу коммутатора, преобразователь ответа без учета порядка, выход которого соединен с третьим входом формирователя пароля и с третьим входом блока равенства, преобразователь кодов, вход которого подключен к первому выходу блока ввода ответных действий обучаемого, а выход - к первому входу второго блока памяти, к первому входу пятого блока памяти, ко второму входу блока управления повторами, к первому входу преобразователя ответа без учета порядка и к первому входу блока режимов работы, блок управления сбросом, первый выход которого соединен со вторым входом пятого блока памяти, с пятым входом формирователя пароля, с третьими входами второго и третьего блоков памяти, при этом вторые входы этих блоков памяти соединены со вторым выходом коммутатора. Отличием является также то, что второй выход блока ввода ответных действий обучаемого является выходом синхронизации и соединен со вторым входом первого блока памяти, вторым входом блока режимов работы, третий выход блока ввода ответных действий обучаемого соединен с четвертым входом формирователя пароля, его четвертый выход соединен со вторым входом блока управления сбросом, пятый выход блока ввода ответных действий обучаемого соединен с первым входом блока управления сбросом, а шестой его выход связан с одним из двенадцати входов блока индикаторов. Кроме этого второй выход блока управления сбросом соединен с первым входом коммутатора, третьим входом блока режимов работы, со вторым входом четвертого блока памяти, со вторым входом преобразователя ответа без учета порядка, с шестым входом формирователя пароля, с третьим входом блока управления повторами, с выходом которого соединен второй вход коммутатора. Третий вход преобразователя ответов без учета порядка подключен к первому выходу коммутатора. Третий вход четвертого блока памяти соединен с выходом преобразователя кодов. Первый выход блока индикаторов связан с одним из входов пятого блока памяти, а его второй выход - с четвертым входом блока режимов работы, при этом пятый вход блока режимов работы соединен с седьмым выходом блока ввода ответных действий обучаемого. Третий и четвертый входы пятого блока памяти подключены соответственно к первому и третьему из восьми выходам блока режимов работы, причем, к первому выходу блока индикаторов подключен пятый вход пятого блока памяти, а шестой вход пятого блока памяти соединен со вторым выходом блока ввода ответных действий обучаемого. Первый вход блока индикаторов заявляемого устройства соединен с третьим входом блока режимов работы, ко второму входу блока индикаторов подключен шестой выход блока ввода ответных действий обучаемого, третий вход блока индикаторов соединен с первым выходом блока управления сбросом, к четвертому входу блока индикаторов подключен первый выход блока режимов работы, к пятому входу - четвертый выход блока режимов работы, шестой вход блока индикаторов соединен со вторым выходом блока режимов работы, седьмой, восьмой, десятый, одиннадцатый входы блока индикаторов соединены соответственно со вторым, первым, третьим и четвертым выходами формирователя пароля, девятый вход блока индикаторов и седьмой вход формирователя пароля подключены к выходу блока равенства, двенадцатый вход блока индикаторов связан с первым выходом блока ввода ответных действий обучаемого. Пятый выход блока режимов работы соединен с четвертым входом блока управления повторами, шестой выход блока режимов работы соединен с пятым, а седьмой с четвертым входами блока равенства, восьмой выход блока режимов работы связан с третьим входом коммутатора. Выход первого блока памяти, четвертый вход четвертого блока памяти и седьмой вход пятого блока памяти служат для подключения к компьютеру. Входами блока ввода ответных действий обучаемого являются клавиши клавиатуры компьютера, а его выходы связаны через шифратор, входящий в этот блок, с соответствующими на этой клавиатуре клавишами.

Таким образом, заявляемое устройство отличается от прототипа тем, что оно дополнительно содержит пять блоков памяти, блок равенства, блок управления повторами, преобразователь ответа без учета порядка, преобразователь кодов, блок управления сбросом, а также наличием новых связей между блоками, обеспечивающих функционирование устройства в режимах контроля и самоконтроля знаний обучаемых.

Отличия от прототипа подтверждают новизну заявляемого устройства.

За счет введения новых блоков, новых связей между блоками обеспечена возможность хранения всей введенной информации, а также обеспечено управление повторами вводимых знаков, повышена информативность пароля, повышена кодовая избыточность и множественность ответов на каждый код задания. Кроме этого, предложенная схема устройства допускает распознавание правильности ответов со сложной логистикой, задаваемыми булевыми функциями. Все это расширяет логико-дидактические возможности устройства и его эксплуатационные характеристики.

В заявляемом устройстве предусмотрено подключение к компьютеру. Возможность компьютерной обработки вводимой в устройство информации расширяет его эксплуатационные характеристики и область применения, позволяет обучаемым осуществлять самоконтроль и внешний контроль знаний, что очень важно при дистанционном обучении. Автоматизированный контроль в свою очередь повышает качество обучения при любых формах обучения.

Заявителю не известны из источников информации устройства, аналогичные заявляемому, оно явным образом не следует из уровня техники, что позволяет судить о наличии \изобретательского уровня\.

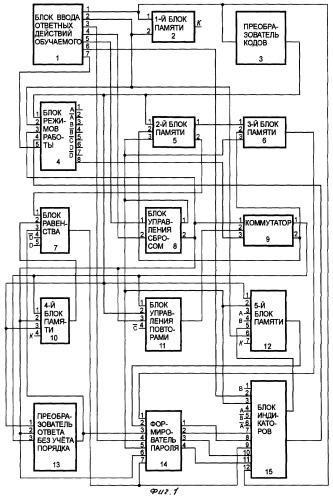

На фиг.1 изображена блок-схема заявляемого устройства, на фиг.2-13 приведены структурные схемы отдельных входящих в это устройство блоков.

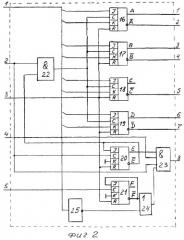

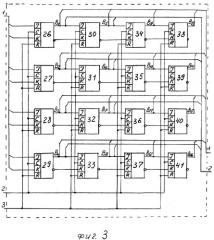

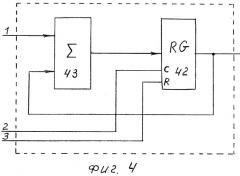

На фиг.2 представлена схема блока режимов работы, на фиг.3 - второго блока памяти, на фиг.4 - третьего блока памяти, на фиг.5 - схема блока равенства. На фиг.6 приведена структурная схема блока управления сбросом, на фиг.7 - схема коммутатора, на фиг.8 - четвертого блока памяти, на фиг.9 - блока управления повторами, на фиг.10 - пятого блока памяти, на фиг.11 - преобразователя ответа без учета порядка, на фиг.12 - формирователя пароля, на фиг.13 - блока индикаторов.

Устройство (фиг.1) содержит блок ввода ответных действий обучаемого 1, первый блок памяти 2, преобразователь кодов 3, блок режимов работы 4, второй блок памяти 5, третий блок памяти 6, блок равенства 7, блок управления сбросом 8, коммутатор 9, четвертый блок памяти 10, блок управления повторами 11, пятый блок памяти 12, преобразователь ответа без учета порядка 13, формирователь пароля 14 и блок индикаторов 15.

Для ввода цифр и букв русского и латинского алфавитов служит стандартная компьютерная клавиатура, клавиши которой являются входами блока ввода ответных действий обучаемого 1. Этот блок 1 содержит также шифратор, на выход которого поступают восьмизначные двоичные коды. Блок 1 имеет семь выходов. Первый его выход является информационным и соединен с первым входом блока памяти 2 и с входом преобразователя кода 3. Второй выход является выходом синхронизации, на котором одновременно с появлением на первом выходе восьмизначного двоичного кода при нажатии клавиши, соответствующей определенной букве или цифре, формируется прямоугольный импульс синхронизации (синхроимпульс). Остальные пять выходов, 3, 4, 5, 6, 7, блока 1 - управляющие, они соответствуют клавишам: \Контроль\, \Общий сброс\, \Частный сброс\, \Пароль\, \Точка\. При нажатии этих клавиш на соответствующем управляющем выходе блока 1 формируется прямоугольный импульс, а на первом выходе - соответствующий восьмизначный параллельный двоичный код.

Первый блок памяти 2 последовательно соединен с блоком ввода ответных действий обучаемого и представляет собой запоминающее устройство, предназначенное для сбора и хранения всей информации, вводимой обучаемым с помощью клавиш клавиатуры. Выход блока 2 предназначен для подключения к компьютеру. Таким образом, вся информация, хранящаяся в блоке памяти, 2 после окончания работы может быть передана в компьютер, тем самым обеспечена возможность компьютерной обработки результатов самостоятельной работы обучаемого.

Преобразователь кодов 3 соединен с блоком ввода ответных действий обучаемого 1 (фиг.1) и представляет собой комбинационную логическую схему, преобразующую входные восьмизначные двоичные коды в двоичные коды меньшей длины. Один из вариантов выполнения логической схемы преобразователя кодов 3 может быть реализован в соответствии с таблицей 1.

| Таблица 1 | |||

| Название клавишей компьютера | Двоичный код на выходе преобразователя кодов | ||

| Русские буквы | Латинские буквы | Цифры и служебные знаки | |

| А а | A a Q q | 00000 | |

| Б б Р р | В b R r | 00001 | |

| В в С с | С с S s | 00010 | |

| Г г Т т | D d T t | 00011 | |

| Д д У у | Е е U u | 00100 | |

| Е е Ф ф | F f V v | 1 | 00101 |

| Ж ж Х х | G g W w | 2 | 00110 |

| 3 з Ц ц | H h X х | 3 | 00111 |

| И и Ч ч | I I Y у | 4 | 01000 |

| Й й Ш ш | J j Z z | 5 | 01001 |

| К к Щ щ | К k | 6 | 01010 |

| Л л Ъ ъ | L l | 7 | 01011 |

| М м Ы ы Ь ь | M m | 8 | 01100 |

| Н н Э э | N n | 9 | 01101 |

| О о Ю ю | O о | 0 | 01110 |

| П п Я я | Р р | 01111 | |

| ; | 11001 | ||

| + | 11010 | ||

| × | 11011 | ||

| , | 11100 | ||

| ( | 11110 | ||

| ) | 11111 |

Соответственно этим пятизначным двоичным кодам, поступающим на выход преобразователя кодов 3, представлены и схемы блока режимов работы (фиг.2), второго блока памяти (фиг.3), четвертого блока памяти (фиг.8), пятого блока памяти (фиг.10), блока управления повторами (фиг.9), преобразователя ответа без учета порядка (фиг.11), входы которых связаны с выходом преобразователя кодов 3.

Возможны и другие варианты выполнения преобразователя кодов 3, когда входные восьмизначные двоичные коды преобразуются в двоичные коды иной длины (не пятизначные). Сущность изобретения при этом не меняется.

Блок режимов работы 4 (фиг.2) содержит двоичный регистр, образованный триггерами 16, 17, 18, 19, обозначенными буквами А, В, С, D, триггеры 20, 21, обозначенные соответственно как Е, F, схему И 22, элемент совпадения 23, элемент ИЛИ 24 и инвертор 25.

Первый вход блока режимов 4 соединен с выходом преобразователя кодов 3 (фиг.1), с которого поступают четырехзначные двоичные коды (в параллельном виде) на единичные входы J и нулевые входы К триггеров (фиг.2).

Второй вход блока режимов работы 4 соединен со вторым выходом (выходом синхронизации) блока ввода ответных действий обучаемого 1 (фиг.1). Первый синхроимпульс, поступивший с этого выхода, перепишет подаваемые коды в регистр блока 4 и одновременно переведет в единичное состояние триггер 20. В результате схема И 22 окажется запертой, и в дальнейшем число в регистре меняться не будет. Первый синхроимпульс не пройдет на восьмой выход блока режимов работы благодаря элементу совпадения 23.

Четвертый вход блока режимов работы 4 подключен ко второму выходу блока индикаторов 15 (фиг.1). Пока на этом входе поддерживается высокий уровень, а триггер 21 (фиг.2) находится в нулевом состоянии, все синхроимпульсы, кроме первого, поступающие на второй вход блока 4 со второго выхода блока ввода ответных действий обучаемого 1, будут проходить на его восьмой выход, который соединен с третьим входом коммутатора 9 (фиг.1).

Пятый вход блока режимов работы 4 соединен с седьмым (управляющим) выходом блока ввода ответных действий обучаемого 1 (фиг.1), соответствующим клавише \Точка\. Синхроимпульс, поступающий на этот пятый вход, переводит в единичное состояние триггер 21, благодаря чему на первый вход элемента ИЛИ 24 поступит низкий уровень. После этого на восьмой выход блока режимов работы 4 при нажатии клавишей, соответствующих служебным знакам по таблице 1, синхроимпульсы проходить не будут.

Третий вход блока режимов работы 4 подключен ко второму выходу блока управления сбросом 8 (фиг.1). По этому входу все триггеры 16-21 блока режимов работы 4 (фиг.2) низким уровнем напряжения, подаваемым со второго выхода блока 8, устанавливаются в нулевое состояние.

При помощи триггеров 16-19 задаются режимы работы всего устройства. Всего возможно 16 режимов, которые отражены в таблице 2.

| Таблица 2 | ||||||

| Номер режима | Двоичные коды номера режима | Учитываются | Оценка ответа | Вывод пароля | ||

| порядок ввода знаков ответа | повторы знаков вводимого ответа | в системе \Правильно-неправильно\ | по многобалльной шкале \0-15\ | |||

| 0 | 0000 | да | да | да | нет | да |

| 1 | 0001 | нет | да | да | нет | да |

| 2 | 0010 | да | нет | да | нет | да |

| 3 | 0011 | нет | нет | да | нет | да |

| 4 | 0100 | да | да | нет | нет | да |

| 5 | 0101 | нет | да | нет | нет | да |

| 6 | 0110 | да | нет | нет | нет | да |

| 7 | 0111 | нет | нет | нет | нет | да |

| 8 | 1000 | да | да | да | да | да |

| 9 | 1001 | нет | да | да | да | да |

| 10 | 1010 | да | нет | да | да | да |

| 11 | 1011 | нет | нет | да | да | да |

| 12 | 1100 | да | да | нет | нет | да |

| 13 | 1101 | нет | да | нет | нет | да |

| 14 | 1110 | да | нет | нет | нет | да |

| 15 | 1111 | нет | нет | нет | нет | да |

В режимах под номерами 0, 1, 2, 3 задание состоит из одного кода, работают индикаторы \Правильно-неправильно\.

В режимах 4, 5, 6, 7 задание состоит из одного кода, индикаторы \Правильно-неправильно\ не горят. Самоконтроль производится по паролю.

В режимах 8, 9, 10, 11 осуществляется внешний контроль в сочетании с самоконтролем.

В режимах 12, 13, 14, 15 выполняется внешний контроль без самоконтроля.

Второй блок памяти 5 (фиг.3) представляет собой шестнадцатиразрядный сдвиговый регистр, образованный триггерами 26, 27, 28, 29, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 40, 41. Первый вход второго блока памяти 5 (фиг.1) соединен с выходом преобразователя кодов 3. Второй вход второго блока памяти 5 соединен со вторым выходом коммутатора 9. С выхода блока 3 поступает четырехзначное число, которое под действием синхроимпульса, поступившего с выхода коммутатора 9, записывается в параллельном виде в первые четыре триггера 26, 27, 28, 29 блока 5 (фиг.3). Второе поступившее число с выхода преобразователя кодов 3 записывается в эти же триггеры, но при этом первое переписывается в триггеры 30, 31, 32, 33 и так далее. Таким образом второй блок памяти 5 представляет собой сдвиговый регистр, сдвигающий число одним импульсом на четыре разряда. Регистр является разомкнутым: число, хранящееся в триггерах 38, 39, 40, 41, под действием очередного синхроимпульса стирается. Второй блок памяти 5 имеет два выхода, на первый из которых (фиг.3) поступает шестнадцатизначное число в параллельном виде, на второй - восьмизначное число, хранящееся в первой половине регистра (триггеры 26, 27, 28, 29, 30, 31, 32, 33). Третий вход второго блока памяти 5 соединен с первым выходом блока управления сбросом 8 (фиг.1). Все триггеры блока 5 устанавливаются в нулевое положение низким уровнем напряжения, подаваемым с первого выхода блока 8.

Третий блок памяти 6 (фиг.4) содержит восьмиразрядный регистр 42 и сумматор 43. На первый вход блока памяти 6, который соединен с первым выходом второго блока памяти 5, поступают числа из первой половины сдвигового регистра блока 5. Эти числа поступают на первый вход сумматора 43 (фиг.4), на второй вход которого поступают числа из регистра 42. Второй вход третьего блока памяти 6 соединен со вторым выходом коммутатора 9 (фиг.1). Под действием синхроимпульса, подаваемого со второго выхода коммутатора 9, входное число суммируется с числом, хранящимся в регистре 42 третьего блока памяти 6, и сумма записывается в этот же регистр с одновременным стиранием прежнего числа. Третий вход третьего блока памяти 6 соединен с первым выходом блока управления сбросом 8 (фиг.1). По третьему входу регистр 42 (фиг.4) устанавливается в нулевое состояние.

Блок равенства 7 (фиг.5) содержит две схемы равенства 44, 45 и логическую схему 46. Первый вход блока равенства 7 соединен со вторым выходом второго блока памяти 5 (фиг.1). Второй вход блока равенства 7 соединен с выходом четвертого блока памяти 10, третий вход - с выходом преобразователя ответа без учета порядка 13, четвертый и пятый входы - с инверсным и прямым выходами соответственно триггера D блока режимов работы 4 (фиг.1). На первый вход блока 7 поступает число из первой половины сдвигового регистра блока памяти 5. Оно подается на обе схемы равенства 44, 45 (фиг.4). Схема 44 сравнивает это число с числом, поступившим с выхода четвертого блока памяти 10, схема 45 сравнивает с числом, поступившим с выхода преобразователя ответа без учета порядка 13. Результат сравнения поступает на выход блока равенства 7. Выбор схемы равенства при этом определяется состоянием триггера D блока режимов работы 4.

Блок управления сбросом 8 (фиг.6) состоит из инверторов 47, 48 и схемы И 49. Первый вход блока 8 соединен с пятым (управляющим) выходом блока ввода ответных действий обучаемого 1, соответствующим клавише \Частный сброс\, а второй вход - с четвертым выходом блока 1, соответствующим клавише \Общий сброс\ (фиг.1). Назначение блока 8 - формировать низкие уровни напряжения при нажатии этих клавиш. При не нажатых клавишах на входы инверторов 47 и 48 подаются низкие уровни напряжения, поэтому на выходе схемы И 49 и соответственно на обоих выходах блока 8 будут поддерживаться высокие уровни напряжения. При нажатии клавиши \Общий сброс\ низкий уровень напряжения появится на обоих выходах блока 8, при нажатии клавиши \Частный сброс\ - лишь на втором выходе блока 8, а на первом выходе будет поддерживаться высокий уровень напряжения.

Коммутатор 9 (фиг.7) содержит два триггера 50, 51 и два логических элемента И 52 и 53. Первый вход коммутатора 9 (фиг.1) соединен со вторым выходом блока управления сбросом 8, по этому входу он устанавливается в нулевое состояние. Второй вход коммутатора 9 соединен с выходом блока управления повторами 11 (фиг.1), который управляет повторами знаков ответа. Если повторы запрещены, то схема И 52 заперта, и синхроимпульсы, поступающие на третий вход коммутатора 9 с восьмого выхода блока режимов работы 4, не проходят на его первый выход. Первым синхроимпульсом переводится в единичное состояние триггер 51 (фиг.7). Второй синхроимпульс проходит на второй выход коммутатора 9 и переводит в единичное состояние триггер 50. С этого момента все синхроимпульсы, поступающие на третий вход коммутатора 9, проходят только на первый выход коммутатора 9. Таким образом, коммутатор 9 первые два импульса отправляет только на второй выход, а все остальные - только на первый.

Четвертый блок памяти 10 (фиг.8) содержит собственно запоминающее устройство (ЗУ) 54 и регистр адреса (RG) 55. Запоминающее устройство должно быть большой емкости. Допустим, его емкость равна 4096 байт. Тогда его адресом будет двенадцатиразрядное двоичное число. Адрес состоит из двух частей. Первую часть образуют восьмизначные числа, поступающие с выхода ЗУ 54 на вход восьмиразрядного регистра 55. Вторая часть состоит из четырех двоичных знаков. Это четырехзначное число поступает на третий вход четвертого блока памяти 10 с выхода блока преобразователя кодов 3. Второй вход четвертого блока памяти 10 соединен со вторым выходом блока управления сбросом 8 (фиг.1). По второму входу регистр 55 блока памяти 10 устанавливается в нулевое состояние. Первый вход блока 10 соединен с первым выходом коммутатора 9 (фиг.1), с которого подаются синхроимпульсы. Под действием каждого синхроимпульса на выход четвертого блока памяти поступает восьмизначное двоичное число в параллельном виде, снимаемое с выхода ЗУ 54 блока 10. Это число подается в блок равенства 7, второй вход которого соединен с выходом четвертого блока памяти 10. Четвертый вход блока памяти 10 предназначен для подключения к компьютеру.

Блок управления повторами 11 (фиг.9) содержит дешифратор 56, блок 57 из шестнадцати триггеров и логических элементов И, и элемент ИЛИ 58. Третий вход блока управления повторами 11, по которому все триггеры устанавливаются в нулевое состояние, соединен со вторым выходом блока управления сбросом 8 (фиг.1). Первый вход блока 11, на который подаются синхроимпульсы, соединен с первым выходом коммутатора 9. На второй вход поступают четырехзначные двоичные числа с выхода преобразователя кодов 3 (фиг.1). Четвертый вход блока 11 соединен с пятым выходом блока режимов работы 4. Если триггер 18 (фиг.2) блока режимов работы 4 находится в нулевом состоянии, то на четвертом входе блока 11 поддерживается высокий уровень напряжения, благодаря чему на выходе элемента ИЛИ 58 (фиг.9) также будет высокий уровень напряжения независимо от состояния триггеров блока управления повторами 11. Если же триггер 18 (фиг.2) блока режимов работы 4 переведен в единичное состояние, то уровень напряжения на выходе блока 11 будет определяться состоянием триггеров блока 57 (фиг.9). Допустим, что на второй вход блока управления повторами 11 поступило двоичное число 0010. Тогда под действием синхроимпульса триггер С2 блока 57 (фиг.9) перейдет в единичное состояние. На выходе блока управления повторами 11 на момент действия синхроимпульса будет неизменным высокий уровень напряжения. Если на второй вход блока 11 подать еще раз то же самое число 0010, то на этот раз на выходе блока 11 будет низкий уровень напряжения, так как триггер С2 находится в единичном состоянии, а его инверсный выход, подключенный к входу соответствующей схемы И, поддерживает на ее выходе низкий уровень напряжения. Таким образом, при подаче на второй вход блока управления повторами 11 повторного кода синхроимпульс не проходит на первый выход коммутатора 9, так как схема И 52 (фиг.7) оказывается запертой низким уровнем напряжения, поступившего с выхода блока 11 на второй вход коммутатора 9. В результате этого повторное нажатие одной и той же клавиши не изменит результат работы всего устройства.

Пятый блок памяти 12 (фиг.10) содержит запоминающее устройство 61, два триггерных регистра 60, 62 и логический элемент И 59. В запоминающем устройстве 61 хранятся \секретные\ коды, которые записываются при помощи компьютера по седьмому входу пятого блока памяти 12. Емкость запоминающего устройства может быть любой. Но лучший вариант - большая емкость. Допустим, она такая же, как емкость запоминающего устройства 54 четвертого блока памяти 10 (фиг.8), - 4096 байт. Регистр 60 (фиг.10) пятого блока памяти 12 представляет собой двенадцатиразрядный сдвиговый регистр. По первому входу блока 12 в этот регистр записывается четырехзначное число с выхода преобразователя кодов 3 (фиг.1). Это число занимает четыре триггера регистра 60. Под действием синхроимпульса первое число сдвигается одновременно на четыре разряда, а на его место записывается новое число. Выход регистра 60 подключен к адресным входам запоминающего устройства 61, выход которого присоединен к входам регистра 62 (фиг.10). Регистр 62 представляет собой двадцатичетырехразрядный сдвиговый регистр, сдвигающий число под действием каждого синхроимпульса на восемь разрядов с одновременной записью нового восьмизначного числа на место прежнего. По второму входу пятого блока памяти 12, который соединен с первым выходом блока управления сбросом 8, регистры 60 и 62 устанавливаются в нулевое состояние. Синхроимпульсы поступают на шестой вход блока 12 со второго выхода блока ввода ответных действий обучаемого 1 (фиг.1). Но не каждый из них пройдет на синхровходы регистров 60 и 62 блока 12, так как они поступают на один из четырех входов логического элемента И 59. Работа регистров 60 и 62 возможна лишь в том случае, если триггеры 16 и 17 блока режимов работы 4 (фиг.2), с которыми связаны третий и четвертый входы блока 12, будут установлены в единичное состояние, благодаря чему на третьем и четвертом входах блока 12 окажутся высокие уровни напряжения, а также в том случае, если с первого выхода блока индикаторов 15 на пятый вход блока 12 поступит высокий уровень напряжения. Седьмой вход пятого блока памяти 12 предназначен для подключения к компьютеру, чтобы сменить информацию запоминающего устройства 61.

Преобразователь ответа без учета порядка 13 (фиг.11) содержит сумматор 63 и триггерный восьмиразрядный регистр 64. Первый вход преобразователя 13 соединен с выходом преобразователя кодов 3, с которого поступает четырехзначное двоичное число. Перед подачей его на первый вход сумматора 63 оно преобразуется в восьмизначное двоичное число путем записи нулей между его цифрами. Например, число 0110 преобразуется в число 00010100, число 1011 - в число 001000101 и т.д. На второй вход сумматора 63 с выхода регистра 64 (фиг.11) подается шестнадцатиразрядное двоичное число. При подаче импульсов на третий вход преобразователя ответа без учета порядка 13 в регистре 64 накапливается арифметическая сумма поступающих на первый вход преобразователя 13 чисел. Эта сумма поступает на третий вход блока равенства 7 и на третий вход формирователя пароля 14 (фиг.1). Второй вход преобразователя ответа без учета порядка 13 соединен со вторым выходом блока управления сбросом 8 (фиг.1). По этому входу регистр 64 преобразователя 13 устанавливается в нулевое состояние.

Формирователь пароля 14 (фиг.12) содержит логические элементы И 65 и 71, счетчик 66, дешифратор 67, регистр 68 из шестнадцати триггеров, обозначенных D0-D15, сумматоры 69, 72 и триггер 70. Пароль формируется в результате суммирования четырех чисел. Первое число поступает на первый вход формирователя пароля 14 с выхода третьего блока памяти 6. Второе число подается на второй вход формирователя пароля 14 с выхода пятого блока памяти 12. Третье число поступает с выхода преобразователя ответа без учета порядка 13. Эти три числа поступают на входы сумматора 69. Результат сложения трех чисел подается на сумматор 72, складывающий числа по модулю 2. Второе слагаемое сумматора 72 снимается с регистра 68. В этом регистре хранятся дихотомические оценки ответов на отдельные вопросы задания. Так как регистр 68 содержит шестнадцать триггеров, то задание может насчитывать также до 16 вопросов. При нажатии клавиши \Контроль\ с третьего выхода блока ввода ответных действий обучаемого 1 на четвертый вход формирователя пароля 14 поступает прямоугольный импульс. Он проходит через элемент И 65 на вход счетчика 66, на синхровход триггера 70 и на вход элемента И 71 (фиг.12). Под действием этого импульса в счетчике 66 увеличивается на единицу число, переходит в единичное состояние триггер 70, благодаря чему запирается элемент И 65, и вторичное нажатие клавиши \Контроль\ никаких изменений в устройстве не произведет. Если с выхода блока равенства 7 на седьмой вход формирователя пароля 14 подается высокий уровень напряжения (фиг.1), что соответствует ответу \правильно\, то соответствующий триггер регистра 68 (фиг.12) переходит в единичное состояние. Чтобы ответить на второй вопрос, необходимо нажать клавишу \Частный сброс\ блока ввода ответных действий обучаемого 1. Тогда со второго выхода блока управления сбросом 8 на шестой вход триггера 70 формирователя пароля 14 поступит низкий уровень нап