Устройство программного управления

Иллюстрации

Показать всеУстройство относится к автоматике и вычислительной технике и может быть использовано в качестве ядра микроконтроллерной или микропроцессорной системы (М-системы) обработки информации и управления в реальном времени с поддержкой режима аппаратного сторожевого таймера для перезапуска М-системы при "зависании" прикладной программы устройства. Техническим результатом является сокращения напрасных потерь рабочего времени устройства при каждом "зависании" его прикладной программы или кратковременном возникновении сигнала аварии основного источника питания за счет автоматического перезапуска устройства по импульсу сброса, который генерируется в процессе аппаратного обнаружения любого из этих событий и исключения тестирования М-системы при идентификации события как кратковременной аварии основного источника напряжения питания. Устройство содержит блок программного управления, управляющие входы и выходы, кодовый выход адреса и двунаправленную кодовую шину данных системой магистрали, входы сигналов сброса и аварии основного источника напряжения питания, источник коммутируемого напряжения, шину основного источника напряжения питания и шину резервного источника напряжения питания, технологический управляющий вход, пороговый элемент, прерыватель и управляемый формирователь импульсов. 3 ил.

Реферат

Изобретение относится к автоматике и вычислительной технике, предназначено для выполнения требуемых функций программного управления с автоматическим перезапуском при «зависании» прикладной программы и автоматическим переходом в режим сохранения оперативной информации с помощью резервного источника напряжения питания при отключении или аварии основного источника напряжения питания и может быть использовано, например, в качестве ядра микроконтроллерной или микропроцессорной системы (М-системы) обработки информации и управления в реальном времени с поддержкой режима аппаратного сторожевого таймера для перезапуска при «зависании» прикладной программы М-системы, проектируемой с учетом следующих основных принципов [1]: программного управления, магистрального обмена информацией, модульного построения и наращивания вычислительной мощности.

Современная типовая М-система содержит модуль устройства программного управления на основе микроконтроллера (МК) или микропроцессора (МП), модули функционально ориентированных контроллеров и модемов для ввода-вывода информации в процессе взаимодействия М-системы с внешними объектами (пультом оператора, датчиками событий в объекте управления, исполнительными устройствами, смежными системами и т.п.), блок питания и системную магистраль, образованную шинами управления (ШУ), адреса (ША) и данных (ШД), для обмена информацией между модулями (функционально законченными составными частями М-системы) в процессе функционирования М-системы [2, с.14, рис.1.1].

В общем случае модуль устройства программного управления содержит блок программного управления, образованный автономной памятью, например комбинированной (ОЗУ+ПЗУ+РПЗУ), и вычислителем (содержит, например, МК, кварцевый резонатор и два конденсатора для обеспечения работы внутреннего генератора синхроимпульсов МК [2, с.63, рис.2.6 а], внутреннюю магистраль, входы и выходы ШУ, выходы ША и двунаправленную ШД системной магистрали, приемопередатчики и адаптер магистралей для функционально ориентированного сопряжения МК с внутренней и системной магистралями), и «вспомогательные» схемы (в [2] они не показаны) для управления блоком программного управления при возникновении ряда событий, например включении и выключении блока питания, замыкании на корпус кнопки системного сброса на пульте оператора и т.п.

Одним из эффективных современных МК является байтовый МК AT89S8252 фирмы «Atmel», созданный по усовершенствованной технологии КМОП на основе популярной архитектуры MCS-51 со следующими основными характеристиками: напряжение питания в рабочем режиме от 4 до 6 В при потребляемом токе не более 25 мА, при частоте функционирования 12 МГц, а в режиме микропотребления не менее 2 В и токе потребления 40 мкА (или 100 мкА) при напряжении питания 3В (или 6В); частота функционирования до 24 МГц в диапазоне рабочих температур от -40°С до +85°С; память: РПЗУ (8 Кбайт flash-памяти + 2 Кбайт EEPROM-памяти с электрической перезаписью) + ОЗУ емкостью 256 байт + блок регистров специальных функций (аккумулятор АСС, регистр В для расширения аккумулятора, слово состояния программы PSW, регистр-указатель стека SP, два регистра указателя данных DPTR, четыре байтовых регистра защелки портов Р0, P1, P2 и Р3, регистр IR приоритетов, регистр IE масок прерываний, три таймера/счетчика Т/С0, Т/С1 и Т/С2, регистр T2CON управления таймером/счетчиком 2, регистр SCON управления приемопередатчиком, регистр PCON управления мощностью, регистры SPCR и SPSR управления последовательным синхронным интерфейсом SPI, Watchdog-сторожевой таймер, регистр WMCON управления сторожевым таймером, памятью EEPROM и выбором регистра DPTR); четыре байтовых параллельных порта ввода/вывода Р0(7:0), Р1(7:0), Р2(7:0) и Р3(7:0), причем при записи всех «1» в регистр-защелку порта Р3(7:0) все биты этого порта используются для выполнения альтернативных функций (P3.7=NRD - выходной инверсный сигнал чтения; P3.6=NWR - выходной инверсный сигнал записи; Р3.5=Т1 и Р3.4=Т0 - импульсные входы Т/С1 и Т/С0 соответственно; P3.3=NQ1 и P3.2=NQ0 - соответственно второй и первый входы прерываний, сигнал каждого из которых воспринимается как низкий уровень или срез; P3.1=TXD и P3.0=RXD - соответственно вход и выход последовательного интерфейса типа RS-232C), аналогично все биты порта Р1(7:0), кроме Р1.2 и Р1.3, имеют также альтернативные функции (P1.7=SCK, P1.6=MISO, P1.5=MOSI и P1.4=NSS - соответственно синхросигнал, последовательный вход, последовательный выход и внешний инверсный строб синхронного последовательного интерфейса SPI; Р1.1=Т2ЕХ и Р1.0=Т2 - соответственно выход триггера и импульсный вход Т/С2).

При каждом включении блока питания генерируется импульс сброса RST, по окончании которого составные части М-системы приводятся в рабочее состояние (сбрасываются, инициализируются и тестируются), а затем в общем случае М-система выполняет с разделением во времени несколько функций управления. Эти функции обычно реализуются циклически как взаимодействующие квазипараллельные процессы [2, с.18-34] на временной сетке с некоторым элементарным интервалом времени, формируемым в МК соответствующим таймер/счетчиком в режиме счета внутренних импульсов.

При немгновенных отказах блока питания М-системы сохранность содержимого ОЗУ МК можно обеспечить с помощью маломощного источника (аккумуляторного или батарейного) резервного напряжения питания Ер путем прерывания по инверсному сигналу NAIP аварии источника основного напряжения питания Еп. Для этого МК по сигналу NAIP=0 прерывания должен перезагрузить в ОЗУ все основные параметры прерванного процесса функционирования и по последней команде установить в регистре PCON бит PD перехода в режим микропотребления (Power down) [3, с.83]. Таким образом, при введении в состав М-системы источника резервного питания Ер относительно легко построить устройство программного управления с энергонезависимым ОЗУ современного МК типа AT89S8252. В этом случае МК питается от источника коммутируемого напряжения Ек, функционирующего по напряжениям Еп и Ер. При выключении или аварии блока питания это событие в М-системе обнаруживается изменением сигнала NAIP из «1» в «0», запускающего прерывающую подпрограмму перевода МК в режим микропотребления при напряжении питания Ек≥4В с сохранением содержимого ОЗУ при последующем снижении напряжения питания МК вплоть до Ек≥2В. При каждом включении блока питания исправной М-системы МК выводится из режима микропотребления с полным сохранением содержимого ОЗУ, если импульс сброса RST=1 формируется не раньше, чем Ек достигнет своего нормального уровня Ек≥4В [4, с.75].

Однако в общем случае, например, при кратковременных изменениях напряжения первичной сети блока питания (например, напряжения 27В борт-сети) напряжение Еп также будет изменяться, и при достижении аварийного уровня (например, меньше 4,5В или больше 5,5В) М-система отработает это событие и сначала переведет МК в режим микропотребления, а затем - в рабочий режим по импульсу RST сброса с затратой времени на инициализацию М-системы и тестирование, т.е. с потерей рабочего времени на тестирование, занимающее значительный отрезок времени (от нескольких десятков секунд до нескольких минут).

Кроме того, в реальных условиях функционирования М-система как сложный цифровой автомат с оперативной и постоянной памятью подвержена сбоям, приводящим, в частности, к «зависанию» прикладной программы устройства программного управления. В этой связи сторожевой таймер (Watchdog) приобретает все большую популярность у производителей МК. Например, в МК AT89S8252 сторожевой таймер при включении аппаратуры инициализируется записью в регистр WMCON кода PS[2:0] периода срабатывания таймера и бита WDTRST включения/сброса и предназначен для формирования внутреннего сигнала сброса МК на программно-аппаратном уровне (при WDTRST=1), если прикладная программа выполняет неконтролируемые действия, например «зависла» [2, с.107, 108].

Однако встроенный в МК аппаратно-программный сторожевой таймер хотя и полезен, но в общем случае не позволяет полностью исключить возможность «зависания» М-системы, поскольку при сбое-сбросе в МК бита WDTRST сторожевой таймер отключается и не препятствует «зависанию» МК по другим сбоям. Сбои возникают как следствие внутренних и/или внешних помех, приводят к функциональным нарушениям работы МК, которые полностью устраняются при перезапуске МК по сигналу RST сброса. Кроме того, при сбое-установке в регистре PCON бита PD (или EDL) управления режимом микропотребления (или холостого хода) МК «зависает» вообще (или на время отсутствия прерывания) - см. [2, с.94, 95], причем выход из режима микропотребления может быть осуществлен только подачей на вход активного импульса RST длительностью tRST, определяемой ограничением

Таким образом, при построении типовой современной М-системы обработки информации и управления в реальном времени, обслуживаемой с оперативным доступом к кнопке СБРОС (RESET), и особенно не обслуживаемой со сбросом только при включении основного напряжения питания Еп и доступом к кнопке СБРОС только в процессе отладки, актуальной является задача надежного автоматического обнаружения двух событий (кратковременной аварии блока питания и «зависания» прикладной программы устройства программного управления) и обеспечения рациональной подпрограммы перезапуска М-системы по каждому событию. В этой связи создание простого устройства программного управления с сохраняемой оперативной памятью при отключении основного напряжения питания и надежным обнаружением кратковременной аварии блока питания или «зависания» прикладной программы (например, за счет обнаружения пропуска импульса или «зависания» (прекращения изменения) импульсного сигнала, формируемого во времени программно вычислителем в качестве функции временной сетки работы М-системы) и обеспечением по каждому из этих событий рациональной подпрограммы перезапуска М-системы, является, на наш взгляд, актуальной технической проблемой.

Создание устройств программного управления с сохраняемой оперативной памятью, как правило, производится на разделении устройства на вычислитель (на основе МК или МП, либо другого устройства, например, типа [5, 6], реализованного с помощью программируемой логической интегральной схемы (ПЛИС)) и автономную оперативную память с сохранением информации, например, типа [7] с блоком питания, либо типа [8, 9] с коммутируемым источником напряжения Ек питания, функционирующим от основного напряжения Еп блока питания или от резервного источника напряжения Ер при выключении или аварии блока питания с устройством контроля, например, типа [10].

Основными недостатками известных устройств программного управления в реальном времени с раздельными вычислителем и автономной оперативной памятью с сохранением информации при построении их на современной элементной базе являются сложность (обусловлена недостаточно полным использованием функциональных возможностей составных частей вычислителя, например его МК с сохранением информации в ОЗУ в режиме микропотребления) и значительная напрасная потеря рабочего времени как из-за «зависания» прикладной программы (при соответствующих сбоях МК из-за внешних и/или внутренних помех даже при наличии в МК аппаратно-программного сторожевого таймера) при отсутствии средств гарантированного автоматического перезапуска М-системы при «зависании», так и на тестирование (от десятков секунд до нескольких минут) при возникновении сигнала NAIP=0 аварии источника питания при каждом кратковременном (при длительности несколько сотен миллисекунд) аварийном изменении уровня напряжения сети (например, напряжения 27 В борт-сети), что обусловлено отработкой вычислителем каждого фронта сигнала NAIP=1 без учета предыстории уровня основного напряжения питания Еп при NAIP=0.

На основании изложенного выше можно сказать, что применение любого устройства программного управления с принципиальной возможностью потери работоспособности в течение длительного времени (из-за неустранимого автоматически «зависания» вычислителя или выполнения программы тестирования при каждом кратковременном появлении сигнала NAIP=0) может приводить к нежелательным (непредсказуемым) последствиям при управлении, например, сложным технологическим процессом в реальном времени.

Известно устройство [11], реализующее создание устройства программного управления с раздельным питанием вычислителя и автономной оперативной памяти с сохранением информации. Устройство [11] содержит датчик сетевого напряжения, первый и второй ключевые элементы, элемент задержки, элемент НЕ, первый и второй элементы И, элемент «Равнозначности», шину сетевого напряжения, соединенную с входами датчика и обоих ключевых элементов, вход управления, являющийся первым входом первого элемента И, второй вход которого через элемент НЕ связан с выходом элемента задержки, показанный в виде входов накопитель (оперативную память с сохранением информации) с источником питания, выходы которого соединены с первыми входами элемента «Равнозначности», выход которого соединен с входом первого ключевого элемента, показанный в виде входов вычислитель с источником питания, выходы которого соединены с первыми входами второго элемента И, выход которого соединен с управляющим входом второго ключевого элемента, выход первого элемента И соединен с последними входами элемента «Равнозначности» и второго элемента И, а выходы первого и второго ключевых элементов соединены с входами источников питания вычислителя и накопителя соответственно, и выход сигнала «Авария сети» (АС), соединенный с входом элемента задержки и соответствующим входом вычислителя.

В исходном выключенном состоянии на вход управления подается сигнал логического «0», ключевые элементы закрыты, напряжение питающей сети не подается на источники питания вычислителя и накопителя, а при включении, обнаружении аварии сети и выключении устройство работает соответственно по программам включения, выключения при аварии питающей сети и выключения следующим образом.

При подаче сетевого питания и включении устройства первый и второй элементы И и элемент «Равнозначности» вырабатывают соответственно цифровые сигналы X1, Х2, Х3 согласно выражениям

Х1=В&NAC(Тз),

X2=X1&PB1&...&PBq,

X3=X1#PH1#...#PHk,

где В - цифровой сигнал включения, который равен «1» или «0» при включенном или выключенном устройстве соответственно;

АС (или NAC(Т3)) - прямой (или инверсный задержанный на время Тз) цифровой сигнал аварии сети, равный «0» (или «1») при номинальном уровне напряжении сети или «1» (или «0») при аварийном уровне напряжения сети;

Тз - длительность времени задержки сигнала АС элементом задержки;

& и # - операторы логических функций соответственно «И» и «ИЛИ» на языке ABEL;

q и k - число источников питания вычислителя и накопителя соответственно;

PBj (или PHj) - цифровой сигнал контроля уровня j-го источника питания вычислителя (или накопителя), равный «1» или «0» при уровне соответственно выше или ниже порогового при изменении j от единицы до q (или k) включительно.

Программа включения устройства начинается с подачи от питающей сети напряжения на шину сетевого напряжения и сигнала В=1 на первый вход первого элемента И. Если в питающей сети присутствует допустимое напряжение, на выходе датчика вырабатывается сигнал АС=0, проходящий через элементы задержки и НЕ, первый элемент И и элемент «Равнозначности» на вход первого ключевого элемента в виде сигнала X3=X1=NAC=1. Первый ключевой элемент открывается и сетевое напряжение подается на источник питания вычислителя, после установления номинальных уровней которого второй элемент И вырабатывает сигнал Х2=1, разрешающий прохождение сетевого напряжения на источник питания накопителя, после установления номинальных уровней которого по результирующему единичному сигналу X4=PH1&...&PHq исправности источников питания вычислителя и накопителя устройство [11] готово к функционированию. По фронту сигнала Х4=1 устройство [11] производит инициализацию и тестирование как своих составных частей, так и других устройств, связанных с устройством [11] через системную магистраль (ШУ, ША, ШД). После этого устройство [11] приступает к выполнению своих функций, например обработке информации и управления в процессе информационного взаимодействия со всеми другими устройствами с помощью системной магистрали.

Если в некоторый момент времени функционирования устройства при Х4=1 уровень напряжения сети становится ниже допустимого, то датчик вырабатывает сигнал АС=1, по фронту которого запускается программа выключения устройства при аварии сети. Эта программа выполняется так, что при Х4=1 по сигналу АС=1 вычислитель в течение времени, не превышающего Тз, осуществляет запись в накопитель всей необходимой информации текущей программы обработки информации и управления, выдает все необходимые аварийные команды на пульт оператора и другие устройства и останавливается. Далее через время Тз вырабатывается сигнал Х2=Х1=NCA(Тз)=0, второй ключевой элемент закрывается и отключает от источников питания накопителя напряжение сети. Затем при X1=PH1=...=PHq=0 элемент «Равнозначности» вырабатывает сигнал Х3=0, первый ключевой элемент закрывается и отключает от источников питания вычислителя напряжение сети.

Если в некоторый момент времени напряжение сети восстановится до номинального, то через время Тз первый элемент И выставит сигнал Х1=1 и далее повторится полностью описанная выше программа включения при В=1 и АС=0.

При АС=0, Х4=1 по переключению сигнала «В» из «1» в «0» выполняется программа выключения устройства по сигналу Х2=Х1=В=0, полностью аналогичная описанной ранее части программы выключения при аварии сети, выполняемой при X2=X1=NCA=0. При этом необходимо учесть, что для выключения системы с сохранением информации о текущем процессе функционирования системы без искажения информации в накопителе о выключении должно быть сообщено вычислителю заранее по исходному входному сигналу IB=0 выключения, по которому через время Тз (т.е. после выполнения вычислителем спасающей программы подготовки к выключению) при AC=0, Х4=1 сигнал «В» переключается из «1» в «0», и при остановленном вычислителе в устройстве [11] последовательно снимается напряжение сети с источников питания накопителя и вычислителя.

При построении устройства программного управления на основе устройства [11] основным его недостатком является программная и аппаратурная сложность, обусловленная организацией программ включения и выключения с помощью значительного числа сигналов: трех сигналов AC, X4 и IB прерывания вычислителя и множества сигналов AC, NAC, IB, В, X1, РВ1...PBq, PH1...PHk, X2, Х3 управления аппаратурой.

Из известных технических решений наиболее близким по технической сущности к предлагаемому относится устройство [9], содержащее блок программного управления, образованный автономной оперативной памятью на элементах технологии КМОП (содержит микросхему ОЗУ, два элемента И-НЕ, два резистора, вход питания, управляющие входы записи WR, стробирования CS и запрета NCR (сброса), кодовый вход адреса и кодовый вход/выход данных), вычислитель (назван остальной схемой и согласно описанному ранее современному уровню развития техники содержит, например, МК, кварцевый резонатор и два конденсатора для обеспечения функционирования внутреннего генератора синхроимпульсов МК [2, с.63, рис.2.6 а], входы и выходы управления, адреса и данных внутренней магистрали, входы и выходы ШУ, выходы ША и двунаправленную ШД системной магистрали, приемопередатчики и адаптер магистралей (например, на основе ПЛИС) для функционально ориентированного сопряжения МК с внутренней магистралью и системной магистралью, входы и выходы которой соединены с соответствующими входами и выходами блока программного управления), источник коммутируемого напряжения (образован двумя стабилитронами и конденсатором), вход источника основного напряжения питания, соединенный с первыми входами питания блока программного управления и источника коммутируемого напряжения, входы сигнала аварии источника питания NAIP и сброса RST, соединенные с входами прерывания и сброса блока программного управления соответственно, и вход источника резервного напряжения питания (этот вход на схеме отражен в виде гальванической батареи или аккумулятора), соединенный с вторым входом питания источника коммутируемого напряжения, выход которого соединен с вторым входом питания блока программного управления, соединенным с входами питания оперативной памяти и контроллера.

На устройство [9] поступают инверсный сигнал NAIP аварии источника питания и прямой сигнал RST сброса. Сигнал NAIP формируется блоком питания так, что NAIP=0 при выключенном блоке питания или при его аварии (например, при аварийном уровне напряжения сети или напряжения Еп, т.е. при 5,5В≤Еп≤4,5В), а при включенном блоке питания и установившемся напряжении 5,5В≥Еп≥4,5В сигнал NAIP=1. Сигнал RST =0 при NAIP=0, a при NAIP=1 сигнал RST=1 длительностью tRST≥10 мс формируется автоматически по каждому фронту сигнала NAIP=1 или вручную, например с помощью кнопки СБРОС пульта оператора.

Как сложный цифровой автомат с комбинированной памятью устройство может находиться в одном из трех состояний (выключенном, рабочем, «зависании») при питании МК вычислителя и автономной оперативной памяти напряжением Ек>2В, которое вырабатывает источник коммутируемого напряжения по напряжениям Ер и Еп согласно соотношениям

В выключенном состоянии на устройство [9] поступают сигналы NAIP=0, RST=0, вычислитель вырабатывает сигнал NCR=0 запрещения обращения к автономной оперативной памяти по сигналам WR и CS, оперативная память и МК находятся в режиме микропотребления.

При включении блока питания установление напряжений Еп≈5В, Ек≈Еп отмечается переключением на входе прерывания блока управления сигнала аварии NAIP из «0» в «1», а затем на вход сброса блока программного управления поступает сигнал сброса RST=1 длительностью tRST≥10 мс. По окончании RST (при Еп≈5В, Ек≈Еп) устройство программного управления переходит в рабочее состояние (NAIP=1, RST=0, NCR=1) и под его управлением инициализируются и тестируются все составные части М-системы, которая затем выполняет свои функции управления и обработки информации в реальном масштабе времени по прикладной программе, содержащейся, например, в РПЗУ МК вычислителя. В рабочем состоянии вычислитель функционирует с обращением к оперативной памяти при NCR=1 по импульсу CS=1 для чтения при WR=0 или записи при WR=1.

В процессе функционирования М-системы каждое изменение сигнала NAIP из «1» в «0», возникающее при выключении блока питания или кратковременном аварийном изменении уровня напряжения сети, запускает прерывающую подпрограмму. Эта подпрограмма выполняется при Ек≥4В так, что вычислитель сначала записывает для сохранения в оперативную память (ОЗУ МК + автономную оперативную память) соответствующую информацию, а затем переводит устройство программного управления в выключенное состояние: выставляет сигнал NCR=0 блокировки обращения к автономной оперативной памяти и переключает МК в режим микропотребления.

При NAIP=1 и RST=0 из рабочего состояния устройство программного управления может перейти в состояние «зависания», например, переходом МК вычислителя в режим микропотребления или холостого хода под воздействием внешних или внутренних помех. В состоянии «зависания» М-система прекращает выполнять свои функции с помощью обмена информации через системную магистраль между составными частями под управлением от устройства программного управления. Из состояния зависания в рабочее состояние устройство переводится выключением и включением блока питания в необслуживаемой или обслуживаемой М-системе, либо формированием сигнала RST нажатием кнопки СБРОС в обслуживаемой М-системе.

Основным недостатком устройства [9] является значительная напрасная потеря рабочего времени М-системы как из-за «зависания» прикладной программы (при соответствующих сбоях МК по внешним и/или внутренним помехам даже при наличии в МК аппаратно-программного сторожевого таймера) при отсутствии средств гарантированного автоматического перезапуска М-системы при «зависании», так и на тестирование (от десятков секунд до нескольких минут) при возникновении сигнала NAIP=0 аварии источника питания при каждом кратковременном (при длительности несколько сотен миллисекунд) аварийном изменении уровня напряжения сети (например, напряжения бортсети 27В), что обусловлено отработкой вычислителем каждого фронта сигнала NAIP=1 без учета предыстории уровня основного напряжения питания Еп при NAIP=0.

Предлагаемым изобретением принципиально решается задача сокращения напрасных потерь рабочего времени устройства (т.е. и М-системы) при каждом «зависании» его прикладной программы или кратковременном возникновении сигнала аварии источника питания за счет автоматического рационального перезапуска устройства (исключения тестирования М-системы при обнаружении кратковременной аварии источника основного напряжения питания) по импульсу сброса, который генерируется в результате аппаратного обнаружения любого из этих событий.

Для достижения этого технического результата в устройство программного управления, содержащее блок программного управления, управляющие входы и выходы, кодовый выход адреса и двунаправленную кодовую шину данных системной магистрали, являющиеся управляющими входами и выходами, кодовым выходом адреса и двунаправленной кодовой шиной данных блока программного управления соответственно, вход сброса, инверсный вход аварии основного источника питания, источник коммутируемого напряжения, шину основного источника питания, соединенную с первыми входами питания блока программного управления и источника коммутируемого напряжения, шину резервного источника питания, соединенную с вторым входом питания источника коммутируемого напряжения, выходная шина которого соединена с вторым входом питания блока программного управления, дополнительно содержит технологический управляющий вход, пороговый элемент со срабатыванием по запуску и отпусканием по уровню напряжения питания, прерыватель, снабженный выходом и тремя входами, и управляемый формирователь импульсов, снабженный двумя выходами, двумя управляющими входами, импульсным входом, входом запуска по фронту и входом запуска по нулевому уровню с задержкой, соединенному с инверсным входом сброса устройства, вход аварии основного источника питания которого соединен с первым управляющим входом формирователя импульсов, первым входом прерывателя и входом запуска порогового элемента, выход которого соединен с входом запуска по фронту формирователя импульсов, второй управляющий вход которого соединен с технологическим управляющим входом устройства, шина основного источника питания которого соединена с входами питания порогового элемента, формирователя импульсов и прерывателя, второй вход которого соединен с первым дополнительным управляющим выходом блока программного управления, второй дополнительный управляющий выход которого соединен с импульсным входом формирователя импульсов, первый выход которого соединен с входом сброса блока программного управления, вход прерывания которого соединен с выходом прерывателя, который содержит первый элемент НЕ и четыре элемента И-НЕ, первый вход первого из которых соединен с первым входом прерывателя и через первый элемент НЕ связан с первым входом второго элемента И-НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, выход которого соединен с первым входом четвертого элемента И-НЕ и выходом прерывателя, второй вход которого соединен с вторым входом первого элемента И-НЕ, выход которого соединен с вторым входом четвертого элемента И-НЕ, второй вход третьего элемента И-НЕ соединен с выходом четвертого элемента И-НЕ, третий вход которого соединен с вторым входом второго элемента И-НЕ и третьим входом прерывателя, который соединен с вторым выходом формирователя импульсов, который содержит пятый элемент И-НЕ, пять резисторов, первый конденсатор, второй элемент НЕ, третий элемент НЕ с открытым коллекторным выходом, первый и второй элементы И и управляемый генератор импульсов, снабженный выходом, управляющим входом, импульсным входом и входом запуска, который соединен с первым выводом первого конденсатора, первым входом первого элемента И и выходом пятого элемента И-НЕ, первый вход которого связан через второй элемент НЕ с первым выводом первого резистора, второй вывод которого соединен с вторым выводом первого конденсатора и первым выводом второго резистора, второй вывод которого соединен с входом запуска формирователя импульсов по нулевому уровню с задержкой и первым выводом третьего резистора, второй вывод которого соединен с входом запуска формирователя импульсов по фронту, вторыми входами пятого элемента И-НЕ и первого элемента И и первым выводом четвертого резистора, второй вывод которого соединен с выходом третьего элемента НЕ и первым выходом формирователя импульсов, второй выход которого является выходом первого элемента И, вход третьего элемента НЕ соединен с выходом генератора импульсов, управляющий вход которого соединен с выходом второго элемента И, первый вход которого является первым управляющим входом формирователя импульсов, второй управляющий вход которого соединен с вторым входом второго элемента И и связан через пятый резистор с шиной основного источника напряжения питания, импульсный вход формирователя импульсов является импульсным входом генератора импульсов, который содержит детектор огибающей импульсного сигнала, снабженный выходом, входом установки и импульсным входом, шестой элемент И-НЕ, третий элемент И, шестой и седьмой резисторы и второй конденсатор, первый вывод которого соединен с первым входом шестого элемента И-НЕ и выходами третьего элемента И и генератора, вход запуска которого является первым входом третьего элемент И, второй вход которого через шестой резистор связан с вторым выводом второго конденсатора и первым выводом седьмого резистора, второй вывод которого соединен с выходом детектора, вход установки которого соединен с выходом шестого элемента И-НЕ, второй вход которого является управляющим входом генератора, импульсным входом которого является импульсный вход детектора, причем все элементы прерывателя и формирователя импульсов, возможно за исключением третьего элемента НЕ, являются элементами технологии КМОП.

Автору неизвестны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение технологического управляющего входа, порогового элемента, прерывателя и управляемого формирователя импульсов) предлагаемого устройства программного управления, которые (по сравнению с прототипом [9]) позволяют принципиально сократить напрасные потери рабочего времени устройства программного управления (т.е. и М-системы) при каждом «зависании» его прикладной программы или кратковременном возникновении сигнала аварии источника основного напряжения питания за счет перезапуска устройства с помощью формирования импульса сброса как результата аппаратного обнаружения любого из этих событий и исключения тестирования М-системы при идентификации события как кратковременной аварии основного источника напряжения питания.

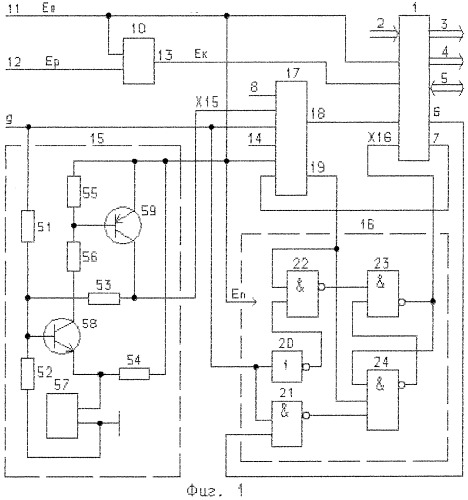

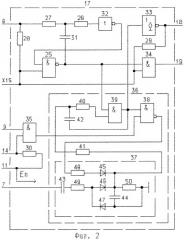

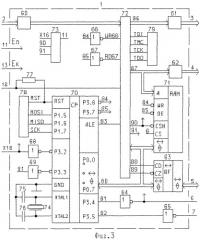

На фиг.1 приведена функциональная схема устройства программного управления в целом с функциональными схемами прерывателя и возможной реализацией порогового элемента, а на фиг.2 и 3 приведены функциональные схемы управляемого формирователя импульсов и блока программного управления соответственно при реализации устройства, в частности с байтовой ШД и 13-разрядной ША с использованием интегральных микросхем (ИС) как импортных (ИС AT89S8252, созданной фирмой «Atmel» по усовершенствованной КМОП технологии, и ПЛИС, например EPM7128ST100-10 фирмы «Altera» в качестве адаптера магистралей), так и отечественных технологии КМОП, например 537РУ17 (или 16) в качестве автономной оперативной памяти и серии 1554 (или 1564) для построения остальных составных частей устройства с учетом того, что ИС 1554 функционируют в диапазоне температур от -45°С до +85°С при напряжении питания от +2 до +6В при постоянном токе по каждому выходу до 24 мА и входном токе по каждому входу от -1 до +1мкА [12, с.15, с.21 табл.3.1]. Кроме того [12, с.16], ИС серии 1554 способны работать с выходным током не менее 75 мА и выходным напряжением не менее 3,85В при Еп=5,5В с сопротивлением нагрузки Zo=50 ОМ.

Устройство программного управления в целом содержит (фиг.1) блок 1 программного управления, управляющие входы 2 и выходы 3, кодовый выход 4 адреса и двунаправленную кодовую шину 5 данных системной магистрали, являющиеся соответственно управляющими входами и выходами, кодовым выходом адреса и двунаправленной кодовой шиной данных блока 1, первый 6 и второй 7 дополнительные управляющие выходы блока 1, инверсный вход 8 сброса, инверсный вход 9 аварии основного источника питания, источник 10 коммутируемого напряжения питания, шину 11 источника основного напряжения питания, соединенную с первыми входами питания блока 1 и источника 10 коммутируемого напряжения, шину 12 источника резервного напряжения питания, соединенную с вторым входом питания источника 10 коммутируемого напряжения, выходная шина 13 которого соединена с вторым входом питания блока 1, технологический управляющий вход 14, пороговый элемент 15 со срабатыванием по запуску и отпусканием по уровню напряжения питания, прерыватель 16, снабженный выходом и тремя входами, и управляемый формирователь 17 импульсов, снабженный первым 18 и вторым 19 выходами, двумя управляющими входами, импульсным входом, входом запуска по фронту и входом запуска по нулевому уровню с задержкой, соединенному с входом 8 сброса устройства, вход 9 аварии основного источника питания которого соединен с первым управляющим входом формирователя 17, первым входом прерывателя 16 и входом запуска порогового элемента 15, выход которого соединен с входом запуска по фронту формирователя 17, второй управляющий вход которого соединен с технологическим управляющим входом 14 устройства, шина 11 источника основного напряжения питания которого соединена с входами питания порогового элемента 15, формирователя 17 и прерывателя 16, второй вход которого соединен с первым дополнительным управляющим выходом 6 блока 1, второй дополнительный управляющий выход 7 которого соединен с импульсным входом формирователя 17, первый выход 18 которого соединен с входом сброса блока 1, вход прерывания которого соединен с выходом прерывателя 16, который содержит первый элемент 20 НЕ и четыре элемента 21-24 И-НЕ, первый вход первого 21 из которых соединен с первым входом прерывателя 16 и через первый элемент 20 НЕ связан с первым входом второго элемента 22 И-НЕ, выход которого соединен с первым входом третьего элемента 23 И-НЕ, выход которого соединен с первым входом четвертого элемента 24 И-НЕ и выходом прерывателя 16, второй вход которого соединен с вторым входом первого элемента 21 И-НЕ, выход которого соединен с вторым входом четвертого элемента 24 И-НЕ, второй вход третьего элемента 23 И-НЕ соединен с выходом четвертого элемента 24 И-НЕ, третий вход которого соединен с вторым входом второго элемента 22 И-НЕ и третьим входом прерывателя 16, соединенным с вторым выходом 19 формирователя 17.

Управляемый формирователь 17 импульсов содержит (фиг.2) пятый элемент 25 И-НЕ, пять резисторов 26-30, первый конденсатор 31, второй элемент 32 НЕ, третий элемент 33 НЕ с открытым коллекторным выходом, первый 34 и второй 35 элементы И, и управляемый генератор 36 импульсов, снабженный выходом, управляющим входом, импульсным входом и входом запуска, который соединен с первым выводом первого конденсатора 31, первым входом первого элемента 34 И и выходом пятого элемента 25 И-НЕ, первый вход которого связан через второй элемент 32 НЕ с первым выводом первого резистора 26, второй вывод которого соединен с вторым выводом первого конденсатора 31 и первым выводом второго резистора 27, второй вывод которого соединен с входом 8 запуска формирователя 17 по нулевому уровню с задержкой и первым выводом третьего резистора 28, второй вывод которого соединен с входом запуска формирователя 17 по фр