Способ синхронизации сигналов и устройство для его осуществления

Иллюстрации

Показать всеИзобретение относится к радиотехнике, в частности к способу и устройству синхронизации, и может быть использовано в приемниках локальных беспроводных сетей на базе стандарта 802.11 и системах широкополосного доступа к Интернету на базе стандарта 802.16, а также в других беспроводных телекомуникационных системах, использующих OFDM сигналы. Технический результат заключается в повышении точности ценки частоты при низких отношениях сигнал/шум и частотно-селективном фединге. Этот результат достигается за счет уменьшения аномальных ошибок, которые обнаруживают и исключают при формировании оценки сдвига частоты, повышают точность оценки частоты при низких отношениях сигнал/шум и частотно-селективном фединге. 2 н. и 4 з.п. ф-лы, 9 ил.

Реферат

Изобретение относится к радиотехнике, в частности к способам и устройствам синхронизации сигналов, и может быть использовано в приемниках локальных беспроводных сетей на базе стандарта 802.11 и системах широкополосного доступа к Интернету на базе стандарта 802.16, а также в других беспроводных телекомуникационных системах, использующих OFDM сигналы.

Для синхронизации принимаемых OFDM (Orthogonal Frequency Division Multiplexing) сигналов с опорными сигналами приемника необходимо оценить их временную задержку и частотный сдвиг.

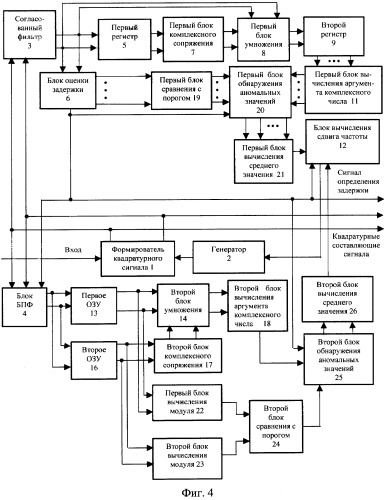

В OFDM системах для частотно-временной синхронизации обычно используют преамбулу фрейма (последовательность пилот сигналов, которая предшествует информационному сообщению). Примером такой преамбулы может служить преамбула по стандарту 802. 11 [Supplement to IEEE Standard for Information technology. Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) specifications: High-speed Physical Layer in the 5 GHZ Band, Figure 110] структура, которой приведена на фиг.1.

Преамбула состоит из десяти коротких и двух длинных OFDM пилот сигналов.

Короткие OFDM пилот сигналы состоят из 12 поднесущих, которые модулированы элементами S последовательности:

S-26,26=√(13/6){0,0,1+j,0,0,0,-1-j,0,0,0,1+j,0,0,0,-1-j,0,0,0,-1-j,0,0,0,1+j,0,0,0,0,0,0,0,-1-j,0,0,0,-1-j,0,0,0,1+j,0,0,0,1+j,0,0,0,1+j,0,0,0,1+j,0,0}

Длинные OFDM пилот сигналов состоят из 52 поднесущих, которые модулированы элементами L последовательности:

L-26,26={1,1,-1,-1,1,1,-1,1,-1,1,1,1,1,1,1,-1,-1,1,1,-1,1,-1,1,1,1,1,0,1,-1,-1,1,1,-1,1,-1,1,-1,-1,-1,-1,-1,1,1,-1,-1,1,-1,1,-1,1,1,1,1}

Аналогичную структуру имеет преамбула в стандарте 802.16 [Amendment to IEE Standard for Local and Metropolitan Area Networks. Part 16: Air Interface for Fixed Broadband Wireless Access Systems].

Известны различные способы и устройства синхронизации приема сигналов, например способ и устройство, описанные в патенте США №5.812.523 [US №5. 812.523 «Method and device for synchronization at OFDM-system», Int. Cl. H 04 J 11/00]. В этом способе и устройстве временную и частотную синхронизацию выполняют по пилот сигналу, состоящему из двух повторяющихся частей. Для оценки временной задержки и частотного сдвига сигнала вычисляют комплексное произведение значений комплексно-сопряженного принимаемого сигнала и принимаемого сигнала, задержанного на половину пилот сигнала. Затем в скользящем окне, длительностью равном половине пилот сигнала, вычисляют среднее значение полученных произведений. По временному положению максимального значения модуля и фазе комплексного значения произведения, соответствующего этому максимальному модулю, оценивают временную задержку и частотный сдвиг соответственно.

Устройство, реализующее предложенный способ, представляет собой последовательно включенные узлы, выполняющие перечисленные выше операции: комплексное сопряжение принимаемого сигнала, задержку сигнала, комплексное произведение, вычисление скользящего среднего, вычисление модуля и фазы скользящего среднего.

Недостатком этого технического решения является то, что при разности фаз между двумя частями пилот сигнала, вызванной частотным сдвигом между принимаемым и опорным сигналом, большей π, рассматриваемые способ и устройство малоэффективны.

Поэтому, как правило, оценку сдвига частоты сигнала выполняют в два этапа. На первом этапе определяют начальную оценку сдвига частоты, а затем на втором определяют уточненную оценку сдвига частоты. Пример такой системы и способа описан в патенте США №6.459.679 B1 [US №6.459.679«Method and apparatus for synchronizing orthogonal frequency division multiplexing (OFDM) receiver». Int. Cl.7 H 04 J 11/00]. В этом патенте приведены система и способ, в которых временную и частотную синхронизацию выполняют по одному пилот сигналу, передаваемому в начале фрейма. Пилот сигнал во временной области состоит из двух частей, причем вторая часть сигнала повторяет первую. Для оценки временной задержки и частотного сдвига сигнала вычисляют временную метрику, значения которой равны скользящей сумме произведений между значениями комплексно-сопряженного принимаемого сигнала и принимаемым сигналом, задержанным на половину пилот сигнала. Сумма произведений вычисляется на интервале, равном половине длительности пилот сигнала. По временному положению максимального значения модуля временной метрики и фазе, соответствующей этому максимальному модулю временной метрики, оценивают временную задержку и частотный сдвиг соответственно. Если разность фаз между двумя частями пилот сигнала больше π, то частотный сдвиг определяют по разности фаз между двумя частями пилот сигнала и максимуму корреляционной функции спектра пилот сигнала и опорного спектра, которые являются псевдослучайными последовательностями.

Устройство синхронизации реализовано на сигнальном процессоре.

Недостатком этого технического решения является то, что и начальная и уточненная оценки сдвига частоты определяются по одному пилот сигналу, что при низких отношениях сигнал/шум и частотно-селективных замираниях приводит к ухудшению характеристик оценки параметров сигналов.

Наиболее близким техническим решением к заявляемому изобретению является способ, приведенный в статье [Paul H. Moose A Technique for Orthogonal Frequency Division Multiplexing Frequency Offset Correction. IEEE TRANSACTIONS ON COMMUNICATIONS, VOL. 42, NO. 10, OCTOBER 1994].

Известный способ, в котором частотную синхронизацию выполняют по К коротким и двум длинным пилот сигналам, можно представить в виде последовательности следующих операций:

Выполняют оценку временной задержки принимаемых коротких пилот сигналов.

Одновременно с оценкой временной задержки коротких пилот сигналов вычисляют комплексную величину корреляции принимаемого короткого пилот сигнала.

Выполняют умножение комплексной величины корреляции принимаемого короткого пилот сигнала на сопряженную величину корреляции принимаемого короткого пилот сигнала, задержанную на длительность одного короткого пилот сигнала.

Выполняют суммирование полученных (К-1) произведений, где К - число коротких пилот сигналов, определенных подряд с интервалом, равным длительности одного короткого пилот сигнала.

Вычисляют аргумент полученной комплексной суммы произведений величин корреляции принимаемого короткого пилот сигнала.

По вычисленному аргументу вычисляют начальную оценку сдвига частоты после выполнения оценки временной задержки.

Выполняют начальную частотную коррекцию принимаемого сигнала, используя вычисленную начальную оценку сдвига частоты.

Выполняют БПФ (быстрое преобразование Фурье) принятых первого и второго длинных пилот сигналов.

Выполняют умножение спектральных составляющих первого длинного пилот сигнала на комплексно-сопряженные спектральные составляющие с равными частотами спектров второго длинного пилот сигнала.

Выполняют суммирование полученных произведений.

Вычисляют аргумент полученной комплексной суммы произведений спектральных составляющих первого длинного пилот сигнала на комплексно-сопряженные спектральные составляющие с равными частотами спектров второго длинного пилот сигнала.

По вычисленному аргументу вычисляют уточненную оценку сдвига частоты.

Выполняют уточненную частотную коррекцию принимаемого сигнала, используя вычисленную уточненную оценку сдвига частоты.

При этом сдвиг частоты определяют по формуле Fof=Δϕ/2πTs, где Fof - сдвиг частоты, Δϕ - разность фаз, Ts - длительность пилот сигнала. Эта формула применима как для определения начальной, так и для определения уточненной оценки сдвига частоты. В первом случае Δϕ равна аргументу комплексной суммы произведений величин корреляции принимаемого короткого пилот сигнала, а Ts - длительность короткого пилот сигнала, во втором случае Δϕ равна аргументу комплексной суммы произведений спектральных составляющих первого длинного пилот сигнала на комплексно-сопряженные спектральные составляющие с равными частотами спектров второго длинного пилот сигнала, a Ts - длительности длинного пилот сигнала.

В описании прототипа не приведено устройство, однако по описанию алгоритма можно представить устройство, которое реализует описанный способ-прототип. Структурная схема такого устройства показана на фиг.2.

Устройство фиг.2 содержит формирователь квадратурного сигнала 1, генератор 2, согласованный фильтр 3, блок быстрого преобразования Фурье 4 (БПФ), первый регистр 5, блок оценки задержки 6, первый блок комплексного сопряжения 7, первый блок умножения 8, второй регистр 9, блок суммирования 10, первый блок вычисления аргумента комплексного числа 11, блок вычисления сдвига частоты 12, первое 13 и второе 16 оперативные запоминающие устройства, второй блок умножения 14, накопитель 15, второй блок комплексного сопряжения 17 и второй блок вычисления аргумента комплексного числа 18, при этом первый вход формирователя квадратурного сигнала 1 является входом устройства, второй вход формирователя квадратурного сигнала соединен с выходом генератора 2, первый и второй выходы, являющиеся соответственно синфазной и квадратурной составляющими входного сигнала, соединены соответственно с первыми и вторыми входами согласованного фильтра 3 и блока быстрого преобразования Фурье 4 и являются соответственно первым синфазным и вторым квадратурным выходами устройства, первый и второй выходы согласованного фильтра 3 соединены соответственно с первыми и вторыми входами первого регистра 5, блока оценки задержки 6 и первого блока умножения 8, первый и второй выходы первого регистра 5 соединены соответственно с первым и вторым входами первого блока комплексного сопряжения 7, первый и второй выходы которого соединены соответственно с третьим и четвертым входами первого блока умножения 8, первый и второй выходы которого соединены соответственно с первым и вторыми входами второго регистра 9, (К-1) выходов которого соединены с соответствующими им входами блока суммирования 10, первый и второй выходы которого соединены с первым и вторым входами первого блока вычисления аргумента комплексного числа 11, выход которого соединен с первым входом блока вычисления сдвига частоты 12, выход которого соединен со входом генератора 2, второй вход блока вычисления сдвига частоты 12 объединен с третьим входом блока быстрого преобразования Фурье 4 и соединен с выходом блока оценки задержки 6, выход которого является третьим выходом устройства, первый и второй выходы блока быстрого преобразования Фурье 4 соединен соответственно с первыми и вторыми входами первого 13 и второго 16 оперативных запоминающих устройств, первый и второй выходы первого запоминающего устройства 13 соединены соответственно с первым и вторым входами второго блока умножения 14, первый и второй выходы второго запоминающего устройства 16 соединены соответственно с первым и вторым входами второго блока комплексного сопряжения 17, первый и второй выходы которого соединены соответственно с третьим и четвертым входами второго блока умножения 14, первый и второй выходы которого соединены соответственно с первым и вторым входами накопителя 15, первый и второй выходы которого соединены соответственно с первым и вторым входами второго блока вычисления аргумента комплексного числа 18, выход которого соединен с третьим входом блока вычисления сдвига частоты 12.

Способ-прототип осуществляют следующим образом (см.фиг.2).

Входной сигнал поступает на первый вход формирователя квадратурного сигнала 1, который преобразует входной сигнал в две квадратурные составляющие: синфазную и квадратурную.

Квадратурные составляющие входного сигнала поступают соответственно на первый и второй выходы устройства и на первый и второй входы согласованного с коротким пилот сигналом фильтра 3 и блока БПФ 4. Выходными сигналами согласованного фильтра является комплексная величина корреляции принимаемого короткого пилот сигнала.

Выходные сигналы согласованного фильтра 3 с первого и второго выходов поступают соответственно на первый и второй входы блока оценки задержки 6. С выхода блока оценки задержки 6 сигнал определения задержки, который определяет момент окончания К коротких пилот сигналов, поступает на третий вход блока БПФ 4, второй вход блока вычисления сдвига частоты 12 и на третий выход устройства.

Выходные сигналы согласованного фильтра 3 с первого и второго выходов поступают соответственно на первый и второй входы первого регистра 5, задерживающего их на длительность короткого пилот сигнала. Первый блок комплексного сопряжения 7 выполняет комплексное сопряжение выходных сигналов первого регистра 5.

Очевидно, что блок комплексного сопряжения 7 можно реализовать в виде логической схемы, меняющей знак мнимой части значения входного сигнала на противоположный.

Выходные сигналы первого блока комплексного сопряжения 7 с первого и второго выходов поступают соответственно на третий и четвертый входы первого блока умножения 8. На первый и второй входы этого блока 8 поступают выходные сигналы согласованного фильтра 3.

Таким образом, в момент окончания короткого пилот сигнала, когда модуль сигнала на выходе согласованного фильтра 3 принимает максимальное значение, на первый и второй выходы первого блока умножения 8 поступает комплексный сигнал, аргумент которого равен разности фаз двух коротких пилот сигналов.

Выходной комплексный сигнал с первого и второго выходов первого блока умножения 8 поступает соответственно на первый и второй входы второго сдвигового регистра 9, осуществляющего его задержку на К длительностей короткого пилот сигнала. Отводы второго регистра 9 выполнены с интервалом, равным длительности одного короткого пилот сигнала. С (К-1) отводов сигналы поступают на соответствующие им входы блока суммирования 10.

В блоке 10 выполняют суммирование действительных и мнимых частей (К-1) комплексных чисел таким образом, что в момент окончания К-го короткого пилот сигнала на выходы блока суммирования 10 поступает комплексное значение суммы произведений величин корреляции принимаемого короткого пилот сигнала с аргументом, равным оценке разности фаз коротких пилот сигналов.

Сигналы с первого и второго выходов блока суммирования 10 поступают соответственно на первый и второй входы первого блока вычисления аргумента комплексного числа 11, который вычисляет аргумент комплексного числа, поступившего на его вход.

Следовательно, после окончания К-го пилот сигнала с выхода первого блока вычисления аргумента комплексного числа 11 на первый вход блока вычисления сдвига частоты 12 поступает оценка разности фаз коротких пилот сигналов. Блок вычисления сдвига частоты 12 по оценке разности фаз коротких пилот сигналов вычисляет начальную оценку сдвига частоты. Затем начальная оценка сдвига частоты с выхода блока 12 поступает на вход генератора 2, который по этой оценке выполняет начальную частотную коррекцию принимаемого сигнала.

Блок БПФ 4 вычисляет спектры длинных пилот сигналов, которые задержаны по времени относительно коротких пилот сигналов на заранее известную величину, как правило, равную длительности защитного интервала.

Полученные спектры записываются соответственно в первое 13 (ОЗУ) и второе 16 (ОЗУ) оперативные запоминающие устройства. Затем эти спектры одновременно считываются из первого 13 ОЗУ и второго 16 ОЗУ. Из первого 13 ОЗУ комплексные значения спектра первого длинного пилот сигнала поступают соответственно на первый и второй входы второго 14 блока умножения. Из второго 16 ОЗУ через второй блок комплексного сопряжения 17 на третий и четвертый входы блока 14 поступают комплексные значения спектра второго длинного пилот символа.

Таким образом, на выходах второго блока умножения 14 формируется комплексный сигнал, аргумент которого равен разности фаз двух спектральных составляющих с равными частотами первого и второго длинных пилот символов. Комплексные значения выходного сигнала второго блока умножения 14 с первого и второго выходов поступают соответственно на первый и второй входы накопителя 15. Результат накопления с первого и второго выходов блока 15 поступает соответственно на первый и второй входы второго блока вычисления аргумента комплексного числа 18, который вычисляет аргумент комплексного числа, поступившего на его входы.

Следовательно, с выхода второго блока вычисления аргумента комплексного числа 18 на третий вход блока вычисления сдвига частоты 12 поступает оценка разности фаз спектральных составляющих первого и второго длинных пилот символов. Блок вычисления сдвига частоты 12 по оценке разности фаз спектральных составляющих первого и второго длинных пилот символов вычисляет уточненную оценку сдвига частоты. Затем уточненная оценка сдвига частоты с выхода блока 12 поступает на вход генератора 2, который по этой оценке выполняет уточненную частотную коррекцию принимаемого сигнала.

В OFDM системах частотная синхронизация должна быть выполнена с высокой точностью. В противном случае возникают большие потери, которые вызваны взаимными помехами между поднесущими и уменьшением амплитуды сигнала на выходах согласованных фильтров каждой поднесущей [Richard van Nee, Ramjee Prasad, OFDM Wireless Multimedia Communications, Artech House, Boston-London, 2000].

При оценке параметров сигналов в шумах могут возникать аномальные ошибки [Радиотехнические системы, под ред. Ю.М.Казаринова, М.; "Высшая школа", 1990]. Частота и величина этих ошибок увеличивается при уменьшении отношения сигнал/шум и при частотно-селективном фединге.

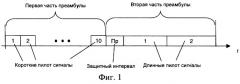

На фиг.3 приведены гистограммы начальных оценок частоты с аномальными ошибками, полученные при моделировании способа прототипа. Синхронизация выполнялась по сигналу стандарта 802.11 в каналах с частотно-селективными замираниями.

Таким образом, недостатком способа и устройства-прототипа является ухудшение оценки сдвига частоты при низких отношениях сигнал/шум и частотно-селективных замираниях, вызванное аномальными ошибками.

Задача, которую решает предлагаемое изобретение, заключается в повышении точности оценки частоты при низких отношениях сигнал/шум и частотно-селективном фединге, что достигается за счет уменьшения аномальных ошибок.

Поставленная задача решается тем, что в способ синхронизации сигнала, при котором для синхронизации сигнала используют предшествующую информационному сигналу преамбулу, состоящую из К коротких и двух длинных пилот сигналов, заключающийся в том, что выполняют оценку временной задержки принимаемых коротких пилот сигналов, одновременно с оценкой временной задержки коротких пилот сигналов вычисляют комплексную величину корреляции принимаемого короткого пилот сигнала, умножают комплексную величину корреляции принимаемого короткого пилот сигнала на комплексно сопряженную величину корреляции принимаемого короткого пилот сигнала, задержанную на длительность одного короткого пилот сигнала, вычисляют аргумент полученного значения, вычисляют начальную оценку сдвига частоты, выполняют начальную частотную коррекцию принимаемого сигнала, используя вычисленную начальную оценку сдвига частоты, выполняют быстрое преобразование Фурье принятых первого и второго длинных пилот сигналов, выполняют умножение спектральных составляющих первого длинного пилот сигнала на комплексно-сопряженные спектральные составляющие с равными частотами спектров второго длинного пилот сигнала, вычисляют аргументы полученных комплексных произведений, вычисляют уточненную оценку сдвига частоты, выполняют уточненную частотную коррекцию принимаемого сигнала, используя вычисленную уточненную оценку сдвига частоты,

согласно изобретению вводят следующую последовательность операций:

вычисляют и запоминают К модулей комплексных величин корреляции, определенных подряд с интервалом, равным длительности одного короткого пилот сигнала, где К - число коротких пилот сигналов,

умножение комплексной величины корреляции выполняют одновременно с вычислением модулей,

вычисляют аргументы (К-1) полученных произведений принимаемого сигнала и короткого пилот сигнала на комплексно-сопряженную величину корреляции принимаемого короткого пилот сигнала, определенных подряд с интервалом, равным длительности одного короткого пилот сигнала, вычисленные аргументы представляют собой разности фаз К комплексных величин корреляции,

выполняют обнаружение аномальных значений вычисленных разностей фаз (К-1) комплексных величин корреляции, модули которых превысили первый заданный порог, после выполнения оценки временной задержки,

вычисляют среднее значение оставшихся неаномальных значений разностей фаз комплексных величин корреляции,

начальную оценку сдвига частоты вычисляют по среднему значению разности фаз комплексных величин корреляции,

вычисляют модули спектральных составляющих спектров первого и второго длинных пилот сигналов,

умножение спектральных составляющих выполняют одновременно с вычислением модулей,

вычисляют аргументы полученных комплексных произведений, являющихся разностями фаз спектральных составляющих с равными частотами спектров первого и второго длинных пилот сигналов,

сравнивают модули спектральных составляющих первого и второго длинных пилот сигналов с заданным вторым порогом,

выполняют обнаружение аномальных значений вычисленных разностей фаз спектральных составляющих, модули которых превысили второй заданный порог,

вычисляют среднее значение оставшихся не аномальных значений разностей фаз спектральных составляющих,

уточненную оценку сдвига частоты вычисляют по полученному среднему значению.

При этом оценку временной задержки принимаемых коротких пилот сигналов выполняют, например, путем вычисления величины корреляции принимаемого короткого пилот сигнала, вычисления суммы К определенных подряд с интервалом, равным длительности одного короткого пилот сигнала значений модулей полученных величин взаимной корреляции, и сравнения каждой полученной суммы с заданным порогом, при этом, если порог превышен, то считают, что временная задержка полученной суммы определяет временную задержку коротких пилот сигналов.

Обнаружение аномальных значений вычисленных разностей фаз комплексных величин корреляции выполняют, например, путем вычисления среднего значения разностей фаз комплексных величин корреляции, формирования первого порога путем сложения полученного среднего значения разности фаз комплексных величин корреляции с первым заданным значением фазы, формирования второго порога путем вычитания из полученного среднего значения разности фаз комплексных величин корреляции второго заданного значением фазы и сравнения каждой полученной разности фаз комплексных величин корреляции с двумя порогами, при этом, если разность фаз больше первого порога или меньше второго порога, то принимают решение об обнаружении аномального значения разности фаз комплексных величин корреляции.

Обнаружение аномальных значений вычисленных разностей фаз спектральных составляющих выполняют, например, путем вычисления среднего значения разностей фаз спектральных составляющих, формирования первого порога путем сложения полученного среднего значения разностей фаз спектральных составляющих с первым заданным значением фазы, формирования второго порога путем вычитания из полученного среднего значения разности фаз спектральных составляющих второго заданного значением фазы сравнения каждой полученной разности фаз спектральных составляющих с двумя порогами, при этом, если разность фаз больше первого порога или меньше второго порога, то принимают решение об обнаружении аномального значения разности фаз спектральных составляющих.

Сдвиг частоты определяют по формуле: Fof=Δϕ/2πTs, где Fof - сдвига частоты, Δϕ - разность фаз, Ts - длительность пилот сигнала. Эта формула применима как для определения начальной, так и для определения уточненной оценки сдвига частоты. В первом случае Δϕ равно аргументу комплексной суммы произведений величин корреляции принимаемого короткого пилот сигнала на комплексно-сопряженную величину корреляции принимаемого короткого пилот сигнала, задержанную на длительность одного короткого пилот сигнала, Ts - длительность короткого пилот сигнала, во втором случае Δϕ равно аргументу комплексной суммы произведений спектральных составляющих первого длинного пилот сигнала на комплексно-сопряженные спектральные составляющие с равными частотами спектров второго длинного пилот сигнала, Ts - длительность длинного пилот сигнала.

Поставленная задача решается также тем, что в устройство синхронизации сигнала, содержащее формирователь квадратурного сигнала, генератор, согласованный фильтр, блок быстрого преобразования Фурье, первый регистр, блок оценки задержки, первый блок комплексного сопряжения, первый блок умножения, второй регистр, первый блок вычисления аргумента комплексного числа, блок вычисления сдвига частоты, первое и второе оперативные запоминающие устройства, второй блок умножения, второй блок комплексного сопряжения и второй блок вычисления аргумента комплексного числа, при этом первый вход формирователя квадратурного сигнала является входом устройства, второй вход формирователя квадратурного сигнала соединен с выходом генератора, первый и второй выходы формирователя квадратурного сигнала, являющиеся соответственно синфазной и квадратурной составляющими входного сигнала, соединены соответственно с первыми и вторыми входами согласованного фильтра и блока быстрого преобразования Фурье и являются соответственно первым синфазным и вторым квадратурным выходами устройства, первый и второй выходы согласованного фильтра соединены соответственно с первыми и вторыми входами первого регистра, блока оценки задержки и первого блока умножения, первый и второй выходы первого регистра соединены соответственно с первым и вторым входами блока комплексного сопряжения, первый и второй выходы которого соединены соответственно с третьим и четвертым входами первого блока умножения, первый и второй выходы которого соединены соответственно с первым и вторыми входами второго регистра, (К-1) выходов которого соединены с соответствующими им (К-1) входами первого блока вычисления аргумента комплексного числа, выход блока вычисления сдвига частоты соединен со входом генератора, первый вход блока вычисления сдвига частоты и третий вход блока быстрого преобразования Фурье объединены и соединены с выходом блока оценки задержки, выход которого является третьим выходом устройства, первый и второй выходы блока быстрого преобразования Фурье соединены соответственно с первыми и вторыми входами первого и второго оперативных запоминающих устройств, первый и второй выходы первого запоминающего устройства соединены соответственно с первым и вторым входами второго блока умножения, первый и второй выходы второго запоминающего устройства соединены соответственно с первым и вторым входами второго блока комплексного сопряжения, первый и второй выходы которого соединены соответственно с третьим и четвертым входами второго блока умножения.

Согласно изобретению введены:

первый блок сравнения с порогом,

первый блок обнаружения аномальных значений,

первый блок вычисления среднего значения, формирующий на выходе средние значения оставшихся не аномальных значений разностей фаз комплексных величин корреляции,

первый и второй блоки вычисления модуля,

второй блок сравнения с порогом,

второй блок обнаружения аномальных значений,

второй блок вычисления среднего значения, формирующий на выходе средние значения оставшихся неаномальных значений разностей фаз спектральных составляющих.

При этом (К-1) дополнительных выходов блока оценки задержки соединены с соответствующими им (К-1) входами первого блока сравнения с порогом, (К-1) выходов которого соединены с соответствующими им (К-1) первыми входами первого блока обнаружения аномальных значений, (К-1) вторые входы которого соединены с соответствующими им (К-1) выходами первого блока вычисления аргумента комплексного числа, третий вход первого блока обнаружения аномальных значений и первый вход второго блока обнаружения аномальных значений объединены и соединены с выходом блока оценки задержки, первый выход первого блока обнаружения аномальных значений соединен с первым входом первого блока вычисления среднего значения, вторые (К-1) входов которого соединены с соответствующими им (К-1) вторыми выходами первого блока обнаружения аномальных значений, выход первого блока вычисления среднего значения соединен со вторым входом блока вычисления сдвига частоты, первый и второй выходы второго блока умножения соединены соответственно с первым и вторым входами второго блока вычисления аргумента комплексного числа, выход которого соединен со вторым входом второго блока обнаружения аномальных значений, третий вход второго блока обнаружения аномальных значений соединен с выходом второго блока сравнения с порогом, первый и второй входы которого соединены соответственно с выходами первого и второго блоков вычисления модулей, первый и второй входы первого блока вычисления модуля соединены соответственно с первым и вторым выходами первого запоминающего устройства, первый и второй входы второго блока вычисления модуля соединены соответственно с первым и вторым выходами второго запоминающего устройства, первый и второй выходы второго блока обнаружения аномальных значений соединены соответственно с первым и вторым входами второго блока вычисления среднего значения, выход которого соединен с третьим входом блока вычисления сдвига частоты.

Заявляемая совокупность отличительных признаков изобретений, способа синхронизации сигнала и устройства для его осуществления, созданных в едином изобретательском замысле, позволяет получить новый технический эффект - повысить точность оценки частоты при низких отношениях сигнал/шум и частотно-селективном фединге, что достигается за счет уменьшения аномальных ошибок, которые обнаруживают и исключают при формировании оценки сдвига частоты.

Далее описание изобретений поясняется примерами выполнения и чертежами.

На фиг.1 показана структура преамбулы по стандарту 802.11.

На фиг.2 выполнена структурная схема устройства-прототипа.

На фиг.3 приведены гистограммы начальных оценок частоты с аномальными ошибками, полученные при моделировании способа-прототипа.

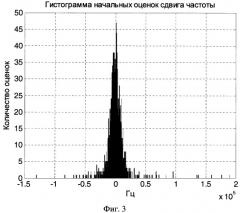

На фиг.4 выполнена структурная схема заявляемого устройства.

На фиг.5 - структурная схема блока оценки задержки 6 для заявляемого устройства, приведена как пример реализации.

На фиг.6 - структурная схема блока вычисления аргумента комплексного числа (первого 11 или второго 18), приведена как пример реализации.

На фиг.7 - структурная схема первого блока обнаружения аномальных значений 20 для заявляемого устройства, приведена как пример реализации.

На фиг.8 - структурная схема второго блока обнаружения аномальных значений 25 для заявляемого устройства, приведена как пример реализации.

На фиг.9 структурная схема блока вычисления сдвига частоты 12 для заявляемого устройства, приведена как пример реализации.

Заявляемое устройство синхронизации сигнала (фиг.4) содержит формирователь квадратурного сигнала 1, генератор 2, согласованный фильтр 3, блок быстрого преобразования Фурье 4, первый регистр 5, блок оценки задержки 6, первый блок комплексного сопряжения 7, первый блок умножения 8, второй регистр 9, первый блок вычисления аргумента комплексного числа 11, блок вычисления сдвига частоты 12, первое 13 и второе 16 оперативные запоминающие устройства, второй блок умножения 14, второй блок комплексного сопряжения 17 и второй блок вычисления аргумента комплексного числа 18, при этом первый вход формирователя квадратурного сигнала 1 является входом устройства, второй вход формирователя квадратурного сигнала 1 соединен с выходом генератора 2, первый и второй выходы формирователя квадратурного сигнала 1, являющиеся соответственно синфазной и квадратурной составляющими входного сигнала, соединены соответственно с первыми и вторыми входами согласованного фильтра 3 и блока быстрого преобразования Фурье 4 и являются соответственно первым синфазным и вторым квадратурным выходами устройства, первый и второй выходы согласованного фильтра 3 соединены соответственно с первыми и вторыми входами первого регистра 5, блока оценки задержки 6 и первого блока умножения 8, первый и второй выходы первого регистра 5 соединены соответственно с первым и вторым входами блока комплексного сопряжения 7, первый и второй выходы которого соединены соответственно с третьим и четвертым входами первого блока умножения 8, первый и второй выходы которого соединены соответственно с первым и вторыми входами второго регистра 9, (К-1) выходов которого соединены с соответствующими им (К-1) входами первого блока вычисления аргумента комплексного числа 11, выход блока вычисления сдвига частоты 12 соединен со входом генератора 2, первый вход блока вычисления сдвига частоты 12 и третий вход блока быстрого преобразования Фурье 4 объединены и соединены с выходом блока оценки задержки 6, выход которого является третьим выходом устройства, первый и второй выходы блока быстрого преобразования Фурье 4 соединены соответственно с первыми и вторыми входами первого 13 и второго 16 оперативных запоминающих устройств, первый и второй выходы первого запоминающего устройства 13 соединены соответственно с первым и вторым входами второго блока умножения 14, первый и второй выходы второго запоминающего устройства 16 соединены соответственно с первым и вторым входами второго блока комплексного сопряжения 17, первый и второй выходы которого соединены соответственно с третьим и четвертым входами второго блока умножения 14,

Согласно изобретению введены:

первый блок сравнения с порогом 19,

первый блок обнаружения аномальных значений 20,

первый блок вычисления среднего значения 21, формирующий на выходе средние значения оставшихся неаномальных значений разностей фаз комплексных величин корреляции,

первый 22 и второй 23 блоки вычисления модуля,

второй блок сравнения с порогом 24,

второй блок обнаружения аномальных значений 25,

второй блок вычисления среднего значения 26, формирующий на выходе средние значения оставшихся не аномальных значений разностей фаз спектральных составляющих.

При этом (К-1) дополнительных выходов блока оценки задержки 6 соединены с соответствующими им (К-1) входами первого блока сравнения с порогом 19, (К-1) выходов которого соединены с соответствующими им (К-1) первыми входами первого блока обнаружения аномальных значений 20, (К-1) вторые входы которого соединены с соответствующими им (К-1) выходами первого блока вычисления аргумента комплексного числа 11, третий вход первого блока обнаружения аномальных значений 20 и первый вход второго блока обнаружения аномальных значений 25 объединены и соединены с выходом блока оценки задержки 6, первый выход первого блока обнаружения аномальных значений 20 соединен с первым входом первого блока вычисления среднего значения 21, вторые (К-1) входов которого соединены с соответствующими им (К-1) вторыми выходами первого блока обнаружения аномальных значений 20, выход первого блока вычисления среднего значения 21 соединен со вторым входом блока вычисления сдвига частоты 12, первый и второй выходы второго блока умножения 14 соединены соответственно с первым и вторым входами второго блока вычисления аргумента комплексного числа 18, выход которого соединен со вторым входом второго блока обнаружения аномальных значений 25, третий вход второго блока обнаружения аномальных значений 25 соединен с выходом второго блока сравнения с порогом 24, первый и второй входы которого соединены соответственно с выходами первого 22 и второго 23 блоков вычисления модулей, первый и второй входы первого блока вычисления модуля 22 соединены соответственно с первым и вторым выходами первого запоминающего устройства 13, первый и второй входы второго блока вычисления модуля 23 соединены соответственно с первым и вторым выходами второго запоминающего устройства 16, первый и второй выходы второго блока обнаружения аномальных значений 25 соединены соответственно с первым и вторым входами второго блока вычисления среднего значения 26, выход которого соединен с третьим входом блока вычисления сдвига частоты 12.

Блок оценки задержки 6 (фиг.5)